基于AD9361的软件无线电平台设计与实现

姜 浩,张 治

(北京邮电大学泛网无线通信教育部重点实验室,北京100876)

在1992年5月的美国全国电信会议上[1],J.Mitole首次提出软件无线电(SDR),之后便受到广泛的关注和研究,软件无线电的基本思想是数字化在靠近天线的前端进行,所需要的处理都通过高速数字信号处理单元中的软件来实现。然而,在实际应用中,由于其要求极高的软硬件处理能力,因此,直到现在,纯粹的软件无线电概念并没能在实际产品中得到广泛应用。

如今,大多软件无线电平台用离散器件搭建,但离散器件功耗大,系统成本高,需要设计人员有很丰富的硬件设计和射频信号处理经验,另外,对软件方面的要求门槛也很高,并且,随着LTE技术的发展,TD-LTE和FDD-LTE两大通信标准共存,全球所需要支持的频段多达40多个,传统的软件无线电设计方案需要设计不同的硬件平台来支持不同的制式和频段,开发周期长,设计成本高,需要投入大量的人力、物力,给软件无线电的商业化提出了挑战。

然而,随着集成技术的发展,ADI推出的AD9361集成射频捷变收发器为上述问题提供了解决方案,引起了软件无线电领域研究人员的极大关注,被称为SDR应用领域的革命性解决方案[2]。在此背景下,本文提出了一种基于AD9361的软件无线电平台设计方案,并实现了基于此芯片的软件无线电系统平台的研制开发,且对其部分性能进行了测试。实践表明,AD9361捷变收发器在软件无线电领域有着良好的应用前景。

1 AD9361结构与特点

1.1 AD9361 芯片结构

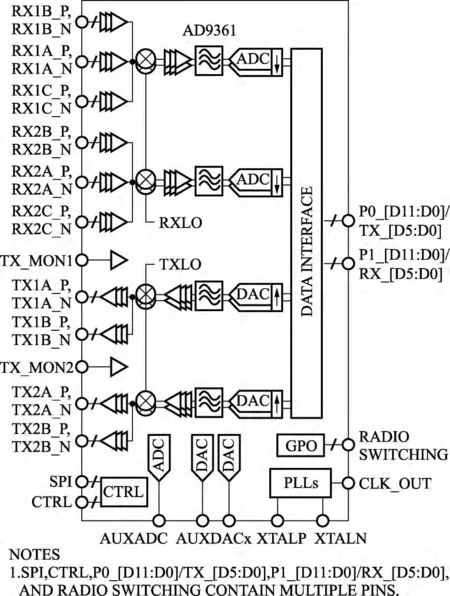

AD9361是ADI公司推出的一款面向3G和4G基站应用的高性能、高集成度的射频捷变收发器,采用10 mm×10 mm、144引脚芯片级球栅阵列封装[3],芯片的内部结构如图1所示。

芯片采用了零中频架构[4],将整个射频以及中频信号电路集成在一个芯片中,包括射频放大器、模拟滤波器、混频器、解调器、12位的ADC和DAC的RF2×2收发器,另外还集成了收发通道的频率合成器,同时为每个接收子系统集成了独立的自动增益控制(AGC)、直流失调校正、正交校正和数字滤波电路[5],消除了数字基带中提供这些功能的必要性,每个通道搭载两个高动态范围ADC,先将收到的I信号和Q信号进行数字化处理,然后将其传过可配置抽取滤波器和128抽头有限脉冲响应(FIR)滤波器[6],以相应的采样率生成12路输出信号。此外,完全集成的锁相环(PLL)可为所有收发通道提供低功耗的N分频频率合成功能,并且芯片集成了频分双工(FDD)系统需要的通道隔离,还集成了VCO和环路滤波器件。

图1 AD9361芯片架构图

1.2 AD9361 性能特点

AD9361的工作频率为70 MHz~6 GHz,涵盖了大部分特许执照和免执照频段,支持可调谐200 kHz~56 MHz的通道带宽,且具有高度的可编程能力,发射器采用了直接变频架构[4],可实现较高的调制精度和较低的噪声,在接收通道,接收噪声系数可以做到小于2.5 dB,此外,该芯片的EVM可以做到小于-40 dB,可为外部功率放大器的选择留出客观的系统裕量,并且,芯片还支持AGC自动增益和更加灵活的手动增益模式,支持外部控制。

2 基于AD9361的软件无线电系统的设计

2.1 软件无线电系统

软件无线电系统的设计如图2所示,该系统射频端采用4片AD9361使单系统支持8×8 MIMO,该系统在一块PXIE Hybrid 8 slots高速背板上搭载了4块数字板,每块数字板上搭载一块AD9361和一块FPGA,背板通过PCIE接口与数字板和主控相连,FPGA与AD9361通过SPI接口完成控制通信。FPGA主要功能是完成时序控制,为AD9361提供数据接口,以及通过PCIE与背板连接于上位机完成交互。

图2 软件无线电系统架构

2.2 SPI接口设计

AD9361与FPGA的接口分为数据接口和控制接口,芯片之间的数据交互通过12 bit的DAC/ADC接口传输,支持6路差分(LVDS)信号和12路单端(CMOS)信号,IQ单路最大采样速率可达61.44 MHz;FPGA对AD9361的控制信息通过PCIE转SPI的控制接口进行传输,FPGA与上位机通过PCIE接口传输信息,配置过程中上位机对射频端的寄存器控制通过PCIE接口写到内存(DDR)中,FPGA通过PCIE转SPI接口传给射频端,射频段完成配置,实现实时的射频参数和工作状态的配置。

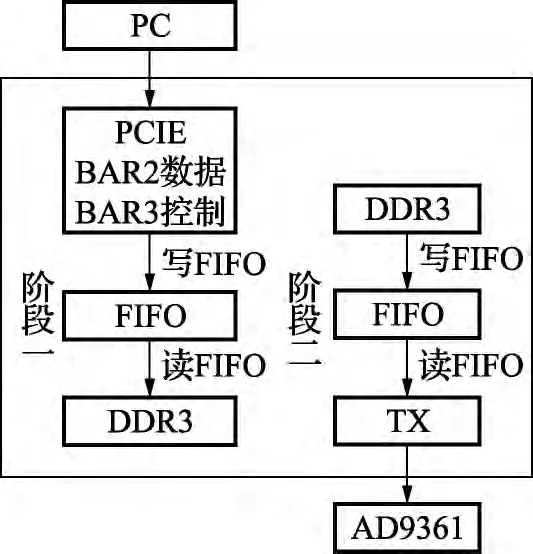

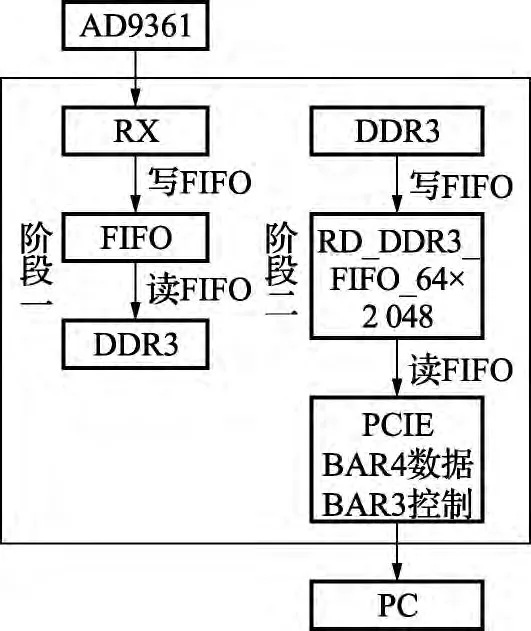

数据的发射过程主要分为两个阶段,如图3所示,第一阶段PC端通过PCIE接口将数据和控制信息写入先进先出(FIFO)队列中[7],再通过读FIFO将数据读到DDR中,第二阶段从DDR中读数据到另一个FIFO中,之后FPGA再从FIFO读数据传给射频段完成发射配置功能,过程中使用了FIFO作为数据的缓冲机制。同样,接收链路也分两个阶段,如图4所示,第一阶段RX模块将接收到的数据通过FIFO机制依次写入DDR中,阶段二上位机通过DMA传输读取DDR中的数据。

图3 数据接口发射过程

2.3 ENSM状态机设计

AD9361收发器包含有使能状态机,允许状态的实时切换,因此,该系统通过使用SPI接口实时更改寄存器值来实现状态的实时切换,系统支持FDD与TDD两种通信模式,可以通过更改寄存器0x013[0]的值来实现两种模式的切换,当0x013值为0时,系统进入TDD模式,值为1时进入FDD模式,两种模式下系统状态切换分别如图5所示,灰色框图表示会自动进入的状态,为了进入WAIT状态,需设置TO_ALERT为0,同样,若要进入 RX、TX或 FDD模式,设置 TO_ALERT为1,而进入睡眠模式需要在WAIT模式前提下,禁用AD9361的时钟和锁相环。在默认状态下,SPI控制是被禁用的,初始化过程中,设置Force Alert State为1,设备强制进入ALERT状态,之后通过配置相应寄存器值使设备进入上述各状态。

图4 数据接口接收过程

图5 TDD与FDD使能状态图

2.4 接口软件设计

首先,基于Linux操作系统较Windows系统有相对简单稳定的系统架构,丰富的开源资源以及更好的实时性[8],可以更好地满足系统平台的要求,降低开发难度,因此该系统软件设计选用基于Linux的开发环境。

接口软件主要实现的功能是完成对AD9361芯片的初始化配置以及实时性的控制,并为用户提供一个简单的控制界面,界面用 QT语言[9]编写,接口软件主要实现的功能有AD9361的初始化,通信模式休眠、FDD、TDD等工作状态的切换,信道带宽、本振频率、采样频率等关键射频参数的配置,RX手动增益控制与AGC自动增益控制的切换,单、双音信号及文件信号的发送。软件界面接口如图6所示。

图6 控制界面(截图)

3 系统测试

3.1 单音波通信试验

首先,对软件控制性能实施测试,通过用户界面对衰减、发射频率、采样频率、带宽等参数进行配置,通过参数返回值以及频谱仪来观察系统的控制情况,结果显示,能正确的对系统进行配置。

之后,对系统进行了单音信号的发送测试,频率为2 MHz的单音信号如图7所示,实验表明单音信号能正常发送。

图7 单音信号(截图)

3.2 QPSK 通信试验

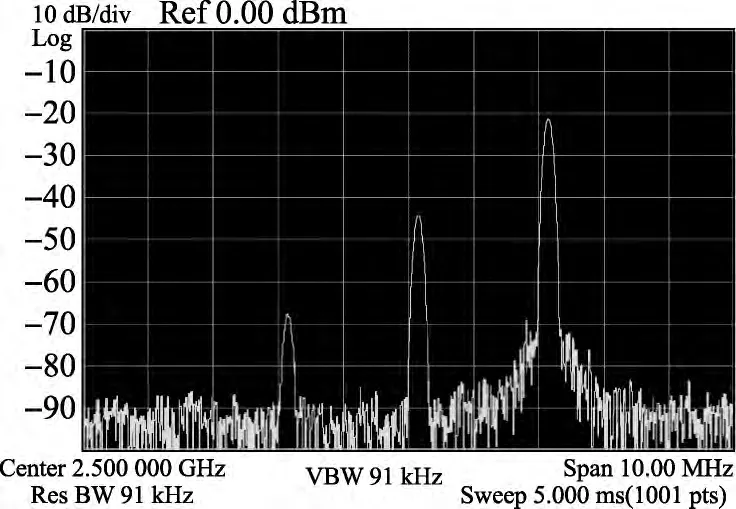

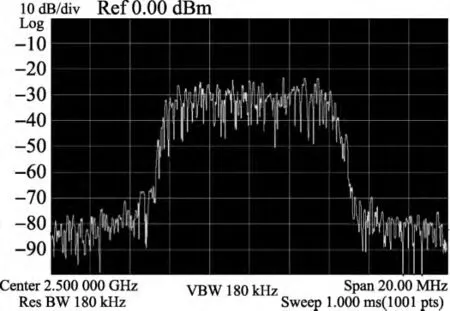

之后,对系统文件发送进行测试,发送已知QPSK数据文件,中心频率为2.5 GHz,通过频谱仪接收数据与MATLAB仿真数据进行对比,大致判断通信效果。图8为MATLAB仿真频谱,图9为实际接收到频谱,综合对比得出QPSK通信成功。

3.3 LTE 通信试验

用系统发送长度为40 ms,采用64QAM调制的LTE-TDD数据,通过频谱仪选件接收数据并对数据进行解调分析,图10为解调结果,通过参数对比,虽然其性能还有待进一步提高,但总体来说验证了LTE通信成功。

图8 MATLAB仿真信号频率(截图)

图9 实际接收频谱(截图)

图10 LTE解调结果(截图)

4 结语

本文详细介绍了基于AD9361的新一代软件无线电平台的结构及实现过程,本系统通过使用AD9361集成收发器代替分立器件射频段搭建,降低了软件无线电系统的开发周期与成本,并对系统的初步性能进行了验证,证明了AD9361捷变收发器在软件无线电领域良好的应用前景,随着系统的进一步开发,本系统性能还有很大的提升空间。

[1]杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010

[2]冯超.ADI推出SDR应用的革命性解决方案——AD9361[EB/OL].[2015-03-28].http://home.eeworld.com.cn,2013.

[3]余莲.AD9361:基于突破性技术 促进软件定义无线电应用[J].电子技术应用,2013(11):1-2.

[4]刘宝玲.电子电路基础[M].北京:高等教育出版社,2013.

[5]高西全,丁玉美.数字信号处理[M].西安:西安电子科技大学出版社,2008.

[6]刘立康,黄力宇,胡力山.微机原理与接口技术[M].北京:电子工业出版社,2010.

[7]王世江.鸟哥的Linux私房菜[M].北京:人民邮电报社,2010.

[8] BLANCHETTE J,SUMMERFIELD M.C++GUI Programming with Qt 4[M].北京:电子工业出版社,2008.

[9]张志涌,杨祖樱.MATLAB教程R2012a[M].北京:北京航空航天大学出版社,2010.