用于SAR ADC中的双通道逐次逼近寄存器的设计与实现

赵 川,唐 宁,翟江辉(桂林电子科技大学,广西 桂林 541004)

用于SAR ADC中的双通道逐次逼近寄存器的设计与实现

赵川,唐宁,翟江辉

(桂林电子科技大学,广西桂林541004)

完成逐次逼近逻辑的逐次逼近寄存器(SAR)在逐次逼近模数转换器(ADC)中的设计相当重要,它控制着整个SAR ADC的正常运行。提出一种新型且结构简单、能在一次AD转换中基于同一组时钟序列信号同时完成两路12bit数据(即24bit数据)信号的逐位逼近转换和存储的无冗余码SAR结构。基于CSMC0.5 μm CMOS工艺采用全原理图输入的方法来实现,最大程度地简化了电路结构和面积,效率高且开关功耗可降到最小。

D触发器;逐次逼近;时钟序列信号;寄存器

0 引言

现代生活中,通常需要将周围环境中的温度、压力、电流等模拟信息采集后以图像的形式立即显示在屏幕上,或者以声音的形式传送,以能更方便地观测和分析,达到智能人机交互的目的,这一过程必定缺少不了将模拟量正确转化为数字量的模数转换器(ADC)。常用的逐次逼近型ADC具有速度高、功耗低且价格便宜的优点[1],可以满足许多便携式、工业、医疗等领域数据采集应用的需求。SAR ADC中SAR控制着转换器的运行,是一个十分重要的子电路,参考文献[2]和参考文献[3]的SAR通过编写Verilog代码经综合工具综合后得到,但对于逐次逼近寄存器,采用该方法进行综合后将会需要调用比较多的D触发器以及门级电路,这将会增大开关功耗[4-5]和电路面积,且通常需要同时处理较多的数据信息,因此将寄存器电路规模优化设计至最简单化、无冗余码、减小面积和功耗具有十分重要的意义。基于此,本文提出一种新型的适用于两路12位ADC的逐次逼近型寄存器结构的实现方法,并对具体电路设计和时序进行详细分析。

1 SAR在ADC中的逐次逼近逻辑

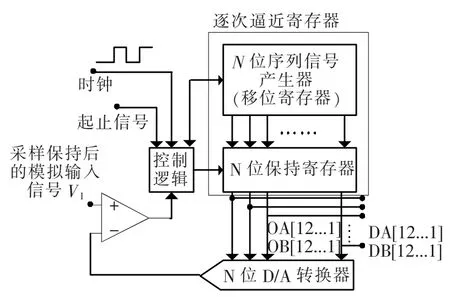

逐次逼近型ADC主要由采样保持放大器(SHA)、模拟比较器、参考数模转换器(DAC)和逐次逼近型寄存器(SAR)构成。如图1所示[6],逐次逼近型ADC是一种使用二进制搜索算法使得DAC的输出逐次逼近输入模拟信号V1的反馈系统,逐次逼近型寄存器SAR控制着转换的运行。

图1 SAR ADC结构框图

SAR控制过程[7-8]:在模数转换开始之前,SAR(由N位移位寄存器和N位保持寄存器构成)被清零,首先采样保持后的模拟输入信号V1输入到比较器的一端,变换过程从数字信号的最高位开始到最低位逐次试探、逼近。在第一个时钟周期,SAR的最高位MSB置“1”,其他各位仍保持为零,N位保持寄存器将输出加载到N位DAC产生相应的模拟信号V0(此刻V0=1/2Vref,Vref为参考电压),如果1/2Vref≤V1,则比较器的输出保持不变,SAR的最高位MSB保存为“1”,否则保存为“0”,至此确定了SAR的最高位。在第二个周期,将“1”送入N位保持寄存器的次高位,如果前一个转换周期确定的MSB=1,那么此时DAC输出3/4Vref,Vin与3/4Vref比较大小,从而确定SAR次高位;如果前一个转换周期确定的MSB=0,那么此时DAC输出1/4Vref,Vin与1/4Vref比较大小,从而确定SAR次高位。依次类推,从高到低位一次逐一进行试探,试探位借助于N位序列信号发生器(移位寄存器)从MSB顺次移向LSB。N位数字信号逐次逼近的过程需要N个时钟周期。判断试探的“1”究竟是保持还是被“0”所取代,由比较器和逐次逼近寄存器逻辑完成,每次逼近动作由时钟信号同步,且每次逼近的结果存留在保持寄存器中。在MSB到LSB各位的试探都结束后,控制逻辑发出一个状态信号,允许数字输出。

2 SAR的设计

本文设计的SAR在同一组时钟序列信号下可同时完成两路数据信号的逐位逼近转换和存储,采用直接原理图输入的方式[9],基于D触发器和非门、与非门、或非门等门级单元电路完成了序列信号产生器和保持寄存器两个部分逻辑电路的设计和仿真验证,采用最少的D触发器,具有更高效的转换效果,以下进行详细分析。

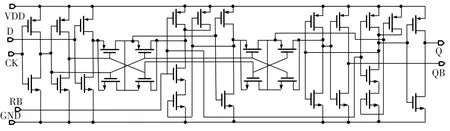

2.1D触发器的设计

本文采用具有低电平异步复位、上升沿触发的D触发器,原理图如图2所示。通过非门、传输门和与非门的逻辑组合形成主、从触发器,再经过主从触发器的级联构成该DFF。其中RB端为复位信号且低电平有效。当RB为0时,将a、b两点维持的信息清零,也将c、d两点维持的信号清零并将低电平送到Q端。RB为1时,当CK=0,传输门TG1打开,D端数据送到主触发器中并保存,当CK=1时传输门TG2打开,保存在主触发器的数据送入从触发器中,最终从Q端输出,至此完成一个时钟信号作用下将D端输入数据送到Q端的功能。当时钟下降沿再次到达时,主触发器才再次接收新数据,而从触发器锁存原来的数据,只有当时钟上升沿再次到达时从触发器才翻转从而输出新的数据。图3为该D触发器的功能仿真结果。图4为该D触发器的晶体管级电路图。

图3 D触发器的功能仿真

图4 D触发器原理图

2.212bits序列信号产生器的设计及仿真

移位寄存器是指寄存器里存储的代码能在移位脉冲的作用下依次左移或右移。如图5所示,本文采用17个D触发器(DFF)组成一个移位寄存器,其中第一个DFF的输入端接收输入信号CON,其余的每个触发器输入端均与前边一个DFF的Q端相连。采用或非门和与门等门电路进行逻辑组合,实现对移位寄存器产生的序列信号进行时序控制,确保每个转换周期的准确运行。

信号POR作为所有DFF清零端RB的输入信号,低电平有效。在SAR没开始工作前,POR为低电平,所有DFF都被清零,则TT和C0~C15都为低电平“0”,TT和C0~C1通过或非门产生的T1~T4为高电平“1”,T1~T4通过与门进而使CON为“1”,这为转换开始后TT和C0~C15能够产生上升沿跳变做好了准备。TT在SARADC中接入到采样保持模块,控制采样模拟信号的开始。当POR变为高电平时,SAR开始工作,所有DFF可正常存储数据,时钟信号clk的第一个上升沿到达后,C0=Q0=D0=CON=1,TT=Q1=D1=0,C1=Q2=D2=0,……,如此类推,其余DFF的输出Q也跟随输入端D的状态变化,都为0,同时由于C0的改变,导致CON也改变为0。第二个clk上升沿到达后,C0=Q0=D0=CON=0,TT=Q1=D1=1,C1=Q2=D2=0,……,在随后的clk上升沿到来时,移位寄存器都做同样的动作,产生一系列上升沿信号,其中的12个上升沿信号C2~C13作为12bit保持寄存器的序列时钟输入信号。时序仿真结果如图6所示。

图5 序列信号产生器

图6 序列信号产生器仿真波形

2.312bit保持寄存器的设计及仿真

用24个DFF和或非门组成保持寄存器,可实现在序列产生器产生的时钟信号下完成两路12bit数据的存储,电路结构如图7所示。两路转换的时钟信号是相同的,它们同时动作,两路的工作机制相同。

保持寄存器两路的输入输出分别为DTA、DTB和DA[12…1]、OA[12…1]、DB[12…1]、OB[12…1],其中OA[12…1]和OB[12…1]为加载到12bit DAC的12bit数字码,产生相应的模拟信号V0,最高位MSB为OA[12]和OB[12]。DTA、DTB为V0和模拟输入信号V1通过比较器比较后输出的结果“0”或“1”。由图3和图4可知,CONAB在C0上升沿到达之后、C15上升沿到达之前都是低电平0,这样设计可以保证CONAB输入或非门后,其输出由另一个输入端口的输入状态决定。C2上升沿没到来之前,DFF还没有动作,故DA[12…1]=000…0,DB[12…1]=000…0,C1先产生上升沿由“0”跳变为“1”,则OA[12]=OB[12]=1,且OA[11…1]=OB[11…1]=[000…0]。接着C2上升沿到达,处理MSB的DFF输出端DA[12]被置成此刻对应的输入数据DTA(OA[12…1]=OB[12…1]=[100…0],加载到DAC后输出V0与V1比较的输出结果),此时C1已变为“0”,OA[12]由DA[12]决定。若此刻DA[12]=“1”,则OA[12]保留为“1”,若DA[12]=“0”,则OA[12]用“0”取代原来的“1”,同时因为C2为“1”,使得OA[11]=OB[11]=“1”,新得到OA[12…1]=OB[12…1]=[X100…0]加到DAC转换器的输入端上,以便下一次的逼近比较。随后的C3~C13分别跳变的瞬间,保持寄存器都作同样的动作,依次完成从次高位到最低位的逐一比较。

C2~C13只有一次上升沿,故数码寄存器可将输入数据DTA锁存,直到C15跳变,控制CONA的DFF清零端RB为低电平输入,导致CONAB跟着变为“1”,OA[12…1]=000…0,12个数位都比较结束,输出模数转换的最终结果为12bit串行数据DA[12…1]和DB[12…1]。因为移位寄存器的时钟输入信号由clk和C15通过“或”逻辑来决定,当C15变为高电平后,移位寄存器的时钟信号将不再满足上升沿触发的条件,直到来一个低电平POR将所有DFF清零才使C15=0。图8为一次转换的仿真结果(图(b)紧接着图(a)右边),可以看出当CONAB变为高电平后,所有寄存器清零,OA[12…1]=OB[12…1]=[000…0],为下一次AD转换做好准备,同时输出最终数据DA[12…1]和DB[12…1],并锁存。

图7 保持寄存器

3 版图设计及在SAR ADC中的验证

基于CSMC 0.5μm DPTM工艺,采用手工布局布线的方式代替参考文献[10]中的EDA自动布局布方式,实现SAR版图如图9所示,整体优化到最紧凑,很好地节省了版图面积,降低了成本,面积约为290μm×110μm。

图8 保持寄存器仿真结果

图9 逐次逼近寄存器版图

将本文设计的SAR接入到SAR ADC整体电路中,输入两路模拟信号进行仿真,A路输入模拟信号2.505V,B路输入模拟信号2.635V,5V单电源供电,得到仿真结果如图10所示。由结果可知,TT上升沿到达时,A路B路开始采样保持,A路为2.5 050 326V,B路为2.6 352 034V,输出AD转换的最终数字信号DA[12…1]=[100000000101],DB[12…1]=[100001101111],将这两个数字量转换后分别为2.5 061 035V和2.6 354 980V,都满足误差要求,表明所设计的SAR能够准确实现逐次逼近比较的功能。

4 结论

根据SAR ADC的工作机理,采用全定制设计方法设计了一个可同时完成两路12bit数据信号的逐位逼近寄存器,仿真验证结果表明,该SAR满足SAR ADC正常运转所需要的时序要求,并解决了采用逻辑综合设计方法带来的电路单元冗杂、功耗大、开关噪声大和电路面积大等问题;通过Cadence软件完成原理图和版图的设计,将其应用到SAR ADC的整体电路中进行仿真,结果表明设计达到要求。该设计在需要同时处理多位数据的模数转换应用中具有重要的实际应用价值。

[1]孙彤,李冬梅.逐次逼近A/C转换器综述[J].微电子学,2007,37(4):523-547.

[2]王俊博.基于CMOS工艺10位模数转换电路的设计[D].哈尔滨:黑龙江大学,2010.

[3]周文婷.数字CMOS工艺下10位580kSps逐次逼近型模数转换器设计[D].上海:上海交通大学,2010.

[4]Ye Yafei,Liu Liyuan,Li Fule,et al.An 8-bit 1MHz successive approximation register(SAR)A/D with 7.98ENOB[J].Anti-Counterfeiting,Security and Identification(ASID),IEEE International Conference,2011:139-142.

[5]张少真,李哲英.应用于SAR ADC中逐次逼近寄存器的设计[J].北京联合大学学报(自然科学版),2011,25(2):15-19.

[6]张红,高炜祺,张正璠,等.一种基于新型寄存器结构的逐次逼近A/D转换器[J].微电子学,2006,36(3):337-343.

[7]李伟华.VLSI设计基础[M].北京:电子工业出版社,2010.

[8]阎石.数字电子技术基础[M].北京:高等教育出版社,2006.

[9]小林芳直.数字逻辑电路的ASIC设计[M].蒋民,译.北京:科学出版社,2004.

[10]孙磊.一种低功耗逐次逼近型模数转换器的研究与设计[D].上海:上海交通大学,2010.

Design of a two-channel SAR registers in SAR ADC

Zhao Chuan,Tang Ning,Zhai Jianghui

(Guilin University of Electronic Technology,Guilin 541004,China)

The design of successive approximation registers(SAR)which completes successive approximation logic in SAR Analog-Digital Conversion is very important,and it controls the SAR ADC′s normal running.A new and simple SAR is proposed in this paper,which can complete two-way 12 bit data signals(that is 24 bit data signals)successive approximation conversion and storage based on the same sequence of clock signal in one AD conversion.Based on CSMC 0.5 μm CMOS technology and use the schematic diagram input method to realize,which can maximum simplify the circuit structure and area,have high efficiency and minimize the switch power consumption.

DFF;successive approximation;clock sequence signal;register

TN432

A

1674-7720(2015)10-0025-04

2014-12-20)

赵川(1989-),女,硕士研究生.,主要研究方向:专用集成电路设计与应用。

唐宁(1964-),男,硕士,副教授,主要研究方向:专用集成电路设计与应用。

翟江辉(1981-),男,硕士,讲师,主要研究方向:专用集成电路设计与应用。