基于I2C接口EEPROM读写控制器设计

杨 帆(贵州大学 大数据与信息工程学院,贵州 贵阳 550025)

基于I2C接口EEPROM读写控制器设计

杨帆

(贵州大学大数据与信息工程学院,贵州贵阳550025)

简单介绍I2C总线协议,用Altera公司的FPGA(现场可编程门阵列)芯片设计I2C总线接口控制器,用于控制EEPROM(带电可擦写可编程只读存储器)的读写操作。

I2C总线;FPGA;EEPROM

0 引言

随着电子技术快速发展,有许多的IC需要相互之间进行通信。为此,Philips公司开发了一种性能优越的双向两线串行总线I2C(Inter-Integrated Circuit)总线。进行FPGA设计时经常需要与外围提供I2C接口的芯片进行通信,虽然市场上有专门的I2C总线接口芯片,但是大多性能指标固定、功能单一、使用不方便。根据I2C总线协议和其电路的电气特性,在Altera公司的EP4CE10F17C8N型号的FPGA芯片上可以方便地实现I2C总线接口,进而实现EEPROM的读写操作。

1 I2C总线原理概述

I2C总线有两条串行总线,一条是串行时钟线(SCL),一条是串行数据线(SDA),连接到总线上的每个器件既可以作为发送器又可以作为接收器,且每个器件都有唯一的地址识别。主机主要负责产生时钟、初始化发送和终止发送等操作。从机则是被主机寻址的器件。典型的连接在I2C总线上的器件有LCD、EEPROM等。总线的启动信号条件是当SCL为高电平时,SDA由高变为低;停止条件是当SCL为高电平时,SDA电平由低变高。数据的变化只能发生在SCL为低电平期间[1]。

2 EEPROM读写控制器模块的设计与实现

在进行数据传输时,读写控制器首先产生一个启动信号(当SCL为高电平时,SDA由高变为低),接着发送控制字(即I2C总线器件的特征编码和3bit EEPROM的芯片地址)以及写状态R/W位为0到总线上。这里的总线器件特征码为1010,而3bit EEPROM的芯片地址为000。接着主控制器释放总线,等待EEPROM发出的应答信号,由于采用的EEPROM型号是24LC64,因此在控制器收到应答后,将首先发送EEPROM高字节的存储单元地址,当控制器再次收到应答后继续发送EEPROM低字节的存储单元地址,当控制器再次收到应答后,判断是读还是写,如果是写操作,则控制器发送数据字节,并把数据写入被寻址的存储单元,EEPROM再次发送应答信号,读写控制器收到应答信号后,产生停止信号。如果之前判断出是读操作,则控制器会在收到应答后产生一个重复起始条件,紧接着写入读控制字10100001,这里的最后一位1表示读操作,前面的1010000和之前说的一样,是器件特征编码1010和3bit EEPROM芯片地址000。当控制器再次收到应答后会产生一个释放总线的动作,把总线留给EEPROM,控制器负责接收EEPROM发出的数据。当控制器接收完数据后会占用总线,并发出一个非应答信号,表示数据收到,最后控制器再产生停止信号,停止本次传输。模块的主状态机如图1所示。

图1 读写控制器主状态机

这里写入的地址是2B的地址,且分两次写,因为此EEPROM的地址是16bit的。

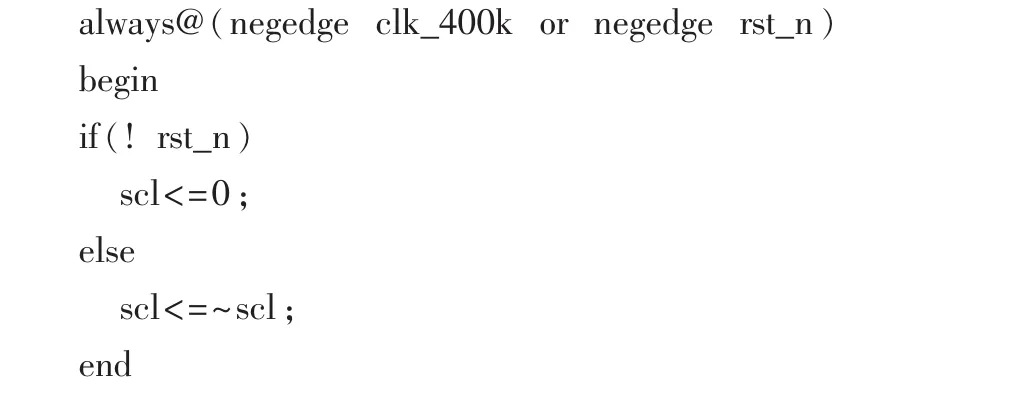

2.1控制器的总线时钟SCL产生

由于FPGA开发板的时钟是50MHz,这里先将输入的50MHz时钟进行分频产生400kHz时钟,利用400kHz的时钟去产生总线时钟SCL。具体方法是:在400kHz时钟的下降沿对SCL进行翻转操作,这样能很好地实现I2C总线时序要求。这里生成的SCL是200kHz时钟。其Verilog代码如下:

时序图如图2所示。

图2 读写控制器时序图

由图2可知,在SCL为高电平时,SDA由高变低会产生一个开始信号,而在SCL为高电平时,SDA由低变高会产生一个停止信号,而数据的改变只能在SCL为低电平期间发生,在SCL为高电平时,数据要保持稳定。数据采样时使用400kHz时钟的上升沿采样,并且是在SCL为高电平时才能采数据,因为这时的数据稳定。

2.2I2C总线数据输入输出

电路的输出采用三态数据通路设计,如图3所示。

图3 三态数据通路结构

其Verilog代码如下:

由图3可知,sda的I/O类型为 inout,当开关link_sda为1时,读写控制器上的数据可以发送到sda上,实现控制器占用总线进行写操作,当link_sda为0时,输出为高阻态,而此时外部的sda上的数据可以读进来,实现了控制器释放总线,将总线交由从机EEPROM,进而可将EEPROM发出的数据读进来[2]。

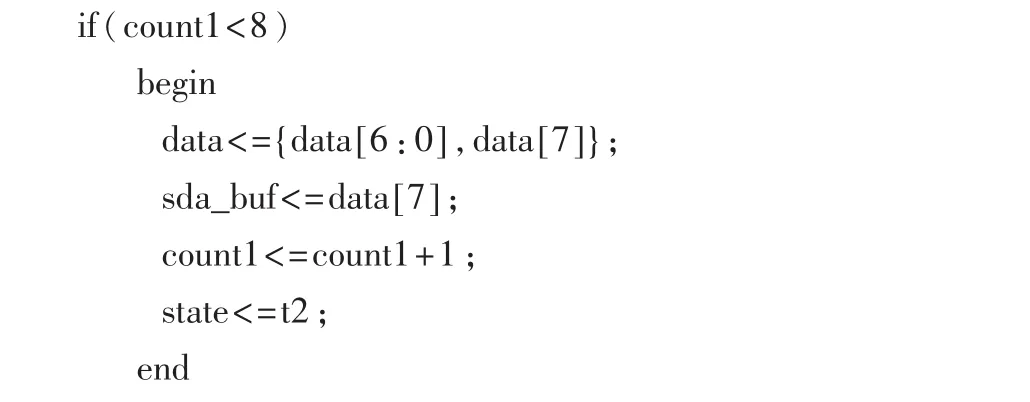

数据的输出涉及并串转换,因为数据寄存器中的数据是8bit,而I2C总线上传输的数据sda为1bit,其Verilog代码如下:

设计采用循环移位的方式将8bit的并行data数据一位一位地移到sda_buf线上送出去。

相反,I2C总线数据的输入涉及串转并操作,Verilog代码如下:

3 仿真验证

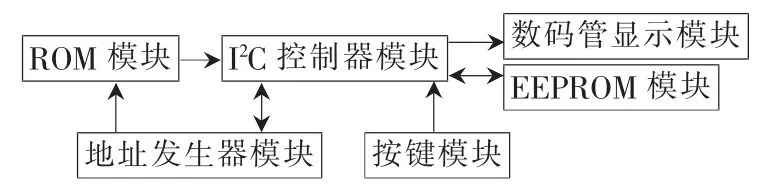

仿真平台的搭建如图4所示。

图4 EEPROM读写控制器验证电路框图

由图4可知,电路的仿真验证模块分为I2C接口控制器模块、ROM模块、地址发生器模块、按键模块、EEPROM模块和数码管显示模块。其中,按键模块用于产生I2C接口控制器的读写操作信号;地址发生器模块用于产生ROM和I2C接口控制器的地址信息;ROM模块中事先存储了一定量的数据,并将这些数据发送给I2C接口控制器,用来写入EEPROM;I2C接口控制器负责EEPROM的读写操作;数码管显示模块负责将读写控制器从EEPROM中读出的数据显示出来,用来查看数据是否正确。

电路的仿真波形如图5、图6所示。

图5 控制器写EEPROM

图6 控制器读EEPROM

由图5可知,在写EEPROM操作时,读写控制器在开始信号后首先写入1B的控制字10100000(前面的1010是器件特征码,000表示EEPROM的芯片地址,最后一位0表示写操作),紧接着控制器释放总线,等待EEPROM给它的应答。因为仿真只是模拟,并没有接入EEPROM,所以应答位呈现高阻态。在应答的后面就是高字节的地址,等到再次收到应答信号时,控制器继续发送低字节的地址位。这里的地址为0000_0000_0000_0000,共2B,等再次收到应答信号时,控制器会发送单字节的数据0000_0001,将其写入相应的存储空间上。收到来自EEPROM的应答后,控制器产生停止信号,结束操作。图6是控制器读EEPROM操作,它与写操作不同的是在写入控制字和高低字节地址后,控制器会产生新的启动信号,紧接着写入1010_0001,最后的1表示是读操作,这时控制器会释放总线,等收到应答后继续释放总线,以读取EEPROM中的数据;1B的数据收完后,控制器产生一个非应答信号并紧接着产生停止信号,表示读数据任务结束。

4 结论

利用I2C总线协议设计出EEPROM读写控制器,与专用的I2C接口芯片相比,有配置灵活、使用方便、可移植性强的特点,除了满足EEPROM的读写操作,还可满足其他I2C总线器件的读写要求。电路仿真完成后,在FPGA上成功实现EEPROM的读写操作,通信正常,满足要求。

[1]Philips Semiconductors.The I2C-bus Specification Version 2.1[Z].2000.

[2]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2013.

图5 系统验证测试平台

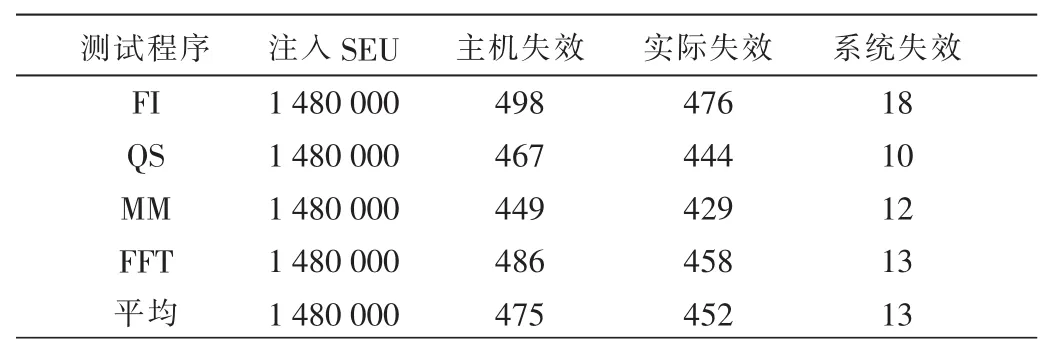

运行时指令SRAM和数据DPRAM会同时发生故障,导致主机失效。本文选用4种程序进行试验,分别为递归(Fibonacci,FI)、快速排序(Quick Sort,QS)、矩阵乘(Matrix Multiplication,MM)和快速傅里叶变换(Fast FourierTransform,FFT)。同时向 指令 SRAM和数据DPRAM中注入1 480 000次故障,主机平均会有475次失效,在这些失效中平均会有452次被检测到并处理,其可靠性相对不加EDAC时显著提高。

表1 SRAM与DPRAM同时注入故障数据(次)

5 结论

本文研究了EDAC的主要原理和实现,针对ARINC 659总线控制器的体系结构与特点,将[40,32]EDAC模块嵌入数据DPRAM和指令SRAM中,用来纠正1bit错位和检验2bit错误。该设计嵌入在FPGA中,与传统的利用纠错芯片硬件电路相比,简化了电路,能快速地实现ARINC 659总线控制器的纠错检错,有效降低了单粒子翻转效应对存储器的影响,提升系统的整体性能。

参考文献

[1]付剑.星载计算机的硬件容错设计与可靠性分析[D].长沙:国防科技大学,2009.

[2]张喜民,魏婷.ARINC659容错数据总线测试验证系统研制[J].西安电子科技大学学报(自然科学版),2011,38(6):140-145.

[3]刘淑芬.崔星.计算机RAM检错纠错电路的设计与实现[J].航天控制,2003(4):59-67.

[4]贾文涛,张春元,付剑,等.一种高可靠双机备份星载计算机的设计与实现[C].第六届中国测试会议,2010.7.

(收稿日期:2014-12-24)

作者简介:

丁志平(1990-),男,硕士研究生,主要研究方向:嵌入式系统设计与应用。

Based on the I2C interface EEPROM read and write controller design

Yang Fan

(College of Big Data and Information Engineering,Guizhou University,Guiyang 550025,China)

The Inter-Integrated Circuit(I2C)bus protocol is introduced briefly.Using Field-Programmable Gate Array(FPGA)chip of Altera Company to design I2C bus interface controller to control Electrically Erasable Programmable Read-Only Memory(EEPROM)read and write operations.

I2C bus;FPGA;EEPROM

TN495

A

1674-7720(2015)10-0022-03

2014-12-25)

杨帆(1987-),通信作者,男,硕士研究生,主要研究方向:微电子科学与工程。E-mail:yangfan2010@yeah.net。