H.264高清视频编码器的设计与实现*

李 飞,卿粼波,滕奇志,何小海(四川大学 电子信息学院,四川 成都 610065)

H.264高清视频编码器的设计与实现*

李飞,卿粼波,滕奇志,何小海

(四川大学 电子信息学院,四川 成都 610065)

针对高清视频庞大的数据量以及H.264编码器复杂的编码结构引起的低编码速率的问题,对影响算法编码速率的原因进行了深入分析,并设计了高效的多核并行方案,进而充分利用TMS320C6678的多核性能,并结合TMS320C6678的运算存储特性,对H.264编码器进行了多方面的优化,最终使H.264编码器对720P高清视频序列编码速率从1.2 fps增加到27.2 fps,更加贴近于实际应用。

H.264编码器;TMS320C6678;高清视频

0 引言

H.264标准吸取以往标准中的优点,编码效率与 H.263+以及MPEG-4 SP相比最多可节省50%的码率,存储需求大大降低。正是由于H.264强大的功能及其巨大的市场潜力,国内外不少公司开始对H.264的编解码应用进行研究并有产品纷纷面世。目前国内也纷纷对H.264标准进行研究,使用专用H.264编解码芯片推出了许多产品。编码芯片速度很快,但是性能固定,无法根据需求进行性能的改进,另一方面新一代的HEVC编码算法性能更为优越,但是由于其技术应用尚不成熟,H.264仍然拥有巨大的应用潜力,因而在DSP上实现H.264编码器具有重大意义。

1 H.264复杂度分析

H.264标准相比于以往压缩标准有以下主要优点[1]:

(1)在相同重建图像质量下,H.264相比H.263+和 MPEG-4节约50%的码率;

(2)H.264具有较强的抗误码能力,可以在恶劣的无线环境中运用;

(3)H.264采用简洁的分层模式,具有更友好的特性。

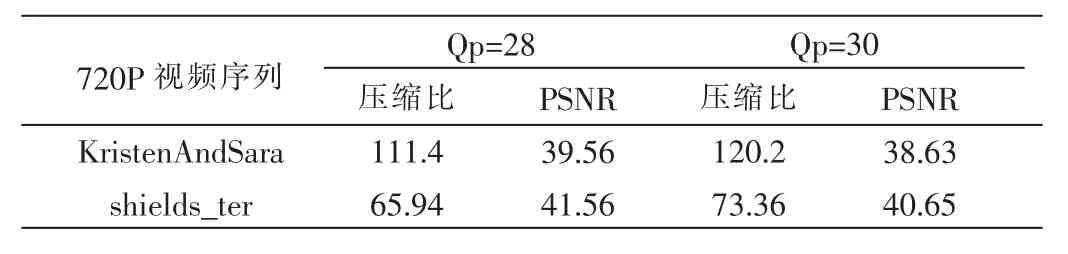

本文采用H.264编码器的可靠性能测试结果如表1所示。

表1 编码工程性能测试结果

为了对编码器进行更具针对性的优化,本文对编码器内部主要算法部分进行了时间统计,结果如图1所示。

2 编码器在DSP上的实现

2.1DSP的多核并行处理方案

为了充分发挥TMS320C6678的性能,需要设计一个高效的多核并行处理方案[2]。核间通信(IPC)的方式一般有两种:MessageQ消息机制和Notify中断机制。其中中断机制是一种不可屏蔽的中断通信机制,通信快速便捷,因而本文采用Notify中断方式进行核间通信。多核之间实现可靠通信后,就需要为8个核的并行运算设计一种高效的拓扑结构,通常有Data-Flow模式和 Master-Slave模式两种常用的核间通信拓扑结构。

图1 帧内、帧间编码时间比例

(1)Data-Flow模式:通信控制逻辑简单,适合单向通信,多核利用率不稳定,取决于各个核流水工作量均衡度,适用于能将算法分成多个独立的相等工作量任务的情况。

(2)Master-Slave模式:通信控制逻辑相对复杂,多核利用率较高,程序开发相对简单[3]。

根据图 1中时间测试可知,H.264编码器中各任务工作时间很不均衡,因此本文采用Master-Slave模式。

2.2多核算法流程

在Master-Slave模式下,核 0充当逻辑控制器及数据流收发器,其他核则专于压缩算法处理。当核0接收到视频帧时,将720P视频帧尽可能均匀地分成7个视频片分配到各核的接收缓冲区中,核1~5的视频片为106×1 280,核6~7的视频片为90×1 280,各核在编码完后将数据流存放在发送缓冲区中。为充分利用、提高多核并行效率,本文为每个运算核提供了两组数据缓冲区,形成一个乒乓缓冲存储结构,用以节约运算核对核0的等待时间,使各个核运算基本保持全速运行状态,从而充分地利用多核并行处理能力。

3 H.264编码器的DSP优化

编码器在DSP上的优化依据是基于 DSP硬件结构上的特有操作,分为传输与运算两种操作。传输优化是DSP核、EDMA控制器等主动模块对不同存储类型访问性能优化配置过程。本文采用的传输方面优化有缓存优化、EDMA优化、数据存储优化;在运算方面主要是针对C66x核的单指令多数据操作(SIMD)以及并行操作特性,在编译器、C语言以及汇编语言层面上对编码器进行优化。

3.1缓存(Cache)优化

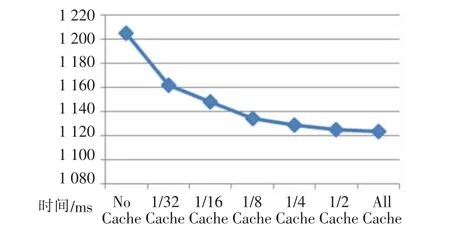

C6678拥有两级缓存结构,SYS/BIOS默认将一级数据存储(L1D)32 KB、一级程序存储(L1P)32 KB全部设置为缓存,而本地二级存储(LL2)则默认全部为普通存储,可用于存放一些关键数据。图2是在一级缓存为 32 KB大小的情况下通过测试得到二级存储不同缓存化程度与平均编码时间的关系图[4]。

图2 二级缓存配置与编码时间优化关系图

由图2可以看出,当二级缓存大小超过 1/8Cache程度时,编码时间基本保持不变。考虑到资源宝贵,LL2用来存放一些高速运行的算法数据会表现出更好的性能,本文将二级缓存设置为1/8Cache模式。

3.2数据存储优化

数据存储优化是根据 C6678对不同存储资源访问的不同速度而确定数据分配,表2是DSP多核共享访问DDR3和SL2的实验统计对比。

表2 DSP共享访问SL2SRAM、DDR3(单位:MB/s)

编码过程中,全局变量所在的数据段为 bss,动态开辟的空间、临时变量以及中间保存结果所在的数据段为stack,还有全局数组所在的段为 far,这部分访问频繁的数据则放在LL2上;其他访问较少的段,如text、sysmem、cio则统一放在DDR3上。

3.3EDMA优化

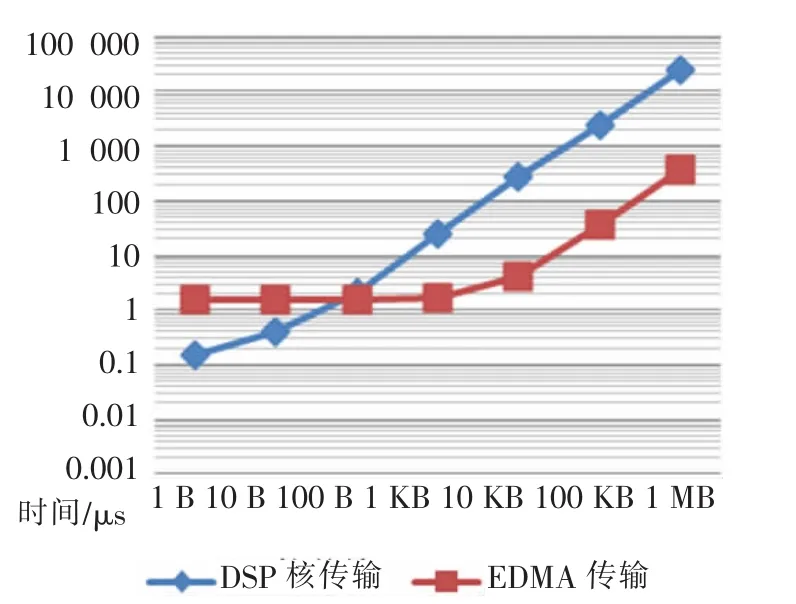

TMS320C6678共有 3个 EDMA管理器,10个通道。本文待压缩视频序列为 720P,YUV420格式,一幅图像的大小为 1.32 MB,在任务分配过程中需要对图像进行拷贝。对于这种大数据量的复制过程,EDMA比通过DSP核进行复制具有相当大的优势,并且 EDMA还可以完成非连续数据段的复制[5]。EDMA和 DSP核的复制性能与复制数据量的关系测试对比如图3所示。

图3 DSP、EDMA传输对比

3.4汇编优化

汇编优化是一种运算型的优化,通过充分利用C66x核的SIMD特性以及运算单元并行特性,从而减少运算过程中所消耗的时间[6]。

根据图1中所示,编码时间主要集中在预测、运动估计、DCT、量化等部分,选择各部分算法中的关键函数进行汇编优化[7],优化结果如表 3所示。

表3 核心运算函数汇编优化表

3.5其他优化

除上述 4种基于 TMS320C6678特性的独特优化,还可以进行一些DSP中常用的普适优化,这里只做简单描述。

(1)-O优化:-O优化是编译器对代码优化的级别,其中-O2深度优化速度和减少代码体积,一般为推荐等级,故本文选择-O2优化级别。

(2)去双重循环优化:在文件级优化的过程中,编译器对于单重循环可以进行 Pipeline优化,当遇到双重循环时,通过解开一层循环,优化效率会得到很大提升[8]。

(3)内联函数优化:内联函数在调用处直接插入,而不是调用,因而可以省略掉函数的调用开销,适合对频繁调用的简单函数如T264_sad_u_c()等进行优化。

4 测试结果

4.1测试环境

本文编码器测试环境如下:调试软件环境CCS5.2.1,测试用到的DSP硬件平台为TMS320C6678,编码算法为 H.264,量化参数 Qp=30,编码结构GOP为I帧:P帧=1:5,测试视频序列为官方 KristenAndSara.yuv、shields_ter.yuv两个序列,分辨率为720P,为更方便准确地计算平均编码速率,测试帧数设定为300帧。

4.2测试结果

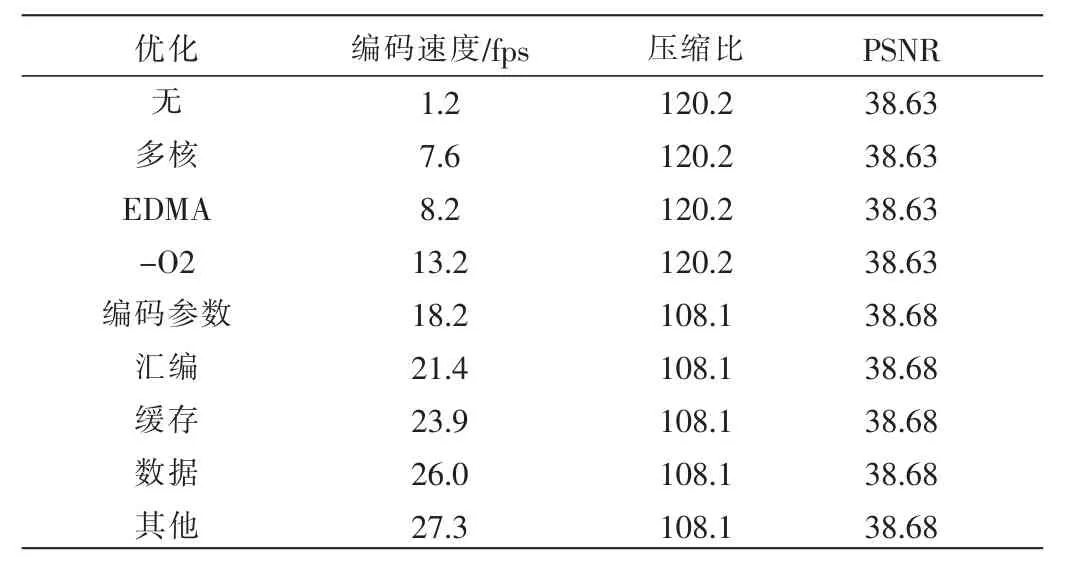

以 KristenAndSara.yuv的测试为记录,编码器在优化过程中的各项指标整体记录如表4所示。

由表4可以看出,表中一系列优化以后,编码图像质量并没有什么影响,编码速度得到了极大的提升,其中多核优化的作用非常明显,说明本文的多核结构效率是很高的。

表4 整体优化效果表

5 结论

H.264具有相当优越的压缩性能,面对其运算复杂性与庞大运算量的难题,本文结合硬件特点,对编码器进行一系列优化,从而使编码器实现对高清视频序列实时编码。目前对DSP编码器的研究很热,本文提供的C6678多核方案、基于 C6678硬件特点的优化以及720P实时高清视频H.264编码器都是很有意义的。

[1]梁佩珊.H.264编码器算法优化与设计[D].杭州:浙江大学,2006.

[2]曹折波,李青.多核处理器并行编程模型的研究与设计[J].计算机工程与设计,2010,31(13):2999-3002.

[3]吴灏,肖吉阳,范红旗,等.TMS320C6678多核 DSP的核间通信方法[J].电子技术应用,2012,38(9):2-3.

[4]王熹微,唐昆,崔慧娟.基于DM642的视频编码 Cache优化策略[J].微计算机信息,2005,21(09Z):84-86.

[5]PESCADOR F,MATURANA G,GARRIDO M J,et al.An H.264 video decoder based on a latest generation DSP[J].IEEE Transactions on Consumer Electronics,2009,55(1):205-212.

[6]郑回青,林嘉宇,张镔.基于TMS320C64xDSP的汇编优化方法[J].微处理机,2010,31(1):105-108.

[7]黄国玉,廖湘柏.基于DM642的x264源代码的汇编优化[J].南华大学学报(自然科学版),2014,28(1):74-76.

[8]Su Bogong,Wang Jian,ESGUERRA A.Source-level loop optimization for DSP code generation[C].1999 IEEE International Conference on Acoustics,Speech,and Signal Processing,1999.Proceedings.1999,4:2155-2158.

Designation and im plementation of H.264 encoder for HD video

Li Fei,Qing Linbo,Teng Qizhi,He Xiaohai

(College of Electronics and Information Engineering,Sichuan University,Chengdu 610065,China)

For the problem of low coding speed caused by HD video huge amount of data,as well as the H.264 encoder′s complex coding structure,in-depth analysis of the causes which influenced the speed of coding algorithms was put into realization in this article.On one hand,an efficient multi-core parallel solution was designed to take full advantage of the multi-core performance of TMS320C6678.On the other hand,according to the TMS320C6678′s computing and storage characteristics,many methods were made to optimize the H.264 encoder′s coding efficiency in many aspects.Eventually the 720P HD videos H.264 encoder′s coding speed was improved from 1.2 fps to 27.2 fps,which was more suitable for practical applications.

H.264 encoder;TMS320C6678;HD video

TP37

A

1674-7720(2015)06-0042-03

2014-10-28)

李飞(1990-),通信作者,男,硕士,主要研究方向:DSP、多媒体处理。E-mail:910002483@qq.com。

卿粼波(1982-),男,博士,副教授,主要研究方向:图像处理、数字通信。

滕奇志(1961-),女,博士,教授,主要研究方向:图像处理与模式识别。

国家自然基金项目( 61471248 )