基于Multisim行扫描AFC锁相环电路仿真设计

李宏恩

(长治医学院 生物医学工程系,山西 长治 046000)

基于Multisim行扫描AFC锁相环电路仿真设计

李宏恩

(长治医学院 生物医学工程系,山西 长治 046000)

锁相环电路具有良好的相位误差控制功能,可实现电路输入信号与输出信号频率之间的同步。基于设计一种行扫描锁相环电路,采用EDA仿真软件Multisim2001,利用Multisim强大的电路设计和仿真功能,完成对锁相环电路的设计。仿真结果表明,所设计电路实现了对相位的锁定功能,同时依托multisim灵活简便的仿真环境,还可通过改变元件参数,并结合观察各点波形的变化,而找到电路的最佳锁相范围数据,为PCB设计与制作节省了设计成本。

Multisim2001;行扫描;锁相环;AFC

Multisim软件由加拿大IIT公司开发,可适用于各类模拟或数字电路的设计工作,并具有丰富的仿真分析能力[1-2]。锁相环电路广泛应用,包括于通讯、雷达、电视、红外、计算机等众多领域,所以电路能否实现“锁相”功能对于设备正常工作影响较大。本次设计是在常规锁相环电路的基础上加入行扫描AFC(AFC)方法,利用Multisim进行设计与仿真,通过调整元件参数,完成了对行AFC锁相环电路的设计。

1 电路的结构、工作原理及AFC

1.1 锁相环电路的结构

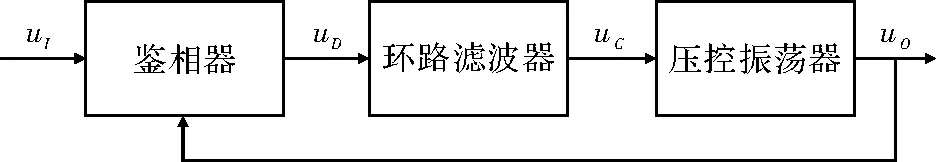

锁相环最基本的结构如图1所示。其由3个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)[3-5],各部分的功能如图1所示。

图1 锁相环结构

在PLL中,PD是一个相位比较器,比较基准信号uI与输出信号uO之间的相位偏差φ,并由此产生误差信号uD;LF是一个低通滤波器,用于滤除uD中的高频成分,起滤波平滑作用,以保证环路稳定和改善环路跟踪性能,最终输出控制电压uC;VCO是一个电压/频率变换装置,产生本地振荡频率,其振荡频率受uC控制,产生频率偏移,从而跟踪输入信号的频率。

1.2 锁相环电路的工作原理

锁相环是一种相位误差控制系统。通过比较输入信号和压控振荡器输出信号之间的相位差,从而产生误差控制电压来调整压控振荡器的频率,以达到与输入信号同频。

假设环路开始工作时的压控振荡器频率与输入信号频率不同,则由于两信号之间存在固有的频率差,其间的相位差势必始终在变化,导致鉴相器输出的误差电压就在一定范围内变化。在这种误差电压的控制下,压控振荡器的频率随之变化。当压控振荡器的频率逐渐变化到与输入信号频率相等时,因此时已满足稳定性条件,所以压控振荡器的频率将不再变化。同时,输入信号和压控振荡器输出信号之间的频率差变为零,相位差不再随时间变化,误差电压也固定下来,此时环路相当于进入“锁定”状态,故称为“锁相环”。

1.3 行扫描AFC

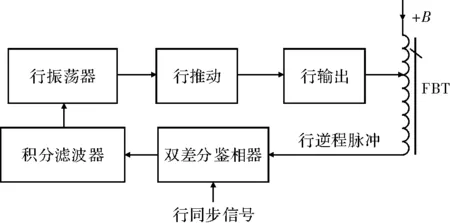

自动频率控制(Automatic Frequency Control,AFC)是一种使输出信号频率与给定频率保持确定关系的自动控制方法。而实现这种功能的电路称为AFC环,相比一般锁相环电路,由于该方法采用闭环结构,所以能使系统的工作频率更加稳定且偏差较小。行扫描AFC是AFC的一种,这种方式应用广泛,其电路结构如图2所示。

图2 行AFC电路结构

2 AFC锁相环电路设计

设计以一般锁相环电路结构为参考,在实现“锁相”功能的基础上加入行扫描AFC方法,使设计的电路更好地控制频率和相位[6-8]。

2.1 电路图设计

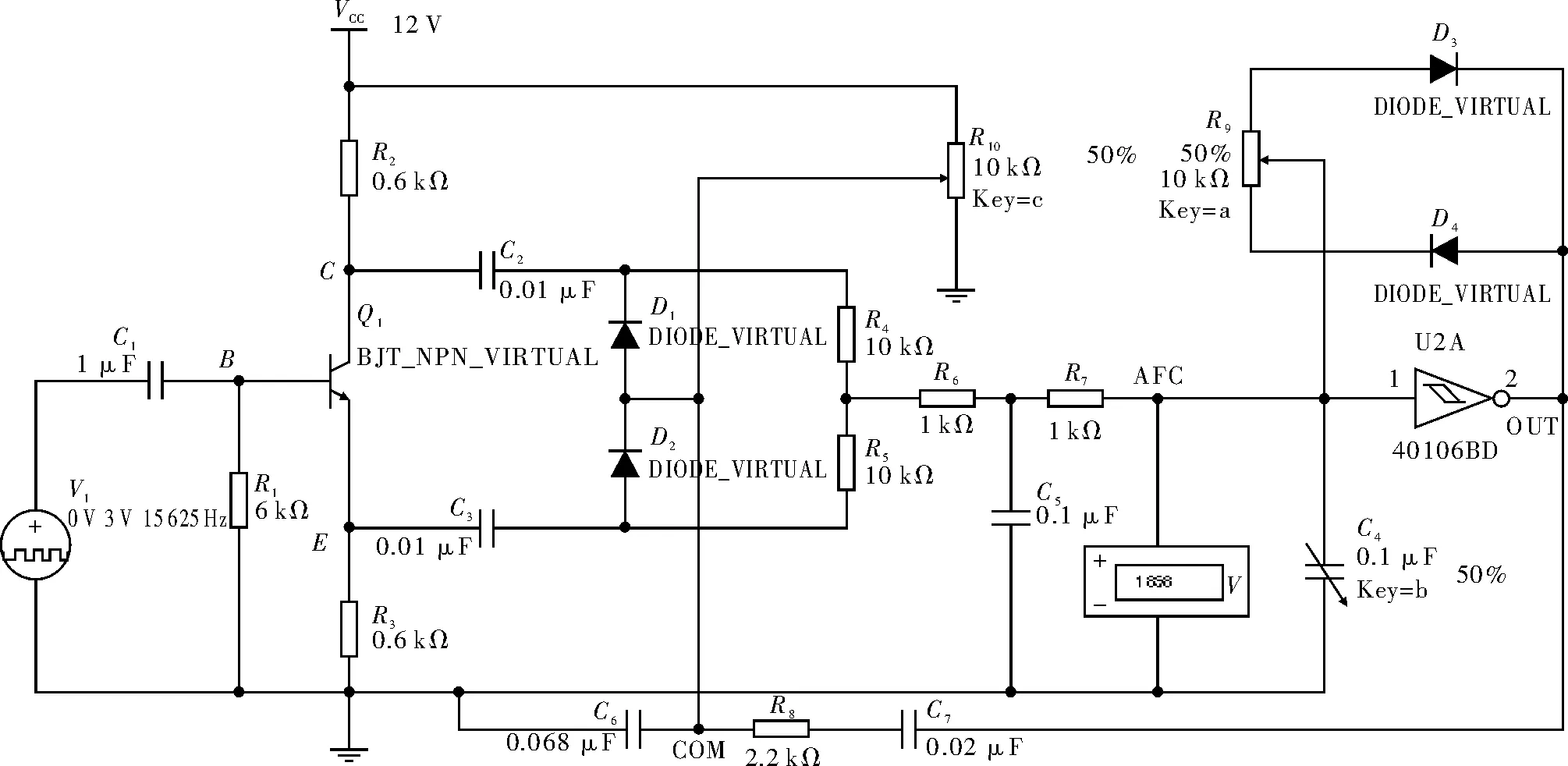

启动Multisim2001,设计的电路如图3所示,电路由鉴相器、环路滤波器和压控振荡器构成。

图3 基于Multisim设计的锁相环电路

(1)脉冲信号源由V1构成,提供行同步信号,方波脉冲的周期为64 μs、脉宽为4.7 μs、幅度为3 V。(2)输入耦合电路由C1、R1构成。(3)AFC鉴相器由Q1、R2、R3、C2、C3、D1、D2、R4、R5组成,属于分相型平衡式。(4)环路滤波器由R6、C5构成,实质是一个低通滤波器。锁相环的压控性和频率稳定性就取决于其时间常数的大小。(5)隔离电阻由R7构成。(6)压控振荡器由U2A、R9、C4、D3、D4构成,其脉冲可变。(7)隔直电容为C7,保证COM点平均电压为0。(8)积分电路由R8、C6组成,形成比较锯齿。(9)调节R9可改变振荡脉宽,方便调出符合比较相位要求的振荡器反馈比较信号。(10)电容C4为可调电容,调节其可方便地改变振荡频率,观察锁相结果。(11)在AFC节点处有直流电压指示器,可观察AFC输出电压。(12)R10为12 V分压电路,提供振荡器正常偏置。

2.2 仿真步骤

(1)按图3连接AFC锁相环仿真电路。1)首先用示波器观察AFC与振荡器断开时的OUT波形。2)按键盘中的A和B分别调节R9阻值和C4容值,观察脉宽和频率变化的规律。3)将AFC到振荡器的连线重新连接好,用示波器分别观察输出端OUT、COM、AFC、晶体管各电极B、C、E各点的波形,并调节R9和C4锁相范围,做好记录。锁相同步时各测试点的波形如图4所示。

图4 锁相同步时各点波形

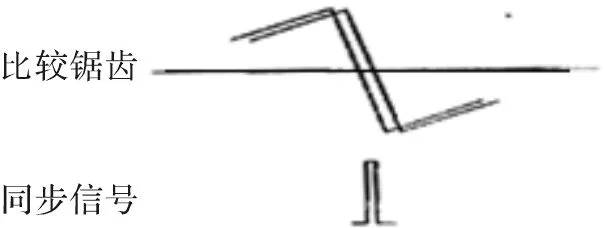

(2)波形分析。1)OUT输出“1”高电平,“0”低电平的振荡波形,是振荡器通过调整R9(85%)获得,原因是为了满足锁相环比较相位的需要。2)COM将OUT输出波形积分获得比较锯齿,锯齿波的逆程放大如图5所示。锁相过程为:设同步信号出现时,对应右边锯齿波逆程处于某一电压值;当振荡频率因某些原因升高,周期变短,即锯齿波左移,当同步信号再出现时,对应左边锯齿波逆程处于较低电压值,即COM点电位下降,引起APC电压也下降,导致振荡器输入端电位降低,使振荡翻转推迟,即振荡频率也下降,通过不断地牵引,电路自动平衡在一个稳定的频率点上,即频率被锁住。可从Ub与COM波形对照看出锁频状况。3)因三极管内部电流分配关系,导致分相器Q1的Uc与Ue的输出波形互为倒相。4)AFC电压波形是振荡器输入端与比较误差电压的波形叠加。

图5 锁相波形

(3)改变参数观察测试结果。通过以上分析,本次设计已初步实现设计要求,为进一步改善电路,可通过如下过程找到合适的元件参数。1)改变比较积分电容C6数值,找出最佳锁相范围的数值。2)增大或减少C1和C2的数值,观察同步性能。3)调节R9,从85%~15%,振荡波形的占空比变化,再微调C4、R10,试图寻找同步点。4)改变V1信号源的频率,找出同步范围。

2.3 仿真结果分析

通过仿真可知,设计的行扫描AFC锁相环电路,相比于一般锁相环电路,由于加入自动频率控制方法和闭环系统,使得电路具有更好的频率比较功能,通过频率差不断地反馈最终实现“锁相”。同时通过调整元件参数,可得到系统工作最佳的锁相范围数据,这些数据大幅简化了下一步PCB的设计与制作,可见达到了设计要求。

3 结束语

通过基于Multisim的行扫描AFC锁相环电路设计,该电路可通过行扫描自动频率控制方法比较输入信号和振荡器输出信号,逐步减小输入输出之间的频率差,以实现两者相位的一致。总之,利用Multisim不但可快速设计出所需的电路,同时因其灵活的编辑环境,通过对元件参数的调整,可找到更加符合设计要求的电路。

[1] 蒋卓勤,邓玉元.Multisim2001及其在电子设计中的应用[M].西安:西安电子科技大学出版社,2003.

[2] 黄智伟.基于Multisim2001的电子电路计算机仿真设计与分析[M].北京:电子工业出版社,2004.

[3] 曾庆贵.锁相环集成电路原理与应用[M].上海:上海科学技术出版社,2012.

[4] 张刚.CMOS锁相环集成电路设计[M].北京:清华大学出版社,2013.

[5] 徐江涛,原义栋.一种高速低相位噪声锁相环的设计[J].天津大学学报,2008,41(3):300-304.

[6] 王刚,王艳芬.基于Multisim的锁相环应用电路仿真[J].电气电子教学学报,2008,30(3):67-69.

[7] 樊孝明.Multisim在“锁相与频率合成”课程教学中的应用[J].电气电子教学学报,2011,33(4):106-108.

[8] 侯卫周,向兵.基于Multisim10.1频率自动跟踪锁相环电路的仿真分析[J].实验室研究与探索,2014,33(6):86-89.

Simulation Design of Line Scanning AFC PLL Circuit Based on Multisim

LI Hongen

(Biomedical Engineering Department,Changzhi Medical College,Changzhi 046000,China)

The phase-locked loop(PLL) circuit has extensive applications in various electronic devices.It can control the phase error and implement frequency synchronism between the input signal and output signal.To design a line scanning AFC PLL circuit,Multisim2001,which is powerful in circuit design and simulation,is used.Simulation results show that the circuit designed has the function of phase locking.And because of the simple and flexible simulation environment of Multisim,the optimal phase locking range can be obtained by changing the parameters of the devices and observing the changes in waveform of each point,thus saving cost for PCB design and manufacturing.

Multisim2001;line scanning;phase-locked loop;AFC

2014- 11- 05

李宏恩(1983—),男,硕士,讲师。研究方向:电子技术应用,PCB设计与制作。E-mail:lihongen888@qq.com

10.16180/j.cnki.issn1007-7820.2015.05.030

TN702

A

1007-7820(2015)05-105-03