基于PowerPC的SATA固态硬盘存储阵列设计

孟 琪,张 杰,范晓星

(西安电子科技大学 电子信息攻防对抗与仿真技术教育部重点实验室,陕西 西安 710071)

基于PowerPC的SATA固态硬盘存储阵列设计

孟 琪,张 杰,范晓星

(西安电子科技大学 电子信息攻防对抗与仿真技术教育部重点实验室,陕西 西安 710071)

设计了基于SATA接口的固态阵列存储系统。系统选用FPGA作为硬件平台,内嵌PPC440处理器作为处理单元,以SATA接口的固态硬盘阵列作为存储介质,并采用RAID0技术。该存储阵列系统具有海量、高带宽等特点。系统同时具有实时存储、传输和管理等功能,并可脱机运行。

FPGA;PPC440处理器;SATA接口;固态硬盘;RAID0

在科研和生产中,往往需要记录实时性强的信息便于后续的分析处理。随着科学技术的发展,高速、海量、能脱机的数据存储设备已成为工业和科研不可或缺的关键设备。而目前市场上常见的硬盘、Flash等存储介质均不具有海量且高速的特点,无法满足需求。因此研究一种同时具有高速传输、海量存储、能脱机运行等特点的数据存储设备具有重要意义。

磁盘阵列(RAID)基本思想是将多个相对便宜的硬盘组合,成为一个硬盘阵列组,使性能达到甚至超过一个价格昂贵、容量巨大的硬盘性能。RAID由多个硬盘组成,通过在多个硬盘上同时存储数据来大幅度提高存储系统的数据吞吐量。固态硬盘(SSD)是一种基于闪存的存储技术。与普通磁盘相比,固态硬盘由半单体存储器构成,没有移动的部件,因而随机访问的时间比旋转磁盘要快,能耗更低,同时也更结实。不过,SSD也有一些缺点。首先,因为反复写之后,闪存块会磨损,所以SSD也容易磨损。其次,SSD的价格较高。基于RAID技术的固态硬盘存储阵列系统[1]不仅解决了SSD单盘容量较小的问题,且提升了硬盘的传输速率,因而具有高传输带宽、大容量、无损、携带轻便等特点。

本文选用FPGA作为硬件平台,内嵌PPC440处理器作为处理单元,以SATA接口的固态硬盘阵列作为存储介质,并采用RAID0技术设计了基于SATA接口的固态阵列存储系统,此设计对传输带宽的提升和容量的增大具有重要作用。

1 SATA固态硬盘系统设计

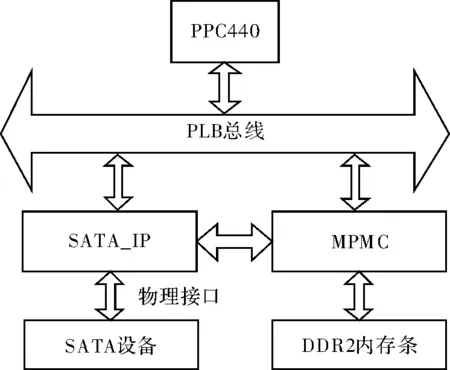

SATA控制器是SSD控制的核心。系统选用Xilinx Virtex5 FPGA作为SATA控制器。SATA控制器根据SATA协议实现主机与硬盘之间的数据传输和管理。系统的数据管理和传输上述功能的软件处理部分,包括SATA应用层的命令传输协议,对数据流的分配等,通过嵌在FPGA内部的处理器PPC440实现。系统在FPGA上集成了SATA控制器、多端口控制器(MPMC)、与PPC440通过PLB总线互联,实现了片上系统,完成了与硬盘的通信以及数据的传输。

图1 系统框图

2 SATA控制器的FPGA实现

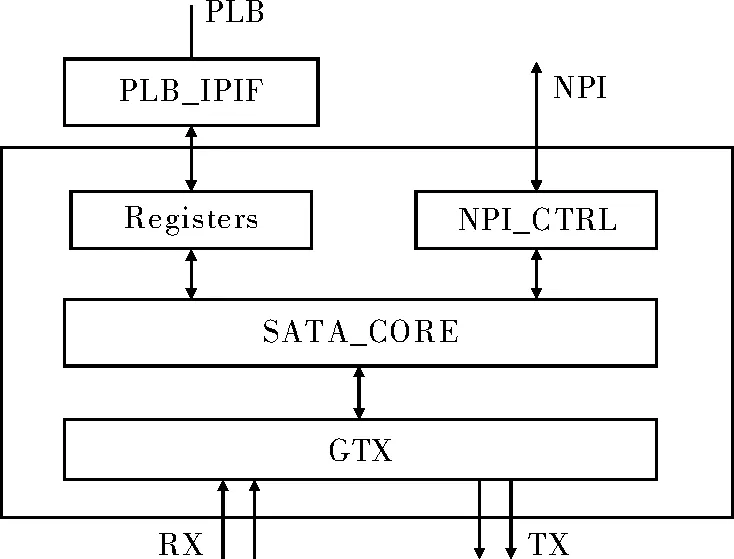

SATA控制器基于SATA协议2.0实现,SATA2.0协议的结构体系分为:物理层、链路层、传输层和应用层。其中,命令层响应ATA命令并控制映像寄存器组。SATA控制器逻辑框图如图2所示。

图2 SATA控制器逻辑框图

如图1所示,SATA控制器逻辑模块包括物理层、SATA_CORE和用户接口模块。物理层通过对集成在FPGA内部的千兆位级串行收发器GTX进行参数配置可以实现;SATA_CORE模块实现了SATA协议的链路层和传输层的功能,负责帧的封装、发送、接收与解析;用户接口模块包括映像寄存器组,PLB接口和NPI接口。

应用层提供了一个映像寄存器组。本设计中将映像寄存器组由32个32位寄存器组成,其中有5个寄存器是用户自定义的,其余的兼容ATA协议指令集,包括Status、Command、Error、LBA low等,用于存放SATA_CORE的控制信息、状态信息、命令、参数、LBA地址等。该寄存器组是地址映射的,一端与PLB总线相连,用于PPC处理器对寄存器的读写,另一端与SATA_CORE模块相连,用于记录SATA_CORE的状态信息。

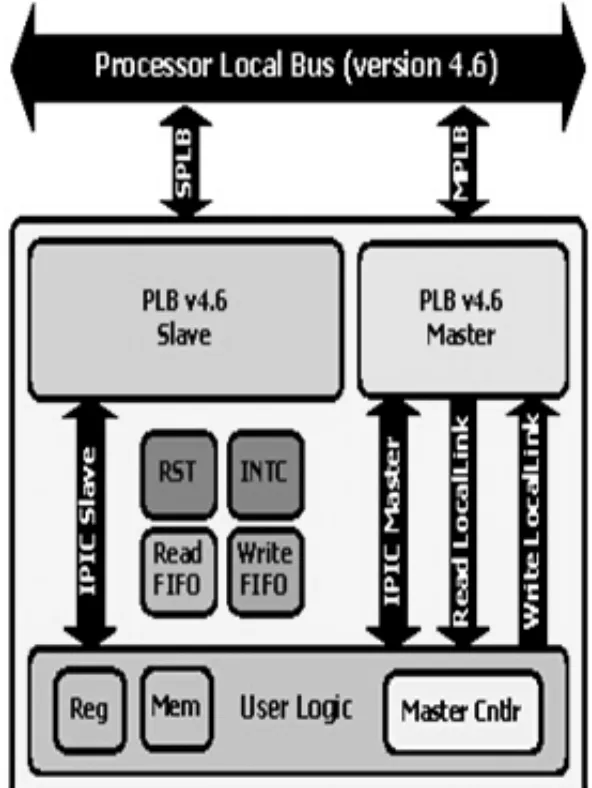

PLB总线是一种高带宽、低延迟、高性能的处理器内部总线,用于连接高性能CPU高速存储控制器、仲裁器等。由于PLB总线协议的复杂性,为了让用户更加方便的地使用,Xilinx公司开发了PLB生成向导。该向导在PLB总线与IP核引入了PLB接口,即IPIF。利用IPIF对映像寄存器进行配置便可实现SATA控制器的控制功能。

图3 IPIF

SATA控制器在传输命令以及控制信息时通过PLB总线,而对数据的读写是通过NPI接口与多端口控制器(MPMC)相连,直接读写存储单元。NPI接口控制器(NPI_CTRL)用于实现NPI接口协议,数据宽度为64位,支持burst工作模式,一次burst读或写最多可传输256 Byte数据,每次burst之后硬件会自动更新地址,得到下一个burst的起始地址。

图4 64 bit NPI 32 word burst 读

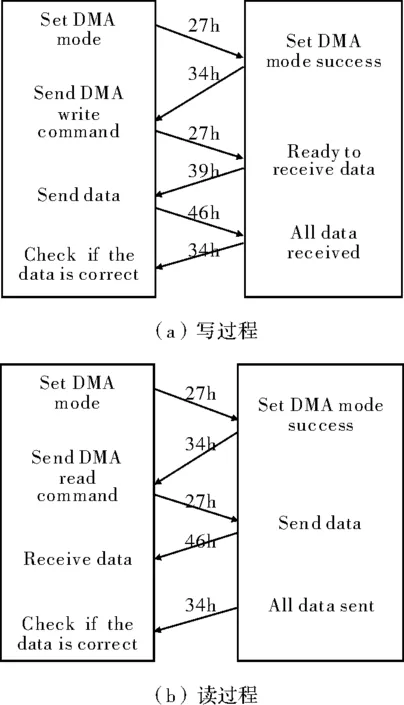

3 SATA控制器读写数据

SATA协议定义了一系列命令传输协议,包括软件复位协议、PIO数据输入命令协议、PIO数据输出命令协议、DMA数据输入命令协议、DMA数据输出命令协议等。其中DMA方式是一种效率极高的传输方式,大量数据的传输一般使用DMA模式。图5为DMA读写命令过程中主机与硬盘之间帧的交换情况。

下面以主机向设备数据的过程为例来说明数据传输的流程:系统上电后,PPC初始化SATA控制器,包括NPI控制模块(控制内存条读写),AD_DATA_CHECK模块(硬盘读数据模块),初始化中断系统,设置硬盘工作模式模块,DMA模式设置,如图6所示。

图5 DMA读写过程框图

图6 与硬盘建立通信连接

图7 设置硬盘模式与建立中断系统

主机向设备发送数据时,NPI接口控制模块按照NPI接口协议将访问地址,数据长度和控制信号给多端口存储控制器MPMC,在NPI控制模块和MPMC的共同控制下,原始数据经过NPI接口写入发送数据缓冲区中。发送数据缓冲区中数据聚集到一定数量时,帧生成模块读出发送数据缓冲区的原始数据,经过对数据编码、校验、添加帧边界、组帧,将完整的帧写入帧发送缓冲区。当帧发送缓冲区中数据聚集到一定数量时,帧发送模块发送请求原语,按照SATA协议的时序控制帧发送缓冲区的读使能。将从帧发送缓冲区读出的数据写入GTX,将数据转变为低压差分信号,发送到SATA电缆上。

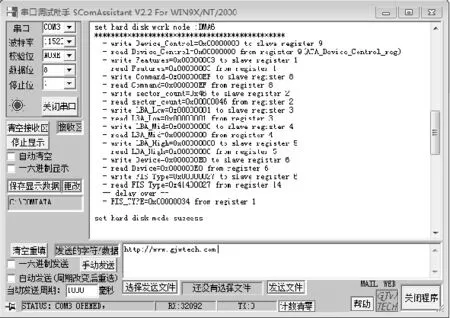

4 存储系统架构的设计

为了实时存储无间断的、高速数据,系统采用基于多片DDR2交替缓存的技术。先将数据分为数据块,然后交替的写入DDR2。为了突破总线带宽瓶颈,系统将数据与信息分开传输。利用高带宽的NPI接口直接传输数据,用PLB总线来传输命令和状态信息。系统实例如图6所示。

图8 存储系统实例图

FPGA选用Xilinx公司的XC5vfx200tff1738-2,嵌入式处理器选用FPGA内嵌的PPC440,高速缓存单元由 DDR2a内存条和DDR2b内存条组成,其容量为1 GB、64位的DDR2内存条,磁盘阵列由8块SSD硬盘组成。

采集的数据通过data_collection_0模块、data_collection_1模块分别写入内存条DDR2_a和DDR2_b。将1 GB的DDR2_a、DDR2_b划分为8个128 MB的数据块,其中数据块0~3称为上半页,数据块4~7称为下半页。

图9 DDR2内存条

图10为从存储阵列读写数据的流程图,其中Work_en为工作标志位;W_flag为写标志位;R_flag为读标志位;flagA_L,flagB_L分为DDR2_a,DDR2_b上半页写满标志位;flagA_H,flagB_H分为DDR2_a,DDR2_b下半页写满标志位。

图10 存储阵列读写过程

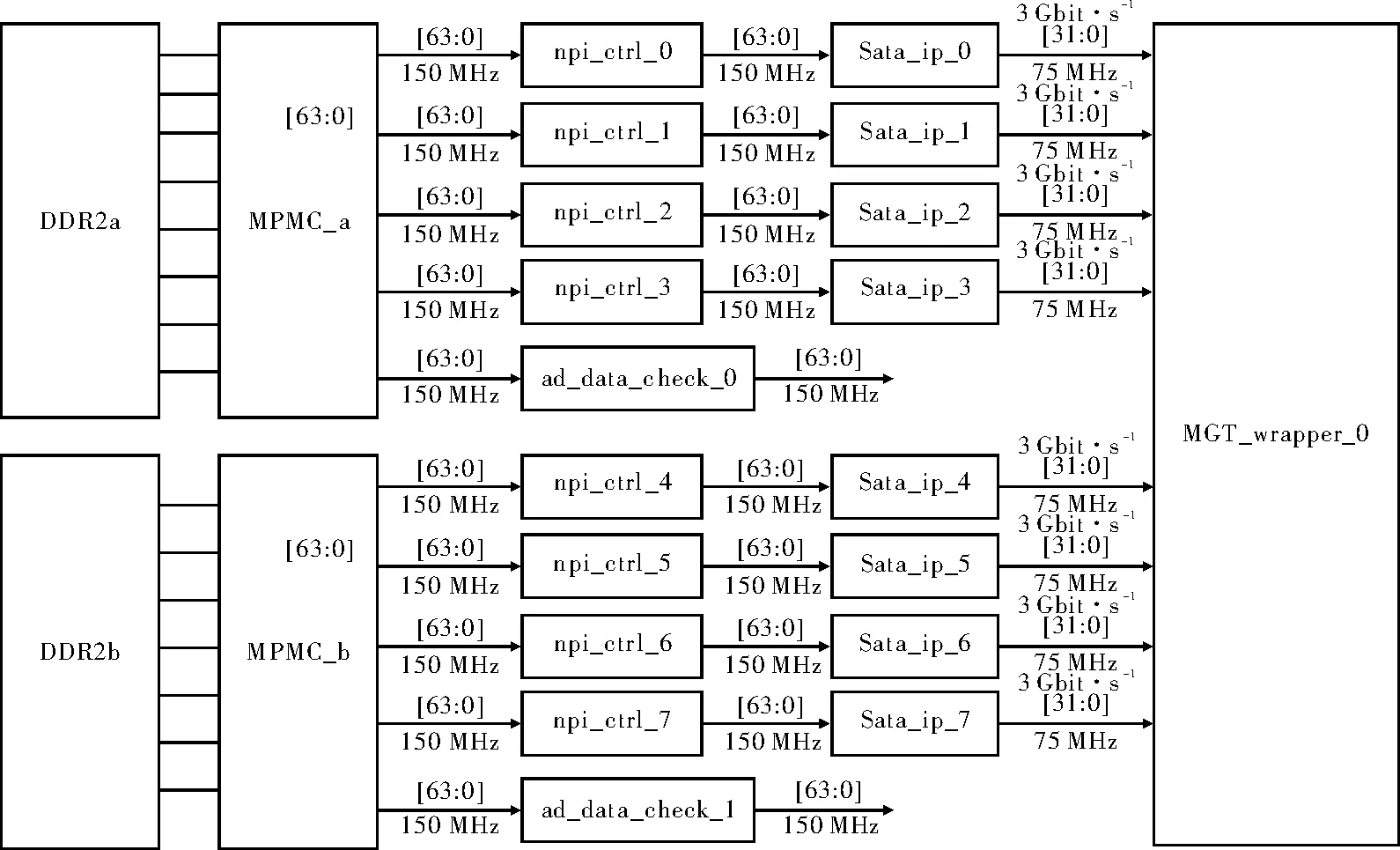

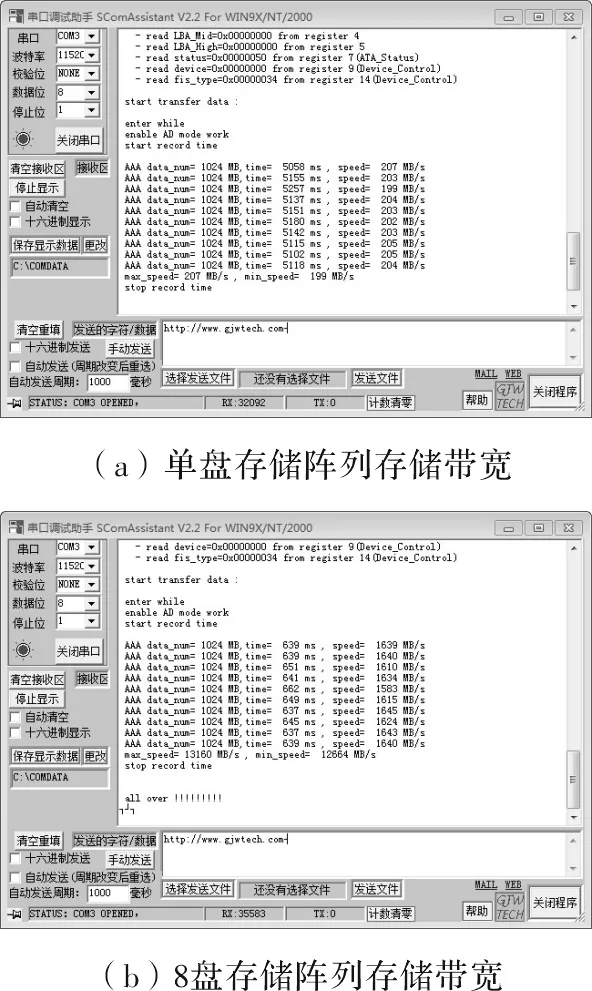

5 实验结果

用上述构建的存储架构,分别向单个硬盘及8盘存储阵列写入10 GB数据,存储带宽如图11所示。通过对比单个SATA控制器控制硬盘存储与8个SATA控制器控制硬盘并行存储,得出通过增加控制器数量,能够增加存储系统的带宽。

图11 单盘和8盘存储阵列存储带宽对比图

6 结束语

本文介绍了一种SATA接口固态存储阵列的实现

形式。在单片FPGA中实现多个SATA控制器,形成磁盘阵列,提高了存储带宽。数据的传输是通过NPI接口直接访问存储器,控制信息以及状态信息是通过PLB总线传输,突破了总线带宽限制的瓶颈。

[1] 吕卫祥.基于SATA硬盘阵列的高速数据存取技术研究[D].南京:南京理工大学,2010.

[2] 何宾.片上可编程系统原理及应用[M].北京:清华大学出版社,2010.

[3] Xilinx.Virtex-5 FPGA GTX transceiver user guide[M].USA:Xilinx,2009.

[4] Xilinx.Multi-port memory controller[M].USA:Xilinx,2008.

[5] Xilinx.FIFO generator v4.4 user guide[M].USA:Xilinx,2008.

[6] 步凯.基于RAID技术的固态存储阵列系统的研究与设计[D].长沙:国防科学技术大学,2008.

[7] 叶肇晋,张稀楠,马磊.基于Xilinx FPGA片上嵌入式用户IP核开发[M].西安:西安电子科技大学出版社,2008.

[8] Xilinx.PLBV46 slave single[M].USA:Xilinx,2008.

[9] Xilinx.PLB usage in Xilinx FPGAs[M].USA:Xilinx,2005.

[10]赵峰,马迪铭,孙炜,等.FPGA上的嵌入式系统设计实例[M].西安:西安电子科技大学出版社,2008.

Design of Hard Disk Storage Array of SATA SSD Based on PowerPC

MENG Qi,ZHANG Jie,FAN Xiaoxing

(Key Lab.of Electronic Information Countermeasure and Simulation Technology of Ministry of Education,Xidian University,Xi’an 710071,China)

The paper puts forward a solid-state storage array system based on the SATA interface.The design selects FPGA as the hardware platform and the embedded PPC440 as CPU to control the whole system.The storage array based on the SATA solid disk adopts RAID0 technology and is used to improve hard disk drive storage and bandwidth.The design can implement the functions of real-time data storage,transmission and management and achieve offline operation.

FPGA;PPC440 processor;SATA interface;solid disk;RAID0

2014- 09- 02

孟琪(1990—),女,硕士研究生。研究方向:片上嵌入式系统。E-mail:mengqi1120@163.com

10.16180/j.cnki.issn1007-7820.2015.04.030

TN79

A

1007-7820(2015)04-111-05