The Design of High-Speed Data Acquisition System Based on the USB3.0 Interface

YUE Xiaozhong,PEI Dongxing,WANG Jian

(North University of China Science and Technology on Electronic Test and Measurement Laboratory,Taiyuan 030051,China)

The Design of High-Speed Data Acquisition System Based on the USB3.0 Interface

YUE Xiaozhong,PEI Dongxing*,WANG Jian

(North University of China Science and Technology on Electronic Test and Measurement Laboratory,Taiyuan 030051,China)

To meet the problem of current existing in the explosion field measurement memory test system,the data transmission is slow and often lost some data.The high-speed data acquisition system based on USB3.0 is designed by using the data collection technology,memory test technology and parallel sampling techniques.The system achieved the high-speed parallel data acquisition with two sampling rates of up to 500 Msample/s A/D chip.It can bring the analog signal from the XX Explosion power test field to the FPGA after A/D conversion,and transmit to the PC by the USB3.0 interface.Data storage can use the time-storage technology.The design method can solved the problem of high-speed transmission and large data storage during the data collection effectively.

memory testing;USB3.0 interface;data acquisition;high-speed transmission

随着信息技术的发展,特别是各种数字处理器处理速度的提高,在一些恶劣环境和无法实时传输数据的情况下,还必须使用存储测试方法。人们对数据采集系统的要求越来越高,特别是在一些需要在极短时间内完成大量数据采集,进行实时处理的场合,对数据采集系统的速度提出了非常高的要求。相应地,人们对数据采集系统的存储能力,接口能力以及抗干扰能力也提出更高的要求,这是数据采集发展的方向。高速稳定可靠的数据传输技术在高速数据采集系统中扮演着重要的角色,而随着数据传输速度越来越快,对数据的抗干扰性的要求也越来越高,本实验室以前一直使用的是USB2.0接口,传输速率最高达到480 Mbit/s,随着以Gbyte为单位的大容量数据传输要求的出现,传统的数据传输标准[1-2],例如RS-422,RS485,SCSI和PECL等传输标准己无法满足设计高速数据采集系统的设计要求,而USB3.0技术的出现无疑解决了一般传输标准无法满足高速数据传输的要求的窘困[3]。在诸如遥测、遥感等采集操作的数据传输速率高、需要采集保存的数据量大的场合,无法做到实时分析和处理,而必须将采集到的数据以适当的方式存储起来,以便分析和处理。所以,在本设计中分时存储技术使得这一问题也得到了很好的解决。本设计提出了选用USB3.0芯片CYUSB3014作为USB3.0控制芯片,不仅提高了数据传输的速率还能保证数据传输的准确性与稳定性[4]。

1 硬件电路设计

1.1系统结构组成及工作原理

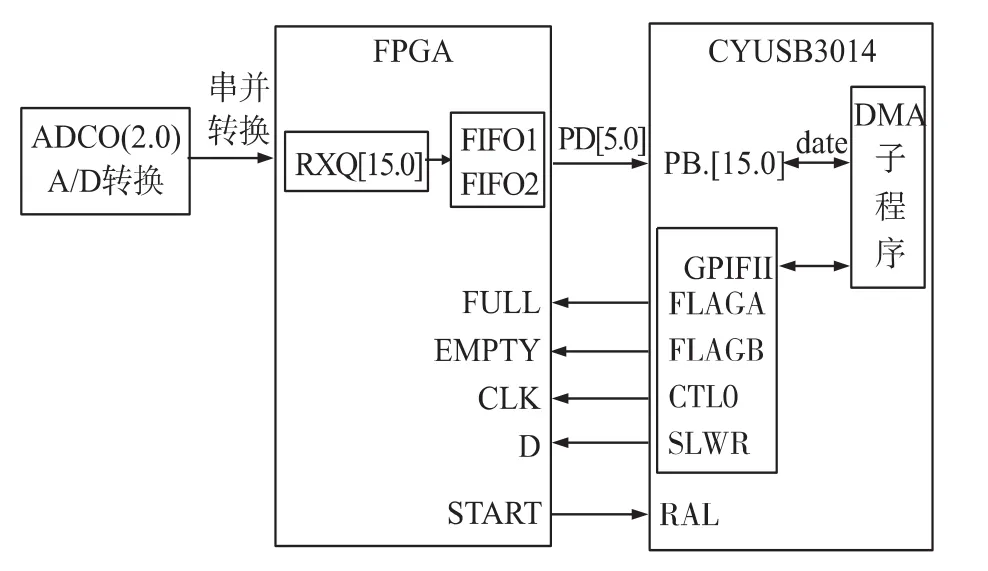

本文设计的数据采集系统主要包含3部分:A/D转换器,可编程逻辑器件FPGA和USB3.0传输接口。A/D为系统的核心芯片,负责将经过调理通道后的模拟信号转换成数字信号。系统选用Aimel公司的AT84AD004模数转换芯片。FPGA选用ATLERA公司的EPZS15F484CS,含有LVDS接收模块可以直接与A/D转换后的数据不需要其他的匹配直接进行数据传输。FPGA主要包含一些硬件电路的设计,A/D控制码发送电路、数据转换电路、存储电路和时钟电路。USB3.0则完成把数据高速传输至上位机完成处理。该高速数据采集系统以FPGA芯片为主控制器,其硬件上与GPIFⅡ接口相连接,通过FPGA与GPIFⅡ之间的逻辑配合,实现FX3同步从FIFO写模式的数据传输,将数据传输至上位机[5]。图1高速数据采集系统的硬件连接框图。

图1 硬件连接框图

首先通过FPGA与GPIFⅡ的逻辑配合使得内部电路向A/D的寄存器写入控制字,选择A/D的工作模式;然后FPGA内部的锁相环对输入时钟进行倍频,将倍频后的时钟送到外部的锁相环,外部锁相环产生A/D转换器的采样时,A/D开始模拟信号到数字信号的转换,并将转换后的数据送入FPGA中,最后通过USB3.0传输至上位机[6-7]。

本设计中,模拟信号调理电路将传感器输出的模拟信号进行放大、滤波等处理,因此利用ADI公司的运放芯片AD8138将单端的模拟输入信号转换为差分格式的信号,提供给A/D转换器。

2 模块化电路设计

2.1A/D转换模块

系统的A/D转换芯片AT84AD004也采用差分模拟输入差分结构对模拟输入信号的偶次谐波有较高的抑制性,该芯片内部含有两个分辨率为8位,最高采样率为500 Msample/s、信号带宽达1 GHz的A/D转换器,芯片集成了采样保持器,提高了系统的动态性能。芯片还有输出数据分配器,降低对后面接口电路的要求;输出数据格式为LVDS,而且对共模噪声有着非常好的抑制作用,适合高速数据传输[8]。

A/D芯片的寄存器写操作通过三线串行口写入,三线串行口由串行时钟输入口SCLK,串行装载使能口SLDN和串行数据输入口SDATA构成,该三线串行口提供了访问A/D芯片内部的8个只写寄存器的路径。利用FPGA内部的串并转换电路模块对经过LVDS接收机转换格式后的数据进行降速,降速系数设定为2,对数据进行2倍降速。ADCQ[7…0]为A/D输出的8位数据,CKLQ为外部提供的差分时钟由专用的时钟IO口进入,设计中需要在内部的Megawizardplug一InManager中设置输入的通道数目、降速系数、数据的速率。RX_Q[15…0]为2倍降速下串并转换后得到的16 bit数据。图2是模数转换及数据传输框图。

图2 模数转换及数据传输框图

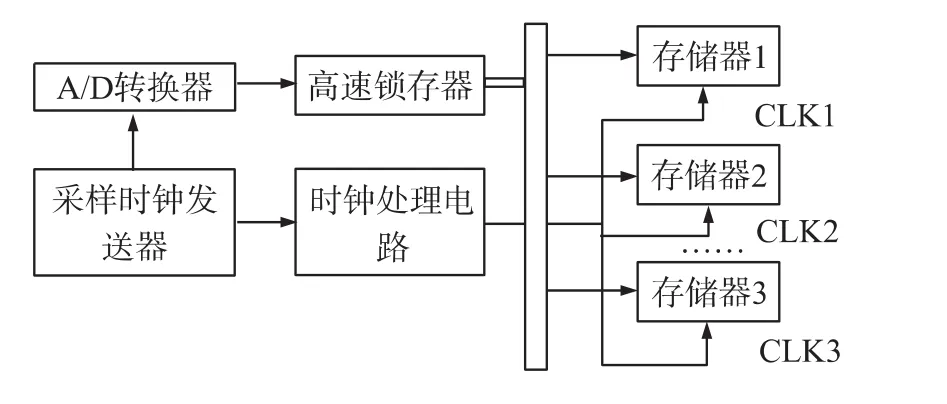

2.2存储模块

对于高速数据采集系统而言,如果采用存取速度很高的高速FIFO,必定会提高设计成本,所以考虑采用分时存储的方法[9],分时存储技术利用一个高速锁存器将采集的高速数据锁存,而后利用多个相对慢速的存储器对数据进行存储以保证数据存储的可靠性。由于多个静态存储器分时参与了数据存储的过程,使得多个慢速静态存储器分时存储操作过程进行了叠加,其效果等效于一个高速静态存储器的操作。采用两片FIFO,在不同的写时钟作用下,交替地将采样数据按一定的顺序写入到两个FIFO中去。同步FIFO其特点为读写指针连续推进,可同时进行读写操作,同时有空、满、可以编程的逻辑空和可以编程的逻辑满等标志位信号,便于和USB3.0控制器模块进行数据传输握手。图3是分时存储的设计。

图3 分时存储的设计

3 软件设计

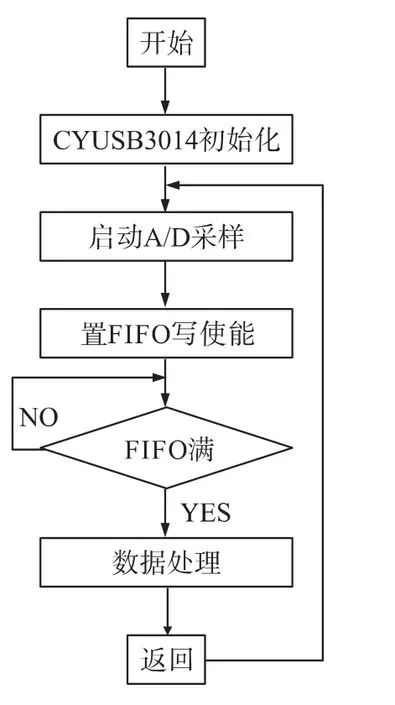

3.1系统流程介绍

软件设计的目的是实现数据采集系统正常工作,完成了从系统上电开始,A/D采样输入信号到采样处理数据的工作。主要包括系统初始化、采样控制的选择,而采样控制包括A/D工作模式的选择、时钟的控制、数据处理。在USB3.0初始化后,需要对A/D工作模式进行选择,其模式选择是通过控制FPGA内部串行码发送电路实现的。首先,通过两次写操作将A/D所需的19 bit码值写入FPGA内部,通过内部锁存电路将写入的码值锁存起来,然后启动FPGA内部的串行码发送电路,将19 bit串行码值依次写入A/D,以实现A/D工作模式的选择。在A/D工作模式选择结束后,需要对A/D采样时钟进行控制,然后开放采样时钟触发A/D采样,清空FIFO,然后打开FIFO写使能,等待数据写入FIFO,一旦FIFO写满后,会产生一个写满标志位,当上位机检测到该标志位时,关断写使能,停止FIFO写操作,同时,关断A/D的采样时钟,最后开启读使能,读取FIFO中存储的数据。图4是系统流程图。

图4 系统流程图

3.2下位机程序设计

用于系统测试的外围设备使用FPGA作为逻辑控制器,其硬件上与GPIFⅡ接口相连接,通过FPGA与GPIFⅡ之间的逻辑配合,实现FX3同步从FIFO写模式的数据传输,将数据从存储器中将数据传输至上位机。数据传输系统的接口时钟是由FPGA提供的,时钟频率为80 MHz。设置SLWR为低电平、SLCS为低电平、PKEND为高电平、SLRD为高电平,这几种情况同时发生的时,GPIF接口可以进行写操作。图5同步写时序仿真图。

图5 同步写时序仿真图

FX3的FIFO与Socket(套接字)相关联。GPIFⅡ一侧的套接字相当于端点。FX3可提供多达4个物理线程用于GPIFⅡ数据传输,将要使用的套接字须映射至某个线程上,这种映射由固件完成。GPIFⅡ接口上的信号A0:A1表示要访问的线程,数据传输时,DMA结构将数据路由至映射到该线程上的套接字。当A0:A1=0时,数据被路由至映射到线程0的套接字1[10]。FPGA根据系统要求配置A1:A0线程选择地址信号。

FLAGA和FLAGB都是FX3固件配置的标志限号,它们可以配置为空、满、局部空或局部满信号。这些由FX3内部的DMA硬件引擎控制。标志语特定的线程相关联,可显示当前映射至该线程的套接字状态。标志会在数据从套接字中读出时只是空/非空状态,也会在数据写入套接字时只是满/不满状态。数据传输系统接口中应用FLAGA作为当前线程套接字的满/不满状态标志。FIFO地址由A0:A1=0确定线程0,FLAGA信号为高电平,表示套接字缓冲区不满,SLCS一直为低电平使能状态,当应用程序通过GPIFⅡ的INT接口向FPGA发送一个高电平脉冲时,SLWR下拉至低电平,数据开始从时钟上升沿向套接字缓冲区写入数据,紧接着FX3会启动DMA通道,当缓冲区被装满数据,FLAGA信号下拉至低电平,相应的DMA回调函数被调用,回调函数将数据送到U端口,然后从U端口传送至上位机。FPGA逻辑控制程序波形仿真图如图6所示。

图6 FPGA逻辑控制程序波形仿真图

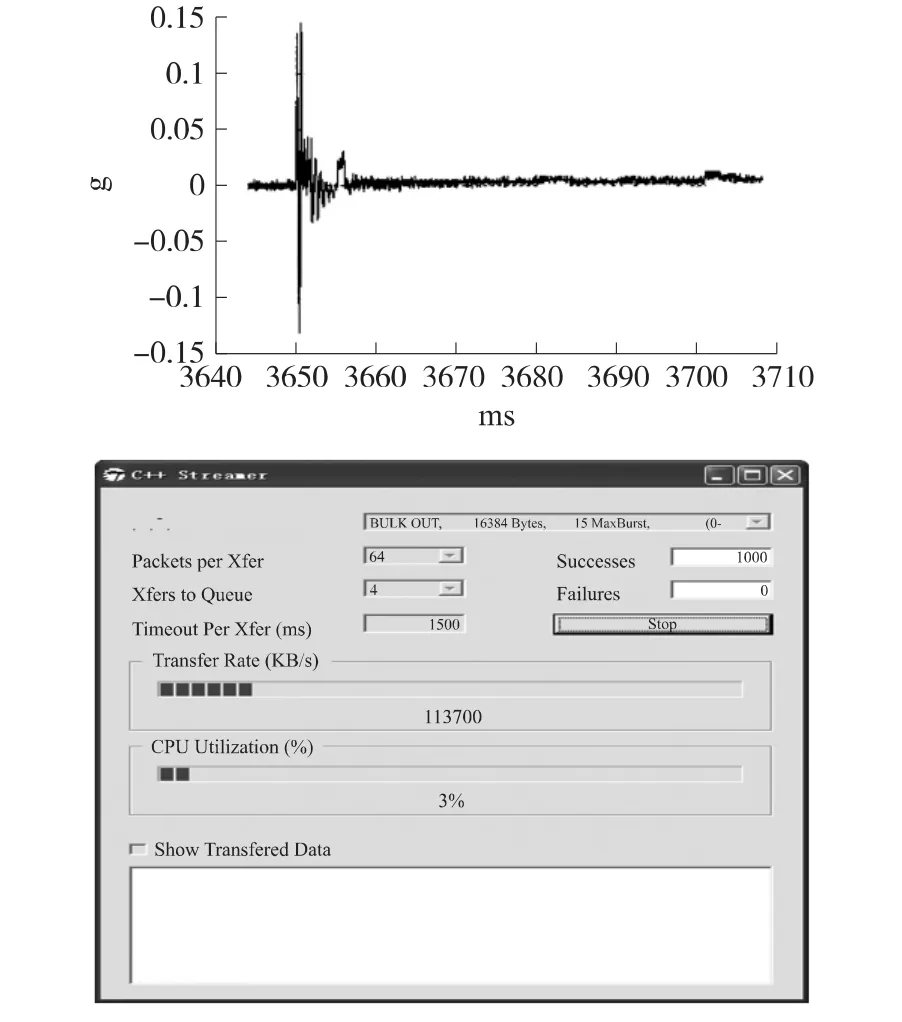

4 分析测试

图7是由某次靶场实验结果分析得到的记录毁伤威力场中振动加速度的变化曲线。左图是振动加速度曲线冲击波完整信号,右图是数据传输系统在接口时钟为80 MHz时测试得出的数据传输速率,达到了113 700 kbyte/s的超高速度,比以往使用的USB2.0接口传输速率更快,并且无点的丢失。由实验结果分析,在爆炸威力试验场相同距离的测点冲击波到达时间基本一致[11],可以看出超压峰值基本符合冲击波衰减规律,完好的数据显示了本设计的高速采集与传输系统在测试中的可靠性和实用性,也表明本数据采集系统可控性强、同步性好、数据完整,传输速率快,是一套成功、实用的采集系统。

图7 采集数据曲线与传输速度速率

5 总结

本设计的采集系统有很多优点,通过USB3.0接口的超高速传输特性进行高速数据采集卡的设计和分时存储的设计,可有效地解决高速数据采集中的数据传输和存储问题,测量结果误差小,可信度高有利于实现数据的实时处理[12]。采用Cypress公司的USB3.0专用接口芯片CYUSB3014与FPGA连接完成了采样数据的高速传输测试,经过多次测试,USB3.0接口的准确、超高速、实时等性能得到了充分的体现。

[1]张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社,2002:32-36.

[2]崔亮飞.USB总线技术在大容量存储测试系统中的应用[J].仪表技术,2010(11):62-64.

[3]高振江.USB3.0通用串行接口技术[J].电子元器件应用,2009(7):77-80.

[4]芦艳芳,郭林.USB3.0兼容性与电源分配方案[J].电脑知识与技术,2010(27):7649-7650.

[5]吴鹏,陶正苏,胡宇贞.基于单片机USB接口的PC主机驱动程序和应用程序设计[J].电子器件,2005(3):612-614.

[6]刘瑞芳,丁卫平,胡文静,等.基于USB3.0高速数据采集系统的研究与设计[J].现代计算机,2011(12):39-43.

[7]白同云.电磁兼容设计[M].北京:北京邮电大学出版社,2011.

[8]刘泽西,程晶晶,孔力.基于USB2.0接口的高速实时数据采集系统[J].测控技术,2007,26(2):34-37.

[9]沈兰荪.高速数据采集系统原理及应用[M].北京:人民邮电出版社,1995:80-82.

[10]Hewlett-Packard Company,Intel Corporation,Microsoft Corporation,et al.Universal Serial Bus3.0 Specification[R].Revision 1.0,November 12,2008.

[11]仲倩.爆炸源毁伤效应测评方法研究[D].南京理工大学,2007.

[12]费业泰.误差理论与数据处理[M].5版.北京:机械工业出版社,2006:24-29.

岳孝忠(1987-),男,汉族,山西省吕梁市人,中北大学硕士研究生,主要研究方向为动态测试与智能仪器,514789733 @qq.com;

裴东兴(1970-),男,教授,研究方向为动态测试、数据压缩、动态校准;近年获得国防科技进步二等奖两项,国防科工委鉴定两项,通过省科委鉴定3项,发表论文多篇,peidongxing@nuc.edu.cn。

EEACC:7210G10.3969/j.issn.1005-9490.2015.01.030

基于USB3.0接口高速数据采集系统的设计

岳孝忠,裴东兴*,王健

(中北大学电子测试技术重点实验室,太原030051)

针对当前爆炸场测量中存在存储测试系统数据传输慢,经常出现丢点问题,综合运用数据采集技术、存储测试技术,设计了一种基于USB3.0的高速数据采集系统,采用并行采样技术,用两片采样率高达500 Msample/s的A/D芯片,实现高速并行数据采集,该采集系统将在XX爆炸威力试验场的模拟信号,经过模数转换送入FPGA中,再通过USB3.0接口高速传输给上位机,数据存储采用分时存储技术;该设计方法有效地解决了大容量数据采集过程中的数据的高速传输和存储问题。

存储测试;USB3.0接口;数据采集;高速传输

TP334.7

A文献标识码:1005-9490(2015)01-0140-04

2014-01-10修改日期:2014-02-20

- 电子器件的其它文章

- The Implementation of CRC Algorithm Based on FPGA

- The Implementation of DDFS by Using Six Segments QLA Algorithm

- A Power Optimization Strategy of Directive Cache on DSP*

- Design of Intelligent Indoor Air Purification System*

- Design of Oxygen Concentration Detection Based on WiFi and Cloud Intelligent*

- Design of the Efficient Control System of Automatic Meteorological Station*