VHDL中的有限状态机教学方法研究

吕高焕,杨 亮,邓冠龙

(鲁东大学信息与电气工程学院,山东烟台264025)

0 引言

在我国高校电子类专业课程中,可编程逻辑器件PLD(Programmable Logic Device)是必不可少的教学内容[1,2]。目前,现场可编程逻辑门阵列FPGA(Field Programmable Gate Arrays)是获得最广泛应用的一类PLD。开发此类PLD常用的工具是VHDL语言[3,4]。在VHDL语言中,有限状态机FSM(Finite State Machine)是数字逻辑电路设计的核心部分,是VHDL语言的精髓所在,又是学生理解的难点所在。由于FSM系统编程复杂,控制量和信号量多,学生通常会感到棘手,编出的程序往往不能满足系统需求。因此,讲好VHDL语言中的FSM是很有挑战性的。

FSM分Moore型和Mealy型两类[5-7]。Moore型FSM的输出仅与当前状态有关,而Mealy型FSM的输出除与当前状态有关外,还与当前输入信号有关。因此,两类FSM在编程过程中有些差异。

在FSM的设计过程中,状态控制信号的分类非常重要,它不仅决定了程序的条理性,还决定了所设计系统的有效性和可靠性。我们将控制信号分为两类,一类是强制状态控制信号,一类是常规状态控制信号,将这两类信号放在不同的控制进程中,分别编程控制。教学过程中,我们将FSM的编程步骤分为三步,即:系统图、状态转移图和编程。系统图表示了整个系统的输入、输出关系,并标示了控制信号在系统中的位置;状态转移图展示了系统状态在控制信号作用下的转换过程;而编程则是根据系统图和状态转移图,使用VHDL语言描述系统的状态运动、输出过程。在编程过程中,这三步都要具备。通常对FSM的编程方式有单进程、双进程和三进程模式。其中三进程模式易于理解,方便编程控制,且编程过程中条理清晰,易于查错。因此,在教学过程中,把三进程编程方式作为主要讲授内容。

状态图的设计方法在FSM的教学中也比较重要,课堂上我们以数字探测为例,讲授状态图的设计方法,以此启发学生理解状态转换过程及状态图的画法。通过上述教学策略,学生基本掌握了基于VHDL的FSM设计和编程方法,取得了良好的教学效果。

1 FSM的系统图和状态图

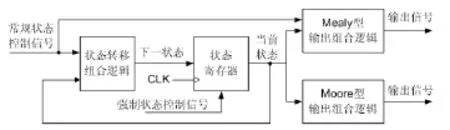

在讲授FSM之前,需要辨析FSM的系统图和状态图。系统图描述了数据流和控制流在FSM系统中的流动过程以及状态转移过程,是编写状态图和程序的基础。典型的FSM系统图如图1所示。

图1 典型FSM的系统图

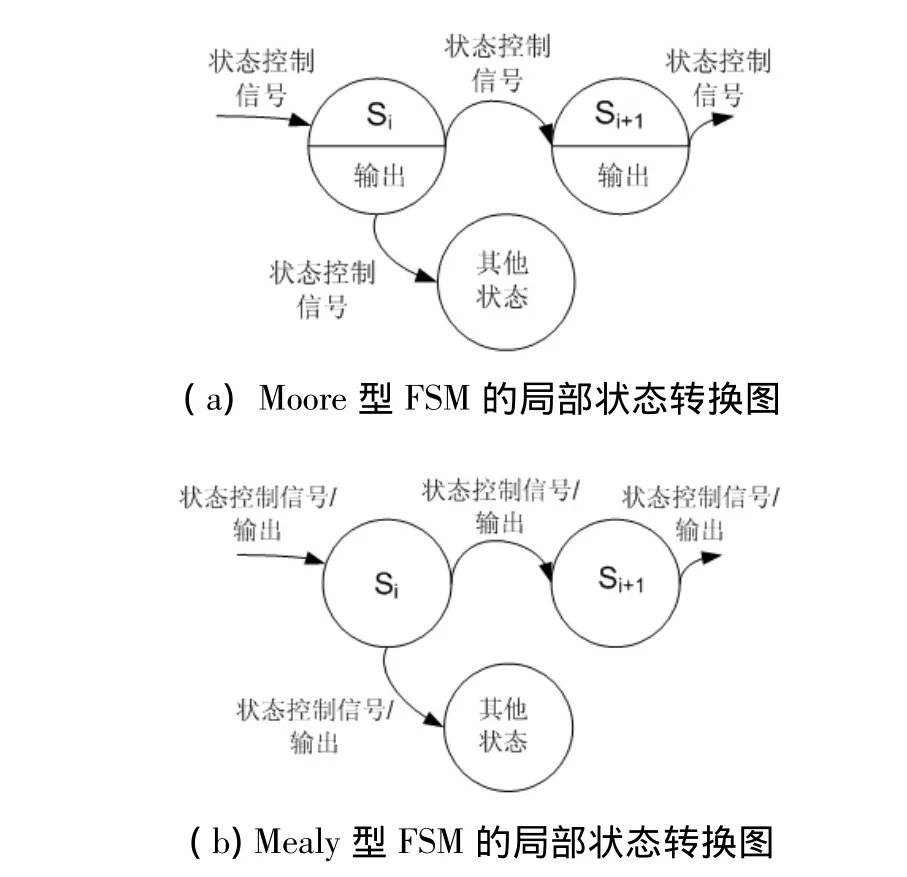

在讲授的过程中,一定要为学生讲清楚常规状态控制信号和强制状态控制信号。所谓常规状态控制信号,即是不同状态转换过程中所公用的控制信号,而强制状态控制信号则是当该信号有效时,将当前状态直接控制到固定的状态,如复位、使能等。状态图则是在控制信号作用下为实现该系统功能而设计的状态转换过程,以及输入输出关系。在Moore型FSM中,其输出信号仅与当前状态有关系,因此每个状态对应一个确定的输出;而在Mealy型FSM中,其输出信号不仅和当前状态有关系,而且还与当前输入的常规状态控制信号有关系。不同类型FSM的状态转移图画法亦不相同。图2(a)和(b)分别表示了Moore型FSM和Mealy型FSM的两个状态之间的局部状态转移图。

图2 FSM的局部状态转换图示例

2 编程方法

2.1 三段式编程框架

系统图、状态转移图和VHDL编码组成三段式编程框架。首先画出如图1所示的系统框图,其上准确标示出常规状态控制信号和强制状态控制信号。常规状态控制信号作为状态转移组合逻辑的输入端,强制状态控制信号作为状态寄存器的输入端。其次根据状态控制信号画出状态转换图,最后根据状态转换图写出VHDL代码。

在FSM编程过程中,将状态控制信号分为常规和强制两类信号是非常必要的,它更符合电路设计过程中各功能模块“相互独立、各尽其责”的思想,避免电路设计复杂和串扰。从电路类型来讲,强制状态控制信号起作用后状态输出是固定的,而常规状态控制信号起作用后其状态输出还需要当前状态共同决定,因此是有记忆的。因此,在理论和实践上,将这两类信号分开,不仅有助于概念上的理解,还有助于程序的编写。

FSM的编程方法分单进程、双进程和三进程三种。单进程将整个系统图放在一个process里面描述;双进程一般是将状态转移和状态寄存器放在一个进程,而将输出进程单独实现;而三进程描述方法则是将三个模块分别描述,不同进程之间使用状态信号相互通信。一般而言,单进程和双进程在状态控制信号比较少时,编程比较方便,但在控制信号较多时,不易调试。因此我们推荐学生使用三进程的编程方法。

2.2 Moore型FSM设计示例

教学过程中,我们以数字序列中的“10”信号检测为例为学生讲解状态机的设计原理,以此为基础,使学生了解状态转换与控制信号之间的设计关系。设输入信号为din,复位信号为reset,当从串行输入序列din中检测到“10”时,输出信号dout<=‘1’,否则dout<=‘0’,复位信号reset=‘0’时有效。

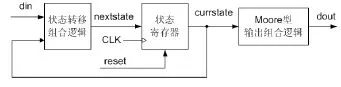

根据输入、输出信号,画出其系统图,如图3所示。

图3 “10”检测器的系统图

这里reset为强制状态转移信号,即当该信号为‘0’时,强制转换到初始状态;din为常规状态控制信号,即在不同的状态下,当din为不同的值时,下一个状态亦不相同。

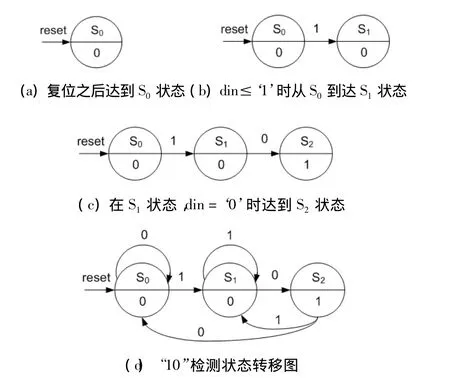

授课时Moore型FSM状态转换图的逐步引导过程如下。首先画出主状态转移过程。设初始状态为S0,则reset有效后,直接进入S0状态,输出为‘0’,如图4(a)所示。当din=‘1’时,则跳转到下一个状态S1,输出为0,如图4(b)所示。在S1状态之下,当din=‘0’时,状态跳转到S2状态,输出为1,如图4(c)所示,此时完成了主状态转移过程。然后,对每一个状态,根据检测要求画出在不同din条件下的状态转移过程,称为辅状态转移过程。首先看S0状态,在该状态下din=‘0’时,由于没有‘1’出现,直接在该状态停滞,直到有din=‘1’出现,才转移到下一状态S1。在S1状态,如果din=‘1’,则停滞在该状态,直到din=‘0’出现,才转移到下一状态S2。此时已经探测到“10”,输出置为“1”。在S2状态,若din=‘0’,则等待检测下一个“10”,从而跳转到S0状态;若din=‘1’,则等待din=‘0’的出现,从而跳转到S1状态,完整的状态转移图如图4(d)所示。

下面讲授三进程的编写方法。注意,要跟学生讲明的是,并行信号赋值语句实际上是隐式进程。

1)写出程序实体

Library ieee;

Use ieee.std_logic_1164.all;

Entity detector10 is

图4 Moore型FSM“10”检测器状态转移图的绘制过程

Port(din,clk,reset:in std_logic;

Dout:out std_logic));

End detector10;

2)描写程序中用到的状态及信号,并写出主题框架:

Architecture behave of detector10 is Type state is(s0,s1,s2);

Signal currstate,nextstate:state;Begin

状态转移进程(din,currstate);

状态寄存进程(clk,reset);

输出进程(currstate);

End behave;

3)根据状态转换图编写状态转移进程。这里使用case语句结合if_then_else语句实现,一个具体的例子如下:

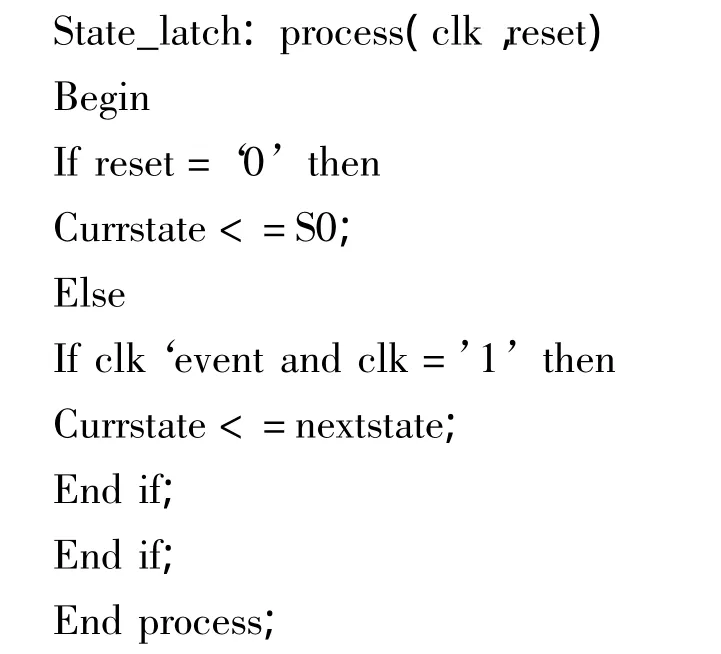

4)编写状态寄存进程,这里使用异步复位,实现如下:

5)编写输出进程。该进程中,只有当前状态currstate=S2时输出dout=‘1’,其他状态全为‘0’,因此可使用选择信号赋值语句实现,示例如下:

With currstate select dout>=‘1’when S2 else‘0’when others;将上述语句放在同一个architecture之内,即可实现“10”检测器。

2.3 Mealy型FSM设计示例

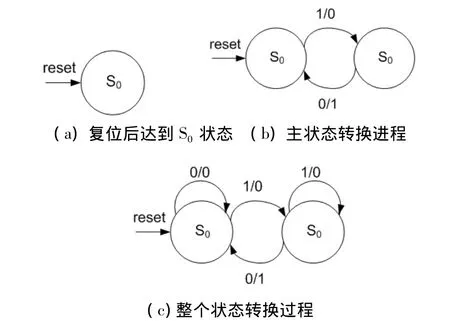

对于“10”检测器,其Mealy型FSM的系统图与图3类似,只不过输出组合逻辑输入端多了din。其状态转移图设计过程如下。Reset信号复位后,进入S0状态,如图5(a)所示。

图5 Mealy型FSM“10”检测器状态转移图的绘制过程

在S0状态,若din=‘1’,则进入S1状态,同时,输出为‘0’。在S1状态,若din=‘0’,则进入S0状态,同时输出为‘1’,实现了主状态转移过程,如图5(b)。最后画出辅状态转移进程,最终状态转移图如图5(c)所示。

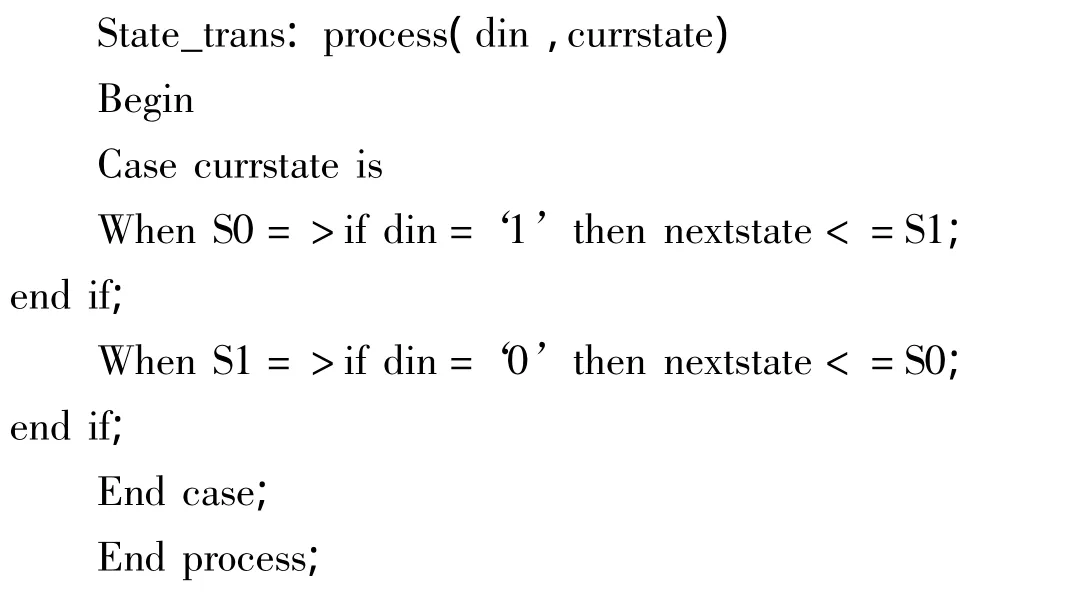

从图5可见,实现同样的功能,Mealy型FSM比Moore型FSM少一个状态,因此描述起来相对简单。对于Mealy型FSM,其状态转移进程可写为

由于输出与当前状态和当前输入有关,因此输出可写为:

Dout<=‘1’when currstate=S1 and din=‘0’else‘0’;

在“10”状态机的设计基础上,我们引导学生练习“10”,“11”,“00”状态机的画法,并进一步拓展到三位码的检测电路设计中,例如“110”,“101”检测等。学生经过思考后都能准确画出所要求的状态转移图。

3 效果评估

在我国高校电子类本科专业中,“可编程器件原理与实践”通常作为一门专业选修课,虽然教师在课堂上强调了该门课的重要性,但学生由于对该领域内的应用了解有限,且缺乏工作经验,因此难以引起学生的重视。再加上刚开始讲课时很多概念陌生,学生难以理解而容易失去学习兴趣。在该课程的教学过程中,我们采用实验、课堂相结合的方法来逐步培养学生的学习兴趣,获得很好的效果。

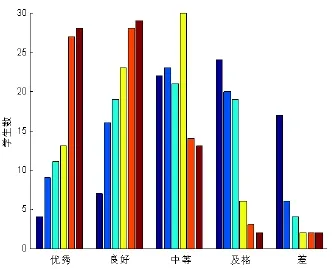

在教学过程中,我们共设计了6次实验,由简单到复杂,由基础到应用逐步深入。根据实验情况和实验报告,成绩按照优秀、良好、中等、及格、差五个档次划分。由于一开始学生对Altera Quartus II开发环境不熟悉,因此成绩较差。但随着课堂和实验的逐步深入,实验成绩便逐步提升,其统计图如图6所示。FSM实验是第5次实验,从该图中可以看出,在FSM实验之后,优秀和良好率有了大幅的增长,这说明学生对VHDL编程有了更深的认识和理解。

图6 实验成绩统计

另外,在课程所布置的作业中,我们发现学生设计的程序明显突出了模块化的设计思维,程序设计思路更加清晰,程序更加易读,说明“相互独立、各尽其责”的思想已经初步被学生所接受,并理解消化,提高了学生的学习兴趣,编程能力得到逐步提高。

4 结语

本文基于三段式方法总结了VHDL语言教学中的FSM编程方法,即将设计过程分为系统图、状态图和编程三部分,并以信号检测为例讲述Moore型和Mealy型FSM状态转换图的画法,在此基础上讲述了程序设计过程。通过这种教学方法,可使学生分清强制控制信号和常规控制信号,并为这些信号找到合适的位置,从而使编程过程有条不紊,正确实现所要求的功能。

[1] 梁妙元,马宁,朱福萌,段黎明,印敏.本科编程类课程教学改革探讨[J] .南京:电气电子教学学报,2015,37(1):35-36

[2] 罗杰,张林,谢世辉.可编程逻辑器件的教学实践与思考[J] .南京:电气电子教学学报,2000,22(2):32-38

[3] Stephen Brown.Fundamentals of digital logic with VHDL design[M] .New York:McGraw Hill,2009

[4] William Kleitz.Digital Electronics:a practical approach with VHDL[M] .New York:Pearson,2011

[5] 程云长.可编程逻辑器件与VHDL语言[M] .北京:科学出版社,2005年5月

[6] 文汉云.数字逻辑与数字系统设计-基于VHDL语言描述[M] .北京:清华大学出版社,2012年3月

[7] 边计年,薛宏熙译,Stefan Sjoholm,Lennart Lindh著.用VHDL设计电子线路[M] .北京:清华大学出版社,2000年4月