基于FPGA的模拟视频采集卡设计

王一程,陶会锋,杨铭博

(1.红外与低温等离子体安徽省重点实验室,脉冲功率激光技术国家重点实验室,电子工程学院,合肥 230037;2.解放军71146部队,潍坊 261000)

基于FPGA的模拟视频采集卡设计

王一程1,陶会锋1,杨铭博2

(1.红外与低温等离子体安徽省重点实验室,脉冲功率激光技术国家重点实验室,电子工程学院,合肥 230037;2.解放军71146部队,潍坊261000)

0 引言

视频技术在现代生活中有着十分广泛的应用,而视频采集是所有视频后续处理的基础。视频采集主要包含A/D转换和视频解码两个过程。A/D转换即模拟视频的数字化,视频解码是指将PAL或NTSC等模拟视频信号转换成8位ITU-R BT.656格式[1]。视频采集质量的好坏将直接影响整个视频系统的性能,是进行后续数字图像处理的前提条件。

FPGA(现场可编程门阵列)既有用户可编程特性,又能为设计者提供比DSP更高的并行性[2],特别适用于数据流量大数字视频处理。因此,FPGA在视频处理产品中的应用越来越广泛。目前市场上的有很多不同型号的视频采集卡,但大多都是采用PCI总线接口或USB等串行总线接口,视频数据经过很多传输流程,无法直接传入FPGA进行高速处理。因此,本文涉及的系统采用FPGA直接读写视频解码芯片的方案,FPGA直接获取BT.656格式的视频数据流。由于FPGA具有并行处理结构和高速处理速度,使整个系统的具备很高的处理性能。

1 系统硬件设计

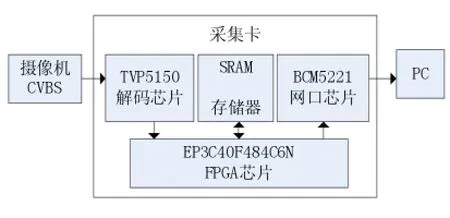

本设计以Altera公司的Cyclone III系列FPGA芯片EP3C40F484C6N为处理核心,可分为视频解码模块、视频存储模块和视频传输模块,如图1所示。

图1 系统硬件方案

在视频解码模块中,采用TI公司的TVP5150作为视频解码芯片。TVP5150将PAL或NTSC等制式的模拟视频信号转换为符合BT.656标准的数字信号,输入FPGA进行处理。视频存储模块为FPGA内部配置生成的FIFO和外部挂接的SRAM,可以将图像数据存入其中。视频传输模块通过百兆以太网接口芯片BCM5221将图像数据上传到PC,PC上运行的上位机程序显示采集到的视频,以验证采集系统的性能。本文主要讨论视频解码模块。

TVP5150是一款能够兼容NTSC/PAL/SECAM三种制式的高性能视频解码芯片,具有超低功耗(115mW)和超小封装(32pin TQFP)的特点,特别适用于便携视频应用[3]。模拟视频输入可以是2路CVBS(复合视频)信号或1路S-Video信号,输出为符合ITU-R BT.656标准的8位4:2:2数字视频信号。它与主控芯片FPGA之间通过I2C串行总线连接,FPGA通过设置TVP5150的内部寄存器对其进行配置和控制。

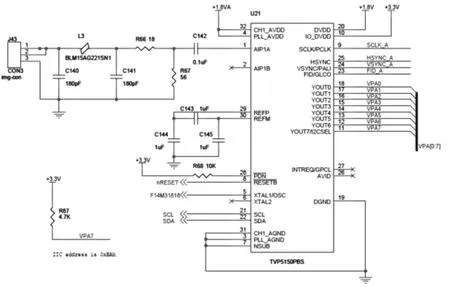

视频解码模块电路如图2所示。TVP5150芯片的系统时钟为14.31818 MHz;电源电压有1.8V和3.3V两种,1.8V为数字和模拟输入电压,3.3V为I/O口电压;模拟视频信号输入有A1P1A和A1P1B两路,图中接入第1管脚A1P1A;数字视频输出信号端口YOUT [7:0]为8位宽度的YCbCr信号,消隐信号可用单独引脚HSYNC和VSYNC输出;SCL和SDA为其与FPGA通信的 I2C总线端口。将 YOUT[0:7]、SCL、SDA、HSYNC、VSYNC与FPGA连接。

图2 视频解码模块电路

2 系统软件设计

本系统软件是在Quartus II环境下采用VHDL语言开发完成的FPGA配置程序。其功能主要包括对视频解码芯片的初始化配置和采集控制、数字视频数据的存储、网口芯片的配置和数据传输等功能,这里主要介绍视频解码芯片的初始化配置和采集控制。

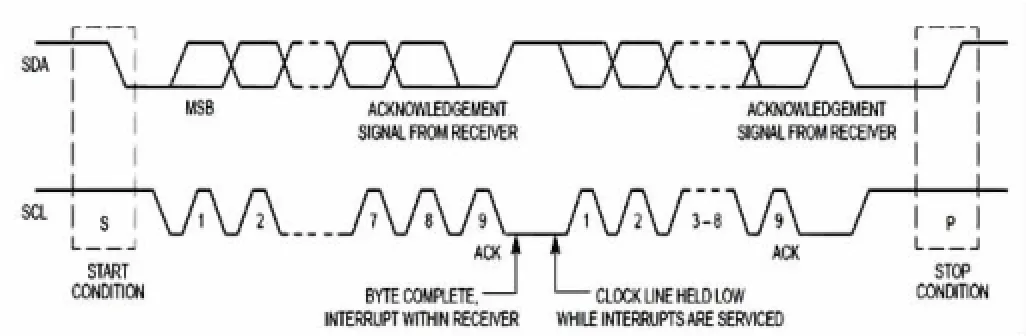

2.1I2C总线控制器

视频解码芯片TVP5150配有I2C总线接口,它的配置和控制是由FPGA通过I2C总线来完成。因此,需在FPGA内部设计生成一个I2C总线控制器,以实现I2C总线时序。I2C总线为两线制,由数据线SDA和时钟线SCL构成,可发送和接收数据。

I2C总线是同步传输的串行总线,总线信号由时钟进行同步。为了保证总线数据的可靠传输,I2C协议对总线时序做了严格的规定,如图3所示,传输数据时有起始位(S),终止位(P),发送零及应答位(A),发送l及非应答位(A)[4]。特别要注意起始和停止的条件,起始条件是SCL为高电平时SDA下降沿;而停止条件是SCL为高电平时SDA上升沿;起始位和终止位之间的数据的每一位传输都是必须在SCL为高电平时完成。

图3 I2C总线时序图

2.2BT.656数据处理

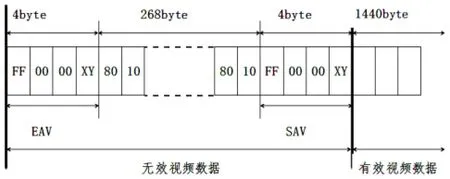

在BT.656标准中,8位宽度的并行接口除了传输4:2:2的YCbCr视频数据流外,还包含行、列同步所用的控制信号。在视频数据流中,一帧图像数据为包含一个625行、每行l728个字节的数据块。其中,第23~311行是偶场视频数据,第336~624行是奇场视频数据,其余的行为垂直控制信号。数据流包括视频信号、时基信号、辅助信号三个分量[4]。数据的归属由时基信号区分,它包括SAV(有效视频起始)和EAV(有效视频结束),分别表示行的开始和结束,由4字节的16进制数组成,用FF、00、00、XY表示。其中,FF、00、00为SAV 和EAV的前导字节,XY为时基信号的信息位。SAV信号后为1440个YCbCr 4∶2∶2格式的有效数据,编码格式如图4所示。

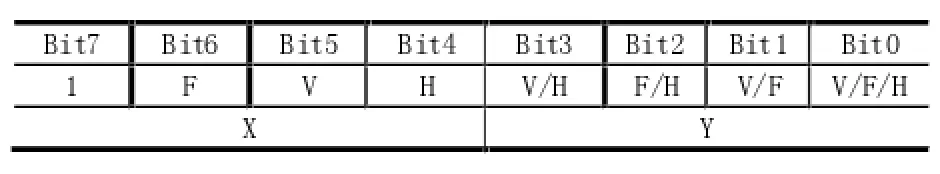

如表1所示,XY字节的最高位Bit7为1;F=0表示偶场数据,F=1表示奇场数据;V=0表示该行为有效视频数据;V=1表示该行为辅助数据;H=0表示SAV信号,H=1表示EAV信号。

图4 BT.656的行数据结构

表1 XY的含义

根据BT.656数据结构规定,帧数据块中包含有效视频数据和无效视频数据(同步和消隐信号),FPGA只需要缓存有效数据。程序可以利用时基信号EAV、SAV产生控制信号去除帧数据块中的无效数据。首先在输入的数据流中检测是否含有三个前导字节FF、FF、00,若检出这三个字节的数据就可能是有效数据的开始或者结束。当判断到SAV信号后,就可以开始接收有效数据,直到出现EAV信号。在接收有效数据时,必须严格按照从偶场第一行开始,直到接收完完整一帧的数据,否则可能会发生丢失数据等异常现象,这样做能够简化程序。当接收满一帧后就存入FPGA的内部FIFO或外部SRAM中进行缓存,等待处理器进行处理或上传。

3 实验结果

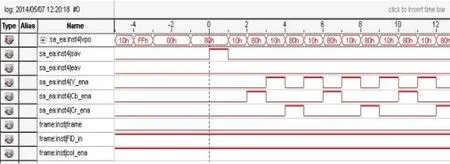

将程序通过JTAG方式下载到FPGA后,利用QuartusⅡ软件自带的Signal TapⅡ逻辑分析仪来对FPGA内部信号进行观察。为了捕获SAV信号,可将Signal TapⅡ中的触发使能信号设为SAV,触发电平为SAV的上升沿。如图7所示,SAV信号被成功捕获,vpo [7:0]为FPGA通过I2C总线从视频解码芯片TVP5150获取的BT.656数据流。在SAV上升沿之前,vpo的值为FFh 00h 00h 80h,反而言之,当vpo出现FFh 00h 00h 80h序列时,则认为一个SAV的到来。为了方便分辨vpo中的Y、Cb和Cr数据,程序中加入 Y_ena、Cb_ena和Cr_ena信号。可见,Y、Cb和Cr数据是交替到来的。

图5 SAV信号

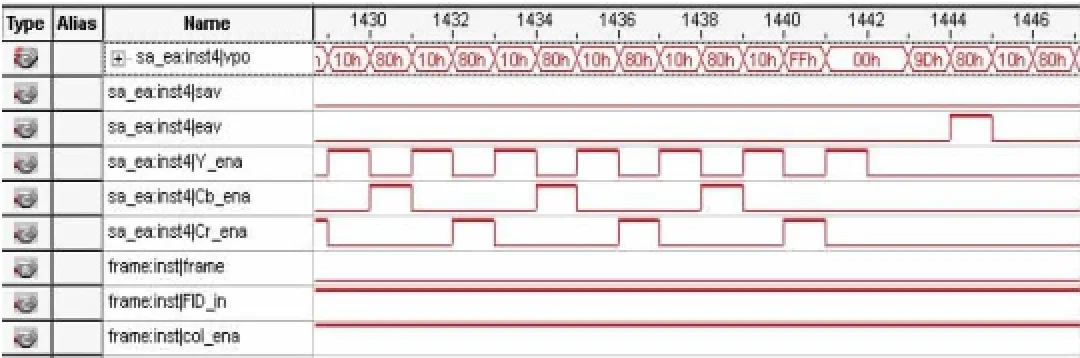

同样,为了捕获EAV信号,可将Signal TapⅡ中的触发使能信号设为EAV,触发电平为EAV的上升沿。如图6所示,EAV信号被成功捕获,在EAV上升沿之前,vpo的值为FFh 00h 00h 90h,反而言之,当vpo出现FFh 00h 00h 90h序列时,则认为一个EAV的到来。

图6 EAV信号

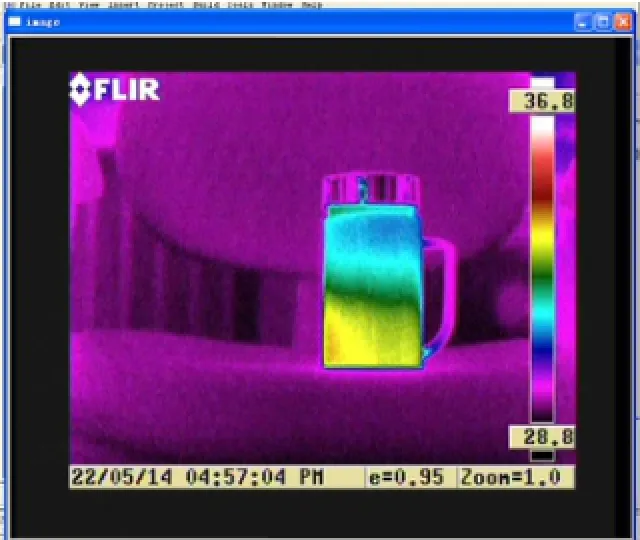

将摄像机输出的模拟视频接入采集卡,上位机通过网口与采集卡连接,上位机程序界面显示上传的数字视频信号。图7显示了采集卡所采集到的红外热像仪输出的视频,画面清晰流畅。

4 结语

本文介绍了一种以FPGA芯片为控制核心的模拟视频采集卡的设计方法。FPGA通过I2C串行总线对视频解码器TVP5150进行配置,然后获得BT.656格式的视频数据,最后通过实验验证了设计的有效性。

图9 上位机程序显示的视频画面

[1]赵鸿章.数字视频处理[M].北京:北京师范大学出版社,2009.

[2]王一程,汪海兵.基于FPGA的光电跟踪控制系统设计[J].电光与控制,2009,16(3):54-57.

[3]蒋陈铭,史小军.基于TVP5150的低功耗视频解码模块[J].电子工程师,2008,34(4):46-48.

[4]陈秀玲,周欣.I2C总线数据传输系统的设计及其应用[J].微型电脑应用,2003,19(5):42-44.

[5]仁帅,陈铎.基于FPGA的TVP5150的视频解码模块[J].科技创新导报,2014,(6):61.

FPGA;Video Capture;TVP5150;BT.656

Design of Analog Video Capture System Based on FPGA

WANG Yi-cheng1,TAO Hui-feng1,YANG Ming-bo2

(1.Key Laboratory of Infrared and Low Temperature Plasma of Anhui Province;State Key Laboratory of Pulsed Power Laser Technology,Electronic Engineering Institute,Hefei 230037;2.71146 PLA troops,Weifang 261000)

1007-1423(2015)33-0047-04

10.3969/j.issn.1007-1423.2015.33.013

王一程(1983-),男,广西百色人,硕士,讲师,研究方向为图像处理、机器视觉、智能控制

2015-11-10

2015-11-20

模拟视频信号采集是视频处理系统的重要部分,为后续数字视频信号的处理打下基础。为了提高视频采集和处理的实时性,设计一种基于FPGA芯片的视频采集卡。该采集卡以Cyclone III系列FPGA芯片为核心,通过视频解码芯片TVP5150将模拟视频信号转换为符合BT.656标准的数字信号,输入FPGA进行处理。实验表明该方案的有效性,能为同类产品的设计提供参考。

FPGA;视频采集;TVP5150;BT.656

陶会锋(1988),男,河北邯郸人,硕士研究生,研究方向为光电工程

Analog video signal acquisition is an important part of the video processing system,and it is the basis for the subsequent processing of digital video signals.In order to improve the real-time performance of video capture and processing,designs a video capture card based on FPGA chip.With a Cyclone III series FPGA chip as the core,this card converts the analog video signal into digital signal which is in accordance with BT.656 standard by the video decoder chip TVP5150.And digital video data are transferred into FPGA chip for subsequent processing.Experimental results show the effectiveness of the scheme,which can provide reference for the design of similar products.