基于NOC技术的多核研究

赵宝功,徐玉洁,屈凌翔

(中国电子科技集团公司第58研究所 ,江苏 无锡,214035)

1 引言

随着微电子计算技术的发展,超大规模集成电路的集成度越来越高,片上系统(SOC)总线结构的弊端逐渐暴露出来,物理连接、单一时钟引起的时钟延迟等问题,制约了SOC系统的进一步发展。在1999年,以瑞典皇家理工学院为代表的学术机构提出了新型的通讯架构——NOC[1],这种设计把通信网络概念结合到集成电路设计中,每个计算单元模块都是片上网络的一个路由节点。而在传统的SOC设计中,都是采用总线架构将各个模块连接起来并且使用一个统一时钟。在SOC系统集成度低的情况下这个方案还是可行的,但是随着集成度的不断提高,SOC系统受到严重的时钟延迟和偏移影响,这给设计者带来极大的挑战,片上网络(NOC)彻底地解决了这个问题,NOC系统采用一种分布式网络结构,它们没有统一时钟,各个计算单元通过路由器连接,各自可以完全独立工作。为了减低功耗本文通过改进现有的2D MESH架构,设计了其中一个节点作为主控核,控制从核以及路由的时钟和复位,对于工作过程中不使用的节点,节点时钟不打开,达到降低功耗的目的。

2 片上网络结构种类及原理

目前片上网络的种类有网格型拓扑结构、环绕型拓扑结构、环型拓扑结构[1,2,8],树型拓扑结构,选择合适的NOC网络拓扑结构对NOC设计非常重要,目前阶段NOC的研究大部分借鉴了并行计算机体系结构中的静态网络结构,各种拓扑结构各有各的优势,目前比较多的研究机构采用了2D MESH 结构,2D MESH结构显著的特点是路由的编码简单[11],结构简洁,目前商用的片上网络架构多是采用2D MESH。

片上网络核心思想是将计算机宏观网络技术移植到芯片设计中来,从体系结构上解决总线架构带来的问题。片上网络原理就是在芯片上搭建网络,用网络的方式把各个IP核联系在一起,各个IP核之间通过报文方式实现数据交互。

3 NOC 设计与实现

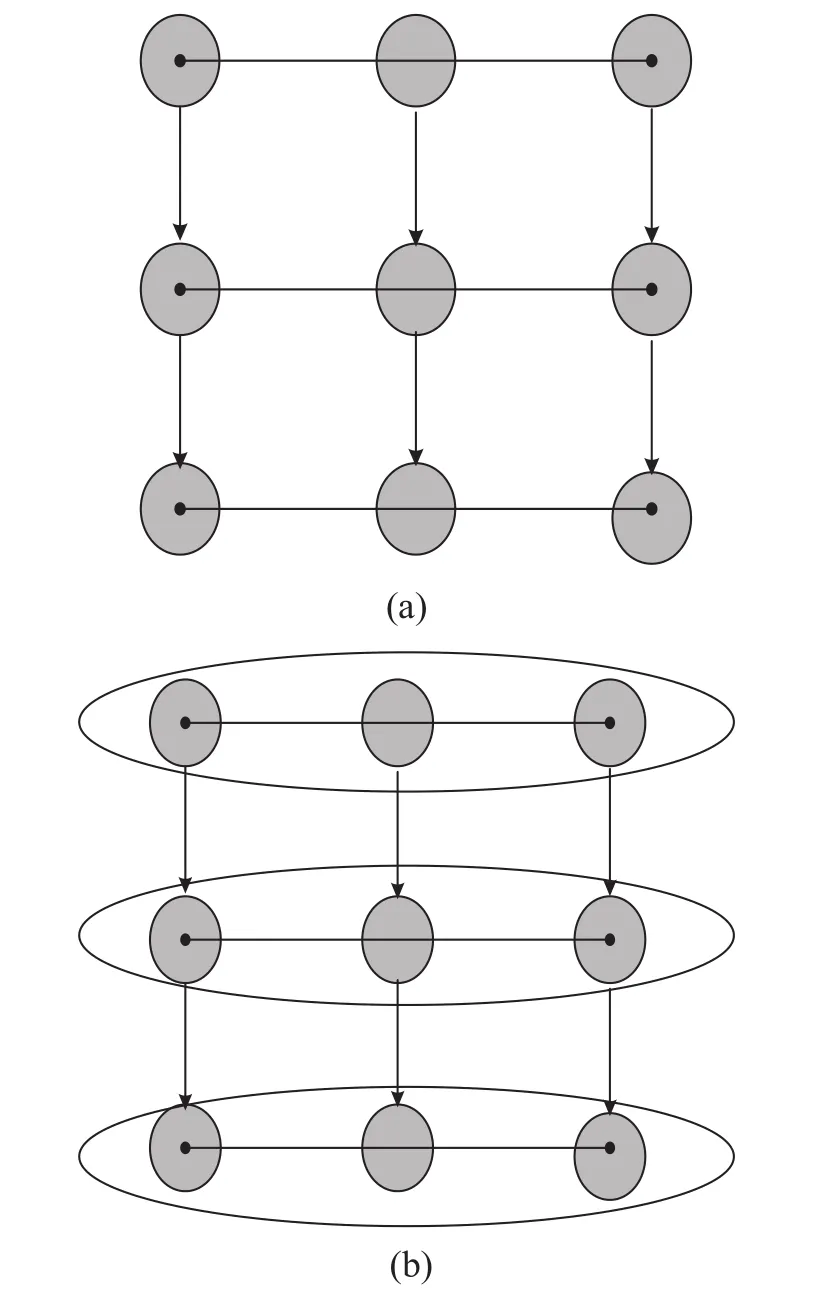

NOC 结构是采用二维MESH_3×3网络结构(如图1),片上网络架构主要由计算单元、网络接口(NI)、路由器(R)组成[3],处理单元分为主控单元、从单元,计算单元主要为IP内核,这里采用高性能DSP内核,处理单元通过局部总线访问私有存储器,通过网络接口访问共享存储器。处理单元(如图1左上角)为主控核控制其他处理单元的时钟以及复位等。整个系统的存储空间统一编址,每个核都可以访问其他核的存储空间,这样所有计算单元可以共享所有存储器。

图1 NOC平台

3.1 路由器设计

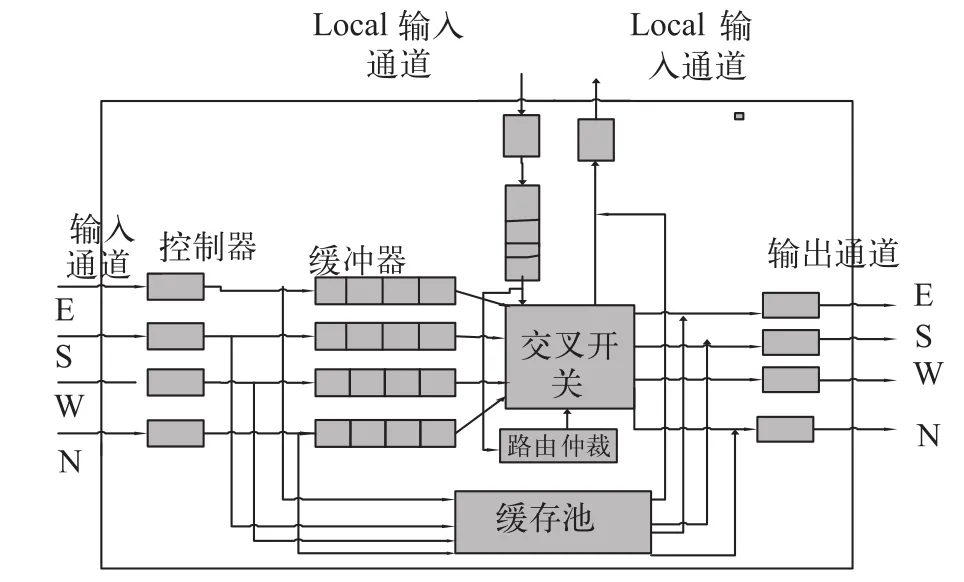

路由器主要功能是根据源节点数据发送端和目的节点数据接收端的网络地址信息,按照一定的路由算法选择最佳的路径,实现数据的通讯。路由器的核心模块是路由仲裁器,它根据路由算法,通过交叉开关分配路径为数据选择其输出端口,当数据进入路由时,先将数据存储在缓存器中,根据数据的头包解析,向路由的仲裁器申请仲裁选择,当输入数据申请获得仲裁时路由分配链路,让数据通过路由[5,6,9,10]。

图2 路由器示意图

路由有 5个双向端口,分别为北(north)、东(east)、南(south)、西(west)和本地端口(local)。每个端口都有输入数据、控制信号通道和输出数据控制信号通道,local端口和本地的计算单元连接,其余连接其他方向的路由器。路由节点内部采用队列缓存方式缓存分组数据,输入通道由两个虚拟通道构成,实现了分组数据的缓存,并且为每个分组数据选择输出端口;虚拟通道分配模块根据相邻节点输入通道的虚通道状态,为输出端口的分组数据分配虚拟通道;仲裁模块控制开关电路的选通,连接输入输出端口,为了提高重用性,我们采用相同的输入输出端口连接路由器和IP,其中IP通过网络接口来实现与路由之间的数据转换,路由器示意图如图2,路由器算法采用xy 维序算法,先沿着x轴方向寻找目的地址,然后在y轴方向轮转仲裁机制,xy维序算法是典型的确定性路由算法。这个算法实现起来比较容易,路由的效率比较高,不会死锁,算法的伪代码如下:

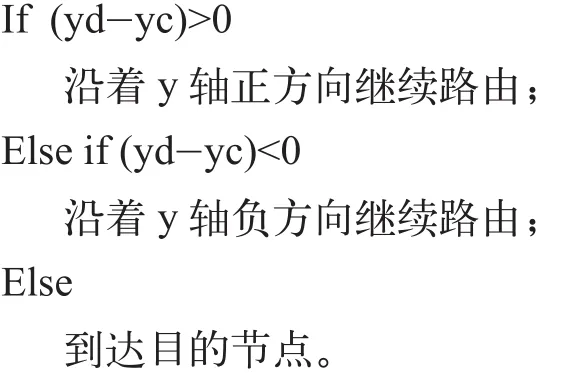

假设(xd ,yd)为目的节点坐标,(xc ,yc )为当前节点坐标[4],

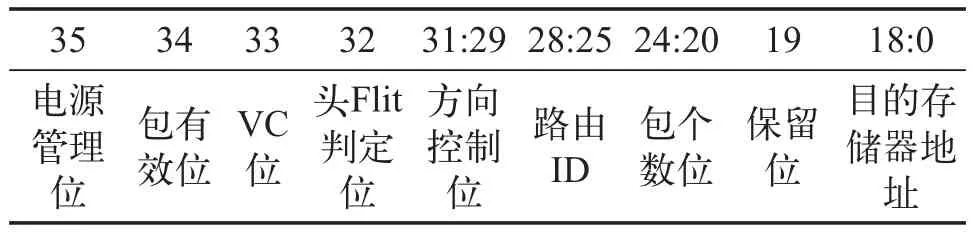

在片上网络中传输数据的基本传输单元为数据包,每个数据包又分为头Flit[2]和数据Flit,它们都有相同的数据位宽,在通信协议中头Flit包含通讯协议中的各项信息,包括电源管理、vc位、方向控制、目的计算节点地址、源计算节点地址、包长、包有效位等,这些信息将在网络接口中被打包发送到路由器中,并在路由中被解析,根据头f l it信息把数据包转发到对应的输出端口上。实际应用协议内容被放在数据Flit中,Packet有两种结构,分别是头Flit和数据Flit,如表1和表2。

表1 头Flit格式

表2 数据Flit格式

网络接口将AHB总线的数据和地址格式转化为Router能识别的Packet格式,Packet结构如表1、表2,头Flit主要包含标志位、控制信息和目的存储器地址信息;数据Flit主要用来存储需要传输的数据。

3.2 网络接口设计

片上网络接口用于连接IP模块与片上网络,是NOC架构中的重要组成部分。网络接口主要负责资源节点与路由之间进行总线结构到网络结构的协议转换,主要分为两个步骤:存储计算单元模块发送的数据并将其封装打包便于NOC通讯架构中传输;存储从通讯架构传输到达目的IP 模块的数据,在网络接口中将数据包拆分得到有效数据并发送到IP模块。另外在网络接口根据接收部分状态,当数据接收完成后网络接口向计算单元发送中断信号。

网络接口实现数据包的打包和拆包都要通过状态机来控制实现[7~11],网络接口在实现总线结构到网络片上网络结构的协议转换过程中需要暂存数据,同时为了实现片上网络架构局部同步全局异步的功能特点,网络接口还要有FIFO对数据进行暂存以便于对数据包封装、拆分和转发。

发送通道工作流程如下:

(1)配置网络接口中寄存器;

(2)从相应的寄存器中读取包头的有效载荷,形成包头并发送出去;

(3)识别并读取数据包的有效载荷,形成包实体并发送出去;

(4)识别并读取尾包的有效载荷,形成尾包并发送出去。

接收通道写入FIFO的操作是在接收来自片上网络的数据进行的,同时并不是所有接收来的数据都写入FIFO。在接收数据过程中,首先被接收的是头包,头包中包含了电源管理位、有效位、VC位、头Flit位、目的地址位、方向位等,当数据包达到目的节点时,头包已经没有意义,不被送到IP核,只有数据包及尾包有效才会被写入到FIFO中暂存,接收通道的工作流程如下:

(1)头包的识别过程,该过程结束后启动下一过程;

(2)数据包和尾包有效荷载的抽取并写入到FIFO中,当数据写完后将会触发中断请求事件的发生。

图3 网络接口示意图

4 功能验证

目前的仿真是基于MESH 3×3搭建的RTL系统验证平台,使用core0节点作为主控核,控制其他计算单元的时钟和复位,当计算单元不工作的时候可以把对应的计算单元、时钟关掉,这样可以降低功耗。这里使用nc仿真器,仿真计算节点之间的数据通讯。首先配置下网络接口中的寄存器,然后让计算节点向网络接口发送数据,在网络接口中数据被打包发送到指定的计算节点(见图3),数据从core8经过17个周期后到达core7,并把数据送到指定的存储空间上,在实际应用时尽量先分配好任务,把要处理的计算任务改为并行处理任务映射到各个计算单元,优化数据传输路径,降低数据传输的延迟,提供网络运行效率。

图4 仿真结果

5 多核系统的实际应用

为了充分利用多核性能,设计了流水矩阵乘法,在此应用中每个从核接点都有个本地N维矩阵。具体通过设计并行程序来实现,具体过程如下。

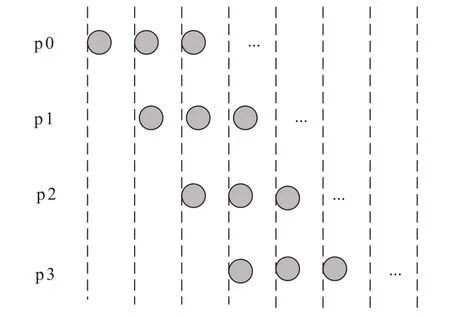

首先将任务分解,把一次矩阵运算作为一个子任务,将多组矩阵乘法运算分解为多个有数据依赖关系的子任务,如图5(a)所示,图中圆圈代表一次矩阵乘法运算,纵向代表一组矩阵连乘的过程。

图5 多组矩阵连乘的依赖关系和并发性

根据如图5(a)的分解方法,按照乘法步骤进行分配,将连乘分为4步,给每一步编上一个号,把编号相同的分配到同一个进程中,如图5(b)所示,这样的分配方式既能考察核的计算能力,也能考察通讯能力。

图6 流水方式的并行计算时序图

其次协调与映射,使用图5(b)的分配方法,按照进程与处理器一一对应的映射方法将3个进程映射到4个处理器上,使用流水方式执行。图6使用流水方式的并行计算时序图,图中横方向表示时间,纵方向表示某一时刻的事件,p0、p1、p2、p3为4个处理器,首先在p0上执行第一组连乘的第一运算,把结果发送给p1;p1进行第二步计算,把结果发送给下一个处理器,在这个过程中,p0完成第一组连乘后接着完成第二组连乘的第一步,其他处理器类似,每个处理器只负责连乘的一个步骤,这样处理器构成并行流水线工作,协调完成连乘任务。

6 结束语

随着无人机、声纳、雷达、信号情报以及软件无线电等波形密集型应用中信号处理需求的不断提高,多个数字信号处理器内核的使用已经成为重要的实现手段,多核数字信号处理器能够满足关键的任务需求,包括更强大的处理速度、更精细的分辨率、更高的精度,过去靠工艺升级,提高主频来实现越来越遇到瓶颈。

本文通过NOC拓扑结构实现了多核芯片,计算单元之间可以通过router进行数据交换。2D MESH拓扑架构具有功能简单、扩展性强等特点,对解决未来多核芯片的需求具有重要意义,NOC架构将成为大规模多核芯片的发展方向。

[1]段宜宾,王晓冬,唐磊. 片上网络关键技术及仿真方法研究[J]. 通信技术,2009,42(12).

[2]丁帅,吴宁,葛芬,王祺. 片上网络路由单元的系统级建模研究[J]. 微电子学与计算机,2009,26 (1).

[3]谭耀东,刘有耀. NOC系统研究综述[J]. 西安邮电学院学报,2008,13(1).

[4]姚放吾,高 莉. 一种改进的二维MESH结构片上网络拓扑[J]. 计算机计算与发展,2009,19(7).

[5]谢晓燕,蒋林. 基于电路交换的NOC路由器设计与实现[J].

[6]刘炎炎. 基于FPGA的NOC的通讯架构的设计与测试[D].合肥工业大学硕士学位论文,2011.

[7]杨盛光,李丽,张宇昂,王佳文,董岚,高明伦. 多处理器NOC仿真平台[J]. 系统仿真学报,2009,21(19).

[8]李忠琦,凌翔,胡剑浩. 片上网络系统网络层设计与研究[J]. 中国集成电路.

[9]万玉鹏,吴宁. NOC路由单元的系统级设计[J]. 2009, 22(2).

[10]Shashi KumarAxel, Jantsch Juha-Pekka, Soininen Martti,Forsell Mikael Millberg. A Network on chip Architecture and design methodology computer SOC iety annual symposium[C]. VLSI 2002 IEEE.

[11]Mullins R, West A, Moore S. Low –latency virtual channel router for on chip network [C]. Proceedings of the 31stAnnual International Symposium on Computer Architecture germany Munchen ,2004.188-197.