基于VIRTEX架构的FPGA布线资源测试技术

王建超,陆 锋,张凯虹

(1. 江南大学物联网工程学院,江苏 无锡 214122;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

基于Virtex架构的FPGA的灵活性和编程能力强。基于Virtex 架构的 FPGA 由阵列式的可配置逻辑模块(CLB)、输入输出等模块组成。利用FPGA器件实现特定功能设计时,内部布线资源产生的延时将会对所设计的芯片速度产生很大的影响。基于Virtex架构的FPGA 器件中对路由资源和布局布线在同一过程中进行优化。这一优化过程减少了最大路径的延时,同时也提高了系统的速度[2]。

FPGA器件内部可编程布线资源所占的晶体管数量是所有模块中最多的,其故障发生率也是最高,因此对布线资源的测试是一个重要的研究领域。布线资源的测试是FPGA测试中的一个难点,一般的思路都是把众多的线段连成一条条总线,使用走步-l(walking-1)测试向量来测试,而使用BIST方法也层出不穷,这些方法达到了更少的编程次数和更高的覆盖率。通常为了减少配置次数,可编程布线资源采用把单长线和双长线的测试压缩到一起,以及手工连线的测试办法。本文对基于Virtex架构的FPGA布线资源采用通用方法的组合进行测试,从而对布线资源达到全覆盖测试。

2 布线资源故障模型

可编程布线资源存在着多种故障模型,这些故障模型是对各类器件失效方式的描述,每一种故障模型都会影响器件的正常工作。可编程布线资源是由可编程布线点和线段组成。因此布线资源的故障模型可以分为两类:线段的故障模型与可编程布线点的故障模型。它们的故障模型分别建立如下:

(1)线段的开路故障:金属线断开,不连续就会导致线的开路故障。

(2)线段的固定型故障:布线线短路到 VDD 或 GND将会导致线的固定1故障(SA-1)或固定0故障(SA-0)。

(3)线段的桥接故障:当电路中两根或两根以上不相连的线短接在一起并形成线逻辑时,对此缺陷用桥接故障(bridging fault)模型来描述。当桥接故障涉及的连线多于两条时,则称该故障为多重桥接故障。

(4)可编程开关的常开故障(stuck-on):常开故障会阻碍连接线间的信号传输。

(5)可编程开关的常闭故障(stuck-off):与常开故障相比,常闭故障并不会中断连接线间的连接,类似于桥接故障。

线段的固定型故障和开路故障都会造成传输信号的不连续,因此,这两种故障都可以用传输0和传输1的方法检测。线段的桥接故障可认为在线段搭接处短路,当使用连线传输相反逻辑时,可观察到故障,因此可以使用走步向量检测桥接故障;可编程开关的常开故障会中断信号的传输,那么可以观察信号是否正确传输检测该故障;对可编程开关常闭故障的检测,可以观察开关在两种工作状态下的输出情况以检测此故障。

3 故障检测方法

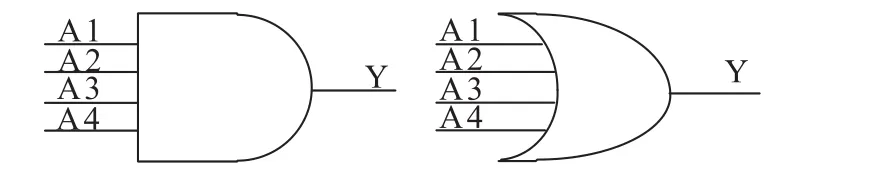

与门可以测得线上(S-A-0)的故障,或门可以测得(S-A-1)的故障。

图1 与、或故障测试

(1)与门测试方法:

把所有CLB中的LUT都设置为与门,xdl中将LUT的描述公式改为:

F:LUT4_inst[1]:#LUT:D=(A1×A2×A3×A4)

G:LUT4_inst[2]:#LUT:D=(A1×A2×A3×A4)

把每个slice的lut连接成每个slice作为8个输入F1、F2、F3、F4、G1、G2、G3、G4,输出给 X,Y。每 4个slice为一组,8输入为4个输入的公共输入端口并接入到SWB上,4个slice的x、y输出分别接到SWB的8端口上。XDL文件中用脚本处理,最终将8个输入端口和8个输出端分别接到IO上。将输入端口设置为高电平,观察输出端口的电平变化,如果输出端口输出低电平,则线上出现了固定0故障(SA-0)。

(2)或门测试方法:

把所有CLB中的LUT都设置为或门,xdl将LUT的描述公式改为:

F:LUT4_inst[1]:#LUT:D=(A1+A2+A3+A4)

G:LUT4_inst[2]:#LUT:D=(A1+A2+A3+A4)

然后重复与门测试步骤,最后把输入改为低电平,观察输出端口电平变化,如果输出端口输出高电平,则线上出现了固定1故障(SA-1)。6倍线和长线如上方法可以测得故障覆盖率。

4 布线资源的测试原理

基于Virtex架构的FPGA布线资源可分为4类,包括全局布线资源、长线资源、短线资源和分布式布线资源。全局布线资源用于电路内部全局时钟和全局复位/置位的布线;长线资源用以完成电路bank间的高速信号和第二全局时钟信号的布线;短线资源用以完成基本逻辑单元之间的逻辑互联和布线;分布式布线资源用于专有时钟、复位等控制信号线。

FPGA的通用测试和统计方法有几种。方法1:基于应用的布线资源测试,非确定性方法,适用于一般用户,难以达到较高的覆盖率;方法2:手动布线方法,确定性方法,适用于高级用户,完全采用该方法需要耗费大量的人力与时间,通常被用作方法1的补充;方法3:基于FPGA editor坐标图的脚本语言布线方法,确定性方法,适用于高级用户,可读性差,需要人工统计各PIP的坐标;方法4:基于xdl(Xilinx Design Language)语言的脚本语言布线方法,确定性方法,适用于高级用户,可读性好,需要xdl语言支持;方法5:基于配置文件的覆盖率统计方法,确定性方法,适用于FPGA设计人员,需要设计人员提供配置文件与FPGA各资源的对应关系;方法6:基于xdl语言的布线资源覆盖率统计算法,确定性方法,适用于高级用户,可读性好,需要xdl语言支持。

其中前4种为测试方法,后2种为统计方法。统计方法虽然不是测试方法,但是它既可以给用户提供直观的测试覆盖率,又可以指导测试人员设计有针对性的下一轮测试方案。本文对基于Virtex架构的FPGA布线资源采用上述几种方法的组合进行测试,从而对布线资源达到全覆盖测试。

4.1 Interconnect(PSM)之六长线

基于Virtex架构的FPGA其Interconnect(PSM)具有以下连接规则:(1)在同一方向(垂直方向或水平方向)两条紧挨着的单线可通过一个可编程开关(PS)相连接;(2)位于同一个布线通道中的两条十六进制线之间必然存在一个PS;(3)长线可以通过PSM与十六进制线相连接。总而言之,可以通过 PSM 使任意两条布线线段相连接。

相邻CLB间采用如图2的逻辑,4路输入信号构成8组输出,最终整个电路被配置为级数相等的移位寄存器链(由触发器与查找表构成),然后对六长线布线和六长线开关进行测试。

图2 六长线测试的CLB内部逻辑

采用中间六长线的隔3转向法进行测试,具体路径描述为:采用CLB的XQ/X/YQ/Y输出信号,经H6Ei输出;至RxCy+3后,转V6Si输出;至Rx+3Cy+3后,转V6Si输出;至Rx+3Cy后,转V6Ni输出;返回RxCy后,转单长线,输入RxCy+1的CLB之X/XQ/Y/YQ。

整体布局如图3,采用蛇形结构,从而避免了R1C48与R2C1布线资源的远距离连接,因为这种远距离连接需要利用六长线进行中转或者直接利用六长线进行连接。

然后撰写verilog程序,并进行rtl级仿真;撰写用户约束ucf程序(由perl语言程序产生);采用手动布线或者基于FPGA editor坐标图的脚本语言布线方法,给出从左至右的6根布线,与从右至左的6根布线对应的ncd文件;将上述ncd文件转换为xdl文件;依据xdl文件中的布线描述,撰写perl语言程序,修改ncd文件中的其它同规则布线;将修改后的xdl文件转换为ncd文件,并将其余没布线的连接关系,采用自动布线方式进行布线;依据修改后的ncd,产生布局布线后的门级仿真线网表,进行门级仿真;门级仿真无故障后,载入测试系统进行测试;撰写perl语言覆盖率统计程序,统计上述xdl程序的覆盖率,从而对六长线进行全覆盖测试。

图3 六长线测试整体布局图

4.2 Interconnect(PSM)之长线

采用长线与TBUF同时测试的方案,这样的做法可以降低测试向量的总体长度,对FPGA而言,还可以减少用于配置的时间总长度。但由于长线的输入/输出虽然有8种可能,但每次配置一旦确定1种可能,则其余7种不再允许输入/输出;所以测试水平长线,至少需要8段测试码。同理,测试竖直长线,需要6段测试码。由于水平长线与竖直长线可同时进行测试,所以长线测试总共需要8段测试码,实际配置后如图4。然后对长线布线和长线开关进行测试。

将用于测试TBUF的两根输入信号经OMUX连接长线,然后再绕回TBUF。以列为单位,逐列扫描,进行自测试,使长线资源测试达到全覆盖。

图4 长线测试布线图

图5 单长线测试整体布局图

4.3 单长线资源

将每个PSM对应的24根水平单长线分为3组,这样使得每组8根与OMUX输出的8根信号一一对应,从而确保布线与开关同时进行测试。

整体布局如图5,为了避免R1C48与R2C1布线资源的远距离连接,整体布局也是采用蛇形结构。

5 结束语

本文通过对基于Virtex架构FPGA布线资源的六长线、长线、单长线的测试技术研究,采用通用方法的组合进行测试,测试程序可读性好、可复用性高,对布线资源测试故障覆盖率高、故障定位准确。

[1]Ehsan A toof i an , Zainalabed in Navabi. A Test Approach for Look Up Table Based FPGAs [J]. Journal of Computer Science and Technology, 2006.

[2]Xilinx Data Book.Virtex-II Platform FPGA User Guide[Z].Xilinx Inc.November, 2007.

[3]Xilinx Data Book.Virtex-6 FPGA Configuration User Guide[Z]. Xilinx Inc.September, 2012.

[4]唐恒标,冯建华,等. 基于测试系统的FPGA逻辑资源的测试[J]. 微电子学,2006.

[5]李文昌,万理,等. 应用于Virtex系列FPGA的IR-CLB资源的联合测试和诊断[J]. 微电子学与计算机,2014(01):31.

[6]周涛. SRAM型FPGA的测试技术研究[D]. 成都:电子科技大学,2006. 5-7.