基于SM61864的GJB289A通信接口开发和应用

安百俊,吕 冰,李新民

(中航工业西安航空计算技术研究所,西安710068)

基于SM61864的GJB289A通信接口开发和应用

安百俊,吕 冰,李新民

(中航工业西安航空计算技术研究所,西安710068)

为满足GJB289A接口小型化、轻型化、低功耗、高可靠性和灵活性应用需求,设计一款采用SM320F2812作为智能处理器、SM61864芯片作为GJB289A控制芯片,采用FPGA实现主要逻辑的双余度双通道MBI。MBI能极大降低总线负载,提高总线传输效率。SM61864使得MBI具有BC、RT、Monitor、RTMT等功能。通过在线综合与联试,MBI模块能够满足系统的快速、灵活等要求。

总线控制器(BC);远程终端(RT);远程终端组合选择消息监控(RTMT);数字信号处理器(DSP);可编程门阵列(FPGA)

1 引 言

当前,航空电子系统中的主流通信网络仍然采用GJB289A,因为GJB289A总线技术成熟,可靠性高。MBI模块作为航空电子系统中通用总线接口模块,实现了GJB289A总线协议,被广泛应用。之前,MBI模块广泛采用UTMC公司生产的协议芯片实现GJB289A总线的ISBC协议。而ISBC协议,对系统总线通信表的设计要求很高,并且很不灵活。随着总线负载的增加,传统的MBI模块在重量、体积、消息处理速度、存储器容量、软硬件编程方式等方面已经无法满足系统要求。这样,迫切需要设计一款新的MBI来解决上述“弱点”,以提高系统的性能和灵活性。

通过介绍MBI模块的实现,推广SM61864在今后MBI设计上的应用。

2 设计思想

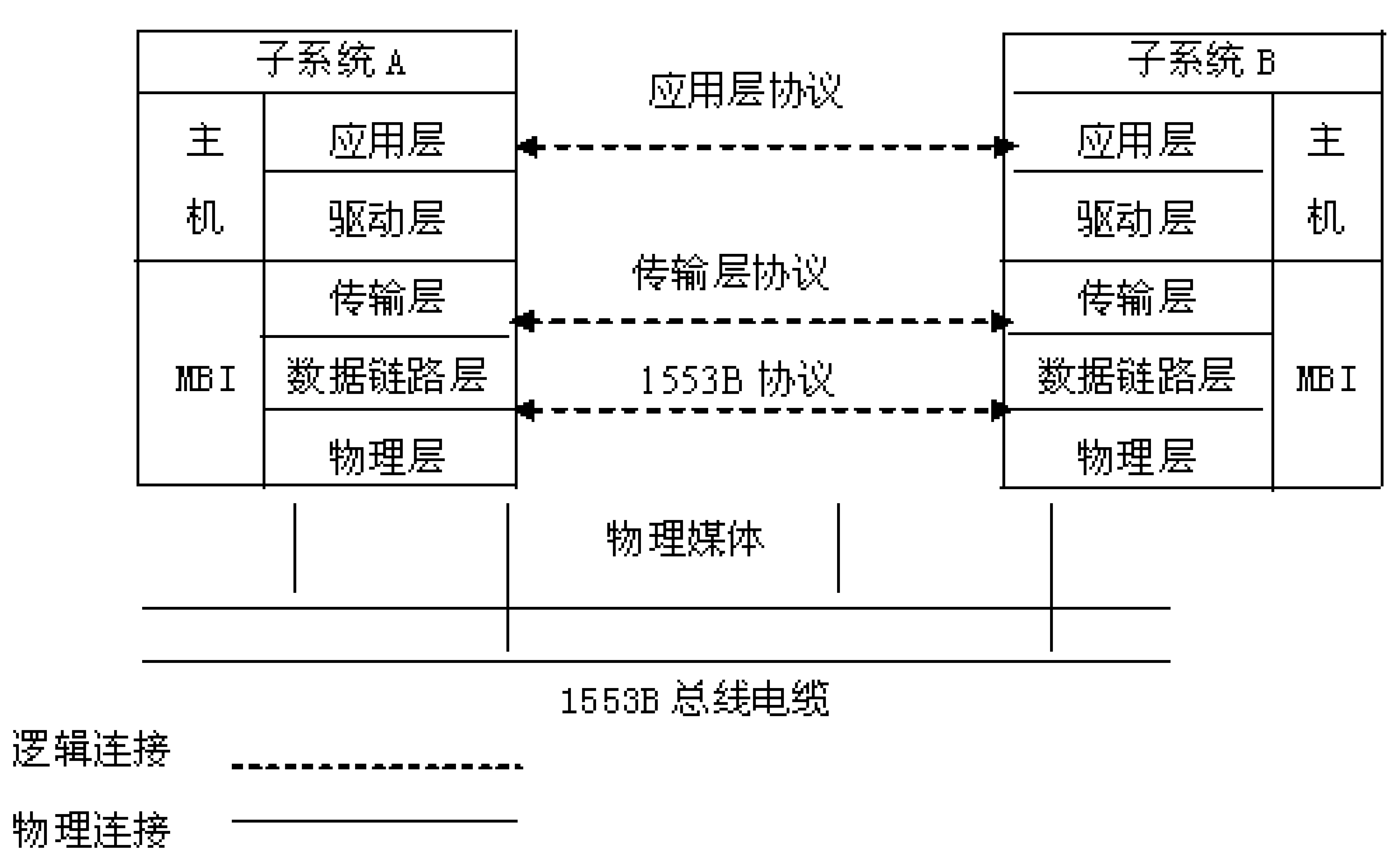

通常,GJB289A总线网络上有且只有一个BC,同时,会有最多31个远程终端。BC用于组织消息传输和管理网络,RT按照BC传输的指令,可以接收BC传输的消息,发送消息到BC或其他RT。航空电子通信系统对应的结构如图1所示。

BC的硬件设计保持和以前设计相同的思路,采用SM61864实现航空电子系统物理层和数据链路层的功能;软件固化在MBI模块上的智能处理器内部FLASH中;驱动软件则驻留在主机上,由应用软件根据系统需要实现对通信软件的控制。

图1 航空电子通信系统层次结构

3 SM61864带来的MBI新特征

MBI在设计重量上要求尽可能轻、体积上尽可能小、消息处理速度尽可能快、存储器容量尽可能大、软硬件编程尽可能方便,因此,在设计的时候,使用SM61864带来的如下优点:

a.实现了MPBC协议,兼容以前的ISBC协议,同时增加了很多新特点;

b.Mini-ACE集成了GJB289A总线协议处理能力和双余度收发器功能,体积大幅减小,重量大幅减轻;

d.主要采用3.3V逻辑供电,5V收发器供电,使得MBI电源设计简单,功耗低;

e.具备了作为BC时能监控RT到RT消息和RT到RT广播消息;

f.作为RT的同时,可以作为选择消息监控,监控除自身外所有其他RT的消息;

g.具有透明模式和缓冲模式,可以和MBI上处理器通过其DMA功能访问MBI上共享存储器。

4 MBI硬件实现

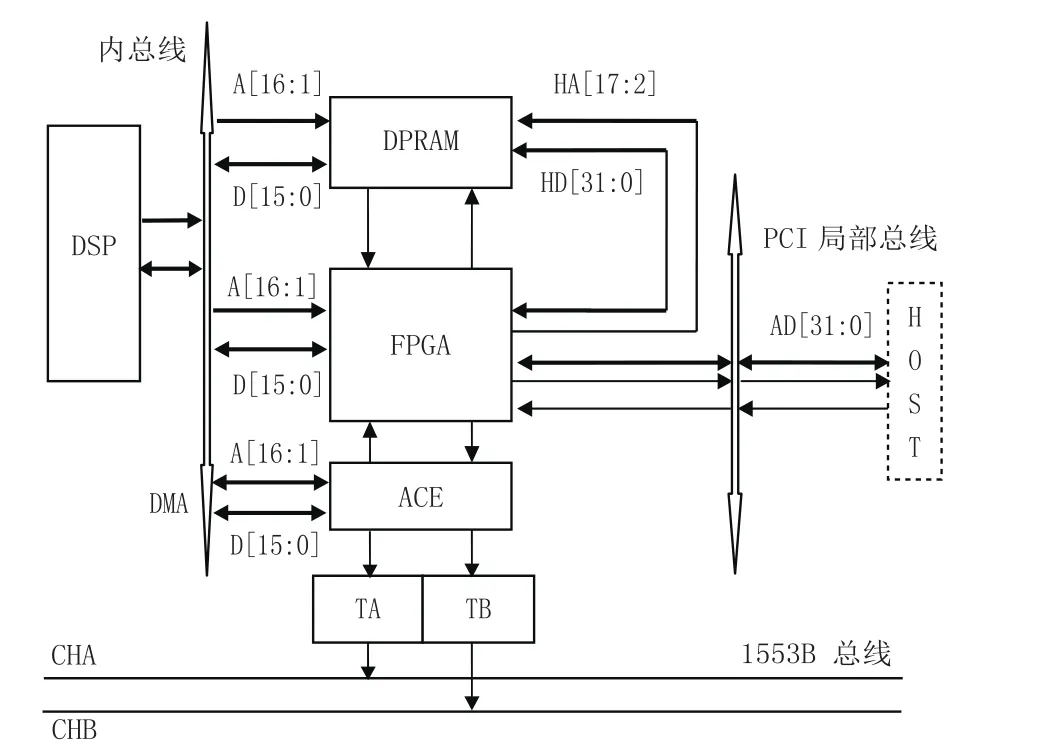

MBI模块上有两路独立的MBI(MBI1和MBI2)。每路MBI的硬件结构如图2所示。

其中,MBI的逻辑电路是通过FPGA实现的,主要功能有:

a.DSP相关的控制逻辑;

b.DSP外部存储器接口逻辑;

c.RTC逻辑;

d.与主机接口的66MHz/33MHz 32位数据接口的PCI从设备逻辑。

其中,DSP相关的控制逻辑,主要实现在透明模式下,与ACE之间的DMA控制逻辑和内部“READY”逻辑;

DSP外部存储器接口逻辑,主要实现多协议复用总线控制器上的RAM和双口存储器右端口、信号灯的译码,以及相关的IO端口译码;

RTC逻辑,采用VHDL语言设计,在功能上保持以前的RTC功能,精度20us/40us可选择,向上计数,带复位、锁功能;

PCI从设备逻辑,未使用传统的PCI桥,而是结合PCI总线规范,采用VHDL语言实现;

图2 MBI结构示意图

主机接口逻辑,实现双端口存储器左端口、信号灯的译码,以及相关的IO端口译码,同时实现主机接口部分的“READY”逻辑;

为了避免主机处理器和DSP或协议芯片对双口存储器访问的冲突,采用BUSY逻辑实现;

SM61864则接成“透明”模式,通过DMA访问外部双口存储器,RT地址锁存信号上拉,通过配置ACE内部寄存器,可以灵活的设置MBI模块作为RT时的RT地址。

SM61864总线信号通过ACE内部的双接收发送器,采用变压器耦合方式和SM61864总线通信网络相连接。

调试的时候,加载软件目标码到DSP内部的RAM中;

固化的时候,烧写软件目标码到DSP内部的FALSH中。

5 MBI软件设计

MBI的软件包括通信软件和驱动软件。

通信软件驻留在MBI模块上DSP内部FALSH存储器中;驱动软件驻留在主机上,提供标准的API接口,供应用软件调用,实现对MBI的控制,和系统控制程序、应用程序等进行动态联编。

通信软件设计是在DSP专用开发工具CCStudio3.1下开发的。驱动软件是在Tornado2.2下开发的,同时移植到AE 653操作系统下的WorkBench2.0上,使得在不同操作系统上都可调用MBI模块驱动程序。MBI软件的顶层结构如图3所示。

图3 MBI软件顶层结构图

主机和MBI之间的通信采用“命令/响应”方式,即主机向MBI模块的DPRAM中命令字单元写相应命令,而MBI执行该命令之后,会在DPRAM中响应字单元写响应字。

MBI主要执行的命令有:初始化、自测试、启动、停止、软复位、加载看门狗等,此外,MBI对RT上下网,自测试失败,紧急消息,互为热备份RT同时上网等,需要向主机发送中断请求。MBI内部需要处理的中断主要有ACE中断,在作为BC的时候,还包括内部定时器周期中断。

5.1 MBI传输软件各模块的实现

初始化模块,首先通过配置DSP内部的PLL电路,XINTF接口,设置DSP的系统时钟频率、CPU时钟频率以及外部接口工作时钟频率等,并配置DSP访问外部各存储区域的时序。然后,依据主机需要的MBI模块的工作方式(BC,RT,MT或RT/MT),配置双口存储器中的相关单元,初始化SM61864内部的固定访问区域,配置寄存器、中断使能、栈指针寄存器等,使得ACE能按照指定的模式工作。

在BC模式,消息栈设置为1K字,最多可存放256条消息,数据缓冲区采用双缓冲模式,遵循系统要求的MPBC协议。

在RT模式,RT地址可以配置,使用单缓冲,忙位设置;可以使用命令非法化表,依据RT地址、发送/接收位、子地址、数据字计数等设置RT相关消息是否合法;可以将方式命令、广播命令的数据,根据需要,放置在特定区域。

在MT模式,可以根据系统需要,设置采用字监控模式或者选择消息监控模式。选择字监控,可以设置各种不同的触发条件;选择消息监控,通过设置消息监控管理表,可以依据RT地址,发送/接收位,子地址进行消息选择,并且有独立的命令栈和数据栈。MBI可以将命令栈中的命令和数据栈中的“数据”重新组织成一条完整的消息,驱动接口通过系统提供的刷新标志,将该消息数据提交给应用。

在RT/MT模式,MT只能采用选择消息监控,可以实现MBI作为RT工作的同时,实现选择消息监控。这时,MBI需要根据RT命令栈指针和MT命令栈指针的变化,决定当前消息结束中断是RT消息还是MT消息。

自测试模块,完成MBI内部资源的自测试,并将自测试结果存储在双口存储器中,当自测试失败时,向主机发送中断请求。主要完成的测试有:DSP自检,双口存储器测试,RTC功能测试,ACE自测试等。

启动和停止模块,是启动或者停止MBI模块按照初始化的功能工作。工作的时候,完全遵循系统提出的MPBC协议。协议严格控制消息传输时间,控制消息重试,消息传输通道等,极大地提高了总线通信效率,减小了通信负载,并提高了系统地可靠性。

软复位模块,完成自测试功能和初始化功能,并设置复位标志;

加载WDT模块,依据系统需要的WDT时间,加载并启动WDT定时器工作。

5.2 MBI驱动软件接口函数的实现

基本接口驱动提供:主机读、写MBI模块DPRAM;主机读、写MBI模块IO端口的基本接口函数。

MBI控制程序提供了:主机向MBI模块DPRAM命令字单元写初始化命令、自测试命令、启动命令、停止命令、加载WDT命令,然后获取MBI模块响应字的相应驱动程序接口函数。

TMR控制程序提供了主机读、写MBI模块上RTC以及读取BC与RT的RTC差值等驱动程序。

系统控制驱动程序提供了主机更改MBI模块作为BC时的子系统模式,获取RT通道状态和通道切换状况,以及软复位MBI模块的驱动程序。

消息控制程序提供了主机从MBI模块接收消息缓冲区中提取消息数据和向发送消息缓冲区写消息数据,以及找出两个消息号之间,接收消息数据已经刷新的消息逻辑号的驱动接口函数。

中断服务程序提供了主机依据MBI模块所发出的中断和记录中断原因,进行相关中断处理的过程。MBI中断主机的原因有:紧急消息中断,看门狗上溢中断,自测试失败中断,RT上下网中断,热备份RT同时上线中断等。

6 MBI模块功能验证

由SM61864实现的MBI,在系统单元进行综合的时候,对各项功能的验证如下:①作为BC,完全实现了系统要求的MPBC协议,能正常、稳定、灵活的组织消息传输,重试管理正常,通道管理正常,同时具备热备份功能;②作为RT,能灵活的进行RT地址配置,能正常接收与之相关的消息和正确响应方式命令;③作为MT的时候,能够对总线上所有的消息数据进行字监控,也可以对选择的消息进行监控;④作为RTMT的时候,能作为RT的同时,对总线上其他的RT消息进行监控。

综上所述,由Mini-ACE所实现的MBI,能完成系统提出的所有需求,并可以稳定、可靠地工作。

7 结束语

由SM61864实现的MBI,采用MPBC协议,引入了时间调度和消息帧管理等机制,为系统设计提供了一种灵活的思路,为今后AFDX通信网络、FC总线通信网络的研究奠定了良好的基础。但SM61864总线速度没有根本性的提高,仍然使用1MHz的总线速度,今后,可以逐步考虑使用10MHz,100MHz的总线,进而转入千兆以太网、FC网络。最后,希望广大读者能提供宝贵的意见和建议。

[1] Helmy A.Small world in wireless networks[J].IEEE Communications Letters,2003,7(10):490-492.

[2] Zemanoval L,Zhou CS,Kurths J.Structural and functional clusters of complex brain networks[J].Physica D,2006,224(1-2):202-212.

[3] Girvan M,Newman M E J.Community structure in social and biological networks[J].Proceedings of the National Academy of Sciences of the United States of America,2002,99(12):323-330.

[4] Newman E J.The structure and function of complex networks[J].SIAM Review,2003,45(2):167-256.

[5] Zhou T,Zhao M,Chen G R.Phase synchronization on scale-free networks with community structure[J].Phys Lett A,2007,368(6):431-434.

Development and Application of GJB289A Based on SM61864

An Baijun,Lv Bing,Li Xinmin

(Xi’an Aeronautics Computing Technique Research Institute,AVIC,Xi’an 710068,China)

Tomeet the requirements ofminimization,low-power,high-credibility and flexibility of MBImodule,a new MBImodule is designed in this paper,which uses the mini DSP processor SM320F2812 of TICorp.as the processor,BU61865 of DDC as the GJB289A protocol processor and FPGA to realize themain logic circuit.The MBImodule has two redundant channels and is capable to minimize the payload of the bus to improve the bus transmission efficient.Themini-ACE can be used as the bus controller,remote terminal,bus monitor and the combination of remote terminal and select messagemonitor.After the integration in the system-design institute,the MBImodule satisfies the requirements of high speed and flexibility.

Bus Controller(BC);Remote Terminal(RT);Remote Terminal and selected Message Monitor(RTMT);Digital Signal Processor(DSP);Field Programmable Logic Array(FPGA)

10.3969/j.issn.1002-2279.2015.03.008

TP393

A

1002-2279(2015)03-0024-03

安百俊(1982-),男,吉林安图人,学士,工程师,主研方向:硬件研发。

2014-10-14