VCSEL阵列用半绝缘砷化镓单晶生长工艺研究

孙 强,兰天平,周春锋

(中国电子科技集团公司第四十六研究所 天津300220)

基础研究

VCSEL阵列用半绝缘砷化镓单晶生长工艺研究

孙 强,兰天平,周春锋

(中国电子科技集团公司第四十六研究所 天津300220)

VCSEL(垂直腔面发射激光器)阵列是一种面发射的化合物半导体有源器件,已广泛应用于激光制导、激光测距等军事电子领域。为了减少发射单元之间的高频串扰,VCSEL阵列必须生长在高电阻率和低位错密度的砷化镓衬底上。通过采用 VGF(垂直梯度冷凝法)生长 7.62,cm砷化镓单晶,并选取合适的温度梯度(4,℃/cm左右)和低位错籽晶,同时掺入一定剂量的高纯碳粉并选用适量的无水氧化硼作为液封剂,成功地研制出低位错密度的7.62,cm半绝缘砷化镓单晶材料。

VGF 砷化镓 单晶生长 半绝缘

0 引 言

VCSEL(垂直腔面发射激光器)阵列是一种化合物半导体有源器件,与传统的边发射半导体激光器侧面发光的结构不同。与边发射半导体激光器相比,VCSEL具有多种优良特性,如:可在较宽的温度范围内实现单纵模工作,动态调制频率高;出射光束具有小的发射角和圆形对称的远、近场分布,使其与光纤耦合效率大大提高;VCSEL出光方向与衬底表面垂直,可实现高密度二维面阵的集成;可以在封装前整片检测,极大地降低了生产成本。VCSEL已经成为目前最有实用价值的半导体器件之一,并开始广泛应用于激光制导、激光测距等军事电子领域。

在 VCSEL阵列中,为了减少发射单元之间的高频串扰,要求相邻单元之间具有很高的电阻,以实现单元之间的电隔离,因此 VCSEL阵列必须生长在高电阻率砷化镓衬底上。然而砷化镓衬底材料较高的位错密度和晶向的较大偏移将会影响外延层质量,使器件寿命缩短。但由于常规的高阻砷化镓单晶抛光片通常采用 LEC工艺研制,很难同时保证高电阻率和低位错密度。因此,有必要开展位错抑制、半绝缘特性控制等一系列半绝缘砷化镓单晶生长工艺的研究,为VCSEL阵列提供优质的砷化镓单晶材料。

1 试验

采用VGF法进行单晶生长。7.62,cm坩埚采用PBN坩埚(放肩角度 100,°),直接将高压合成料砸成块状装料,将坩埚装满,预计装料量3,500~4,000,g。对温度梯度、氧化硼掺入量和掺碳量进行了对比试验。

6个监控热偶控温范围如表 1所示,恒温化料 24,h左右开始单晶生长培养。应注意保持籽晶和PBN坩埚的籽晶井有适当间隙,避免引晶失败。单晶生长结束后,进行外观检查。

表1 监控热偶控温范围Tab.1 Temperature range of the thermocoup le

2 结果与讨论

2.1 温度梯度对位错的影响分析

晶体生长过程及生成后的降温过程,即晶体的热历程是工艺过程中位错产生的主要原因。对于熔融法生长的单晶材料,材料的生长过程为过冷生长,因此必须依靠一定的温度梯度才能进行。温度梯度的存在,使得晶体内部产生了一定的应力,同时由于砷化镓材料的热导率较低,加剧了热应力的形成。当应力超过位错产生的临界应力时,就会产生位错。

典型的 VGF砷化镓单晶生长的固-液界面示意图如图 1(a)所示,由于边缘优先生长,中心生长滞后,使得中心生成的晶体内部应力无法释放,容易形成晶格缺陷,导致位错缺陷的大量增殖。理想的固-液界面示意图如图1(b)所示。

图1 VGF工艺生长时的固-液界面示意图Fig.1 Schematic diagram of the solid-liquid interface

通过对 7.62,cm 砷化镓晶体生长工艺的研究表明,固-液界面的形状主要取决于热场设计。当高温区和低温区的温度梯度过小时,固-液界面趋于平坦,有利于位错密度的降低,但单晶生长效率低,而且异相成核(花晶、孪晶)的几率大大增加。当高温区和低温区的温度梯度过大,固-液界面就会变“凹”,会加速位错的增殖。只有当高温区和低温区的温度差适宜,整个晶体生长过程的界面才能一直保持微凹或平坦的形状。另外,坩埚托的形状及材质对固-液界面的形状也有较大影响。

表2 部分7.62,cm VGF晶体位错密度测试结果Tab.2 The etch pit density of some 3-inch VGF GaAs monocrystals

部分7.62,cm VGF晶体位错密度测试结果如表 2所示,控制温度梯度在 4,℃/cm 左右时,易于成晶,且晶格完整性较好(相应的位错密度较低),在晶棒尾部(VGF 05-1302)能观察到明显的缩晶纹(见图2)。

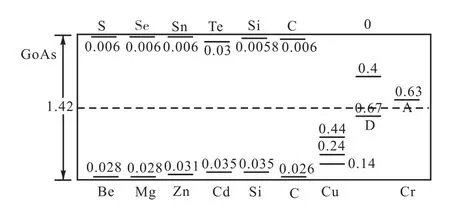

半绝缘特性,即要求保证砷化镓材料的电阻率>1× 107,Ω·cm。砷化镓在常温下的带隙为 1.42,eV,半绝缘特性是由晶体内的电活性杂质和缺陷相互补偿的结果。砷化镓的能带及杂质能级位置如图3所示。

根据能带理论,补偿的结果使费米能级保持在禁带中央,就实现了材料的半绝缘特性。在实际晶体生长工艺中,如果能够满足3.2的浓度公式(1),就可以保证材料的半绝缘性。

图2 7.62,cm砷化镓单晶尾部缩晶纹Fig.2 A shrinkage crystal pattern in the tail of a 3-inch SI-GaAs monocrystal

图3 砷化镓材料禁带中各种杂质及能级位置Fig.3 Im purities and energy-levels in the band gap of the GaAs material

2.2 碳粉和氧化硼掺杂量对半绝缘特性影响分析

式中:ND——浅施主;NA——浅受主;[EL2]NDD——深施主EL2能级。

砷化镓单晶材料是在近化学计量比的熔体中生长的,一般熔体的[As]/([As]+[Ga])大于 0.475,砷化镓晶体中就能形成深施主杂质能级 EL2,浓度一般为(1.0~2.0)×1016,cm-3。主要浅受主杂质为 C元素,来源于原材料高纯砷和多晶高压合成的石墨加热系统,浓度一般为(0.5~10)×1015,cm-3。主要的浅施主杂质为Si元素,来源于VGF单晶生长的石英密封系统。因此,为实现砷化镓材料的半绝缘特性,要采取的技术途径一是要提高浅受主杂质 C的浓度;二是要抑制浅施主杂质Si的浓度。本项目主要开展了碳粉和氧化硼两项掺杂技术的研究。

掺杂量理论计算公式如式(2)所示:

式中:N——晶体头部的掺杂浓度;

WGaAs——每炉次的投料量;

PGaAs——GaAs的密度,为5.32,g/cm3;

NA——阿伏加德罗常数6.02×1023;

k——C在GaAs中分凝系数1;

MC——C的分子量12。

当 N=5×1015,cm-3,投料为 1.0,kg时,理论掺碳量 m=1.87×10-2,mg。

由于碳粉密度为 1.7,g/cm3,大于液态氧化硼的密度1.5,g/cm3,小于砷化镓熔体的密度 5.72,g/cm3,石墨粉漂浮在熔体上,部分悬浮在氧化硼中,很难直接进入砷化镓熔体中。另外,由于 VGF法砷化镓单晶生长为密闭式真空生长,抽真空时,碳粉易被抽真空带走,有效的掺杂剂量很难确定。因此,本实验采用在多晶料尾部打 3~5个小孔放置碳粉,然后用圆柱状砷化镓小块将孔堵住保证碳粉不被抽真空带走。因此,碳的实际装入量应远大于理论计算掺杂量。

此外,在石英管密闭式 VGF砷化镓单晶生长工艺中,由于生长环境所使用的真空系统由石英材料封口构成,不可避免地要引入浅施主杂质Si。试验表明,增加氧化硼液封层的厚度可以有效阻止石英安培瓶挥发的 Si对熔体的沾污,提高了VGF工艺中晶体的电阻率。通过对不同厚度氧化硼液封层的对比试验认为,当氧化硼层的厚度大于 3,mm时,实际氧化硼投料量为50,g左右,氧化硼可以完全覆盖住砷化镓熔体,有效地阻止了石英中 Si杂质进入熔体的几率,保证了生成的晶体具有半绝缘特性。同时,氧化硼能与PBN坩埚壁较好浸润,在熔体与坩埚壁之间形成隔离层,避免了熔体与 PBN坩埚壁的直接接触,消除了接触区晶粒界面核生成的主要原因,解决了坩埚壁导致多晶的问题,提高了成晶率。

通过几炉次的对比试验(见表 3),最终确定的掺碳量为(14±2),mg(投料量(3.7±0.3),kg),氧化硼投入量为 32~36,g。也可以同时降低碳粉投入量和氧化硼投入量,但碳粉投入量不应少于11,mg,氧化硼投入量不应少于25,g。■

表3 不同掺碳浓度的砷化镓单晶电学参数对比表Tab.3 Electrical properties of GaAs ingots w ith different carbon weights

[1] 陆大成,段数坤. 金属有机化合物气相外延基础及应用[M]. 北京:科学出版社,2009.

[2] 江剑平. 半导体激光器[M]. 北京:电子工业出版社,2000.

[3] 何杰,夏建白. 半导体科学与技术[M]. 北京:科学出版社,2007:45-73.

The Technology of 3-inch SI-GaAs M onocrystal Grow th for VCSEL Array

SUN Qiang,LAN Tianping,ZHOU Chunfeng

(No.46 Research Institute of China Electronic Group Corporation,Tianjin 300220,China)

The VCSEL(Vertical Cavity Surface Emitting Laser)array,a type of active compound sem iconductor device w ith laser beam emission from the surface,has been w idely applied in military in laser guidance and laser ranging. In order to reduce the high frequency crosstalk between launch units,the VCSEL array must be grown on a GaAs substrate w ith high resistivity and low etch pit density. In this study,a 3-inch SI-GaAs monocrystal w ith low etch pit density was successfully developed from a 3-inch GaAs monocrystal grown by VGF(Vertical Gradient Freeze)w ith the selection of a suitable temperature gradient(about 4,℃/cm)and a low seed crystal,the mixing of a certain dose of high purity carbon powder and the use of anhydrous boron oxide as the liquid seal.

Vertical Gradient Freeze(VGF);Gallium Arsenide(GaAs);monocrystal grow th;semi-insulating

TN304.0

:A

:1006-8945(2015)03-0018-03

2015-02-13