浅议频率合成器在现代无线通信收发机中的实现形式

胡习霜 玄甲辉

【摘要】 随着科技的不断进步,无线通信技术在人类生活中的作用越来越大。本文对现代无线通信收发机中的关键部件之一——频率合成器的实现形式做了一般性的讨论。首先简要介绍了下无线通信系统中的重要组成部分——射频收发机,对频率合成器在无线通信收发机中的作用做了简单说明。然后详细介绍了频率合成器的几种实现方法,并分别展开描述具体实现形式。文章最后对频率合成器的实现形式做了总结,并指出在目前的无线通信领域中应用最为广泛的是锁相环式频率合成器体系结构。

【关键字】 无线通信 频率合成器 射频收发机 实现形式

一、无线通信系统的射频收发终端概述

无线通信系统是用于发送从信源发出的信息或消息到一个或多个目的地的系统,信源产生的信息可以包括多种形式,比如图像、语音、数据信号等。典型的无线通信系统包括信源信宿、输入输出换能器、发射机和接收机。

通常,接收机和发射机可以被集成设计为无线收发机。集成之后,接收单元和发射单元可以复用部分模块,可进一步减小芯片面积。随着市场需求的不断提高,对收发机的指标要求也越来越高,在保持高性能的基本要求之下,还要求无线收发机具有低成本、低尺寸、低功耗等特点。

二、频率合成器在无线通信收发机中的作用

在无线通信领域中,频率合成器起着越来越重要的角色。在无线收发机结构中,频率合成器作为混频器中本振的产生源,是不可或缺的一部分。频率合成器是将一个高稳定度和高精确度的标准参考频率(一般是晶体振荡器),经过倍频或分频等操作对它进行四则运算,最终产生一个或多个具有同样精确度和稳定度的频率源的电路模块或设备[1],它是影响电子系统稳定性和精确性的最关键因素之一。

在现代无线通信收发机中,频率合成器获得的频率精确度和稳定度的好坏,将直接决定整个射频收发机系统性能的好坏。

三、频率合成器的实现形式

有关频率合成器的研究,最早提出是在20世纪30年代,在近代电子技术发展的过程中,频率合成器体系得到不断发展,结构得到不断扩充。

从这项技术提出以来,先后经历了直接模拟式频率合成器、直接数字式频率合成器和间接锁相式频率合成器等三个阶段的发展。

随着各种现代产品中电子系统地位的与日俱升,在应用以及市场的牵引下,频率合成器技术得到不断快速发展,如高指标、小体积的合式频率合成器[2]以及将锁相和DDS相结合的混合式频率合成器。

如表 1所示,频率合成器大致上可分为三大类:直 接型、间接性和混合型。

3.1直接模拟式频率合成器

直接模拟式频率合成器是最早出现的一种频率合成类型,它的工作原理很简单,就是用谐波发生器、混频器、倍频器、分频器和带通滤波器电路对一个或几个基准频率进行四则运算,从而产生所需求的频率信号。根据合成方式不同可分为相关合成与非相干合成两种[3]。

直接频率合成器可以实现快速频率变换、低相位噪声、几乎任意高的频率分辨率以及很高的频率输出。但是直接频率合成要使用很多的硬设备,因而具有体积大、造价高的特点。除此,它还有另一个缺点:在输出端会出现大量无用的寄生频率——杂波。

在大部分应用场合,直接频率合成方法已被采用锁相技术的间接频率合成方法所取代[1]。

3.2直接数字式频率合成器

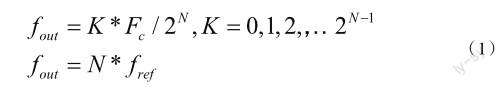

直接数字式频率合成技术是1971年由美国学者J.T、C.M.R和B.G首次提出的,采用全数字化方式实现。一个典型的DDS系统主要由相位累加器、正弦波查找表、D/A转换器和低通滤波器组成。DDS的输出频率为:

其中,K为频率控制字,N为相位累加器的比特位长度,FC为时钟频率。由于受奈奎斯特定律的约束,最高输出频率不能高过系统时钟的一半,一般取时钟的40%作为上限,其频率分辨率为FC / 2N。

DDS是一个完全数字化的系统,具有易于集成、频率合成速度快、极快的跳频速度、频率切换时相位连续和极高的频率分辨率等优点,缺点是杂散比较大、输出频率低、功耗较大。

3.3间接锁相式频率合成器

锁相式频率合成技术又称为间接式频率合成技术,是基于PLL的一种频率合成技术。广义的讲,锁相环电路使一个特殊系统跟踪另一个系统。在同步状态,振荡器输出信号和参考信号之间的相位差为0,或者保持常数[4]。锁相环是一种相位误差控制系统,它通过比较输入信号和压控振荡器输出(或分频器后的输出)信号之间的相位差,从而产生一个反馈电压来控制VCO的输出频率,以达到与输入信号成倍频关系的目的。

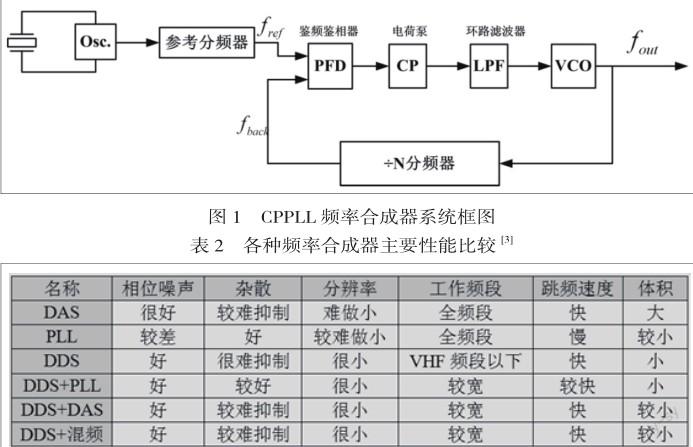

在现代通信用收发终端机中,基于PLL的频率合成器广泛采用电荷泵锁相环(CPPLL)式频率合成器。CPP LL频率合成器的一般系统框图如图 1所示。

电荷泵锁相环式频率合成器由鉴频鉴相器、电荷泵、压控振荡器以及÷N分频器组成。频率合成器的输出频率为:

其中N为分频器分频比(可为整数或小数),fref为PFD的输入参考频率。

3.4混合型频率合成器

混合式频率合成技术是近几年非常流行的频率合成技术,主要形式有DDS激励PLL、DDS内插PLL、DDS+倍频、DDS+混频等几种合成方式[3]。

这种方案利用了DDS的高分辨率来提高PLL输出的频率分辨率,又能得到较高的频率输出,同时PLL内的环路滤波器对带外的DDS杂散也能够起到很好的抑制作用。但是该种混合型频率合成器的频率转换时间取决于PLL。

四、频率合成器不同实现形式总结

本文中大致介绍了目前所存在的几种不同形式的频率合成技术,其中,无线通信领域中应用最为广泛的是锁相环式频率合成器体系结构。

这种结构的最大优点是容易在CMOS工艺上集成。在性能可满足大多数无线通信系统指标要求的前提下,可大大节省功耗。基于ADPLL的频率合成器一般用于数字电路,能够纠正时钟,实现很低的时钟倾斜,缺点是不能够编程。

在需要本振频率很高的情况下,一般可采用直接模拟频率合成器结构,缺点是功耗和体积比较大,而且成本会 比较高。综上,可对各种频合成器主要性能比较如表 2所示。

参 考 文 献

[1]李智群. 射频集成电路与系统[M]. 北京:科学出版社. 2008.8.

[2]Longiun Zhai,Yonghua Jiang,Xiang Ling,et a1.DDS-Driven PLL Frequency synthesizer for X-band Radar signal simulation[C]. IEEE Conference on Systems and control in aerospace and astronautics.IEEE,2006:344-346.

[3]杨檍,鲍景富. 现代频率合成技术的研究进展. 电讯技术 Telecommunication Engineering. 2007, 47(2).

[4]Roland E.Best 著 李永明 [等] 译. 锁相环设计、仿真与应用. 北京:清华大学出版社,2007.4