一种低功耗多输出带隙电压基准源电路的设计

张珂铭

摘 要:文章提出了一种基于带隙原理的多路输出的基准电压电路设计。该电路采用标准CMOS工艺,工作电压为1.8~3.3 V,输出基准电压为1.5 V、1.1 V、0.9 V,温度系数为75.86 ppm/℃。由于采用了MOS管亚阈值原理,功耗低至4.29 μW。在室温27 ℃和频率为10 Mhz处的电源抑制比为22.5 dB。

关键词:带隙;电压基准;多输出;低功耗;亚阈值

中图分类号:TN432 文献标识码:A 文章编号:1006-8937(2015)27-0007-02

1 电路原理图及原理分析

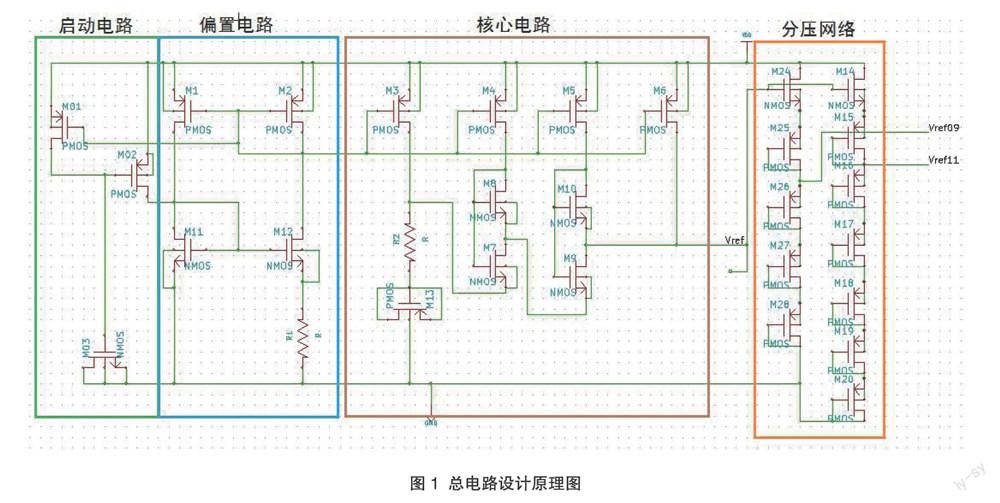

总电路设计原理图,如图1所示。

一般来说,带隙基准产生基准电压是基于两种电压之和:一个二极管电压和一个适当系数的PTAT电压。PTAT电压是与绝对温度成正比的电压。基准电压可以表示为公式(1):

VREF=VD+KPTAT·UT (1)

式中,热电压UT的值为(k·T/q),其中k是玻尔兹曼常数,T是绝对温度,q是电子电荷量。热电压通常是由两个双极晶体管的基极-发射极电压的差值产生。

常数KPTAT是与温度无关(在一阶情况下)的增益因子。由于(1)式中VD为负温度系数的电压,因此调整KPTAT到合适值便可达到合适的温度补偿的目的。KPTAT的值约为10,通常是由具有同样温度系数的两个电阻的比值决定的。

通常在CMOS工艺中,(1)式中的VD是由寄生的纵向或横向双极性晶体管实现的。但是一些标准的数字CMOS工艺的器件库中并没有这些特性的器件可供使用。一种PN结的替代的实现方法是利用P衬底的CMOS工艺实现的。该MOS管的栅、源、漏端被连载一起作为阳极,而N阱则作为阴极。对于一个357 nA的电流来说,该管的VGB有一个负的温度系数,约为-1.69 mV/℃。(本电路中,电流取值并不为357 nA,故其负温度系数也并不等于-1.69 mV/℃,设计过程中有其仿真结果。)

如上文所言,ΔVD可以用来产生热电压UT。而一种替代的方法是,可以用两个工作在亚阈值的两个MOS管的栅源电压差来产生UT。对于工作在亚阈值晶体管,若其漏源电压(VDS)大于0.1 V,则其漏源电流(IDS)由公式(2)给出:

IDS=2mμ0COXSU 2T·exp[(VGS-VT)/m·UT] (2)

式中,S=(W/L)是晶体管的宽长比;

m是亚阈值斜率因子;

μ是有效沟道迁移率;

COX是单位面积的栅氧电容。

正如寄生三极管可以产生的热电压UT,亚阈值电流与栅源电压的指数关系也可以被用来产生UT。一个自级联复合晶体管的Δ VGS由公式(3)给出:

Δ VGS=VGSM1-VGSM2=VDS1

=n·UT·ln[(nM2·IDS1)/(SM1·IDS2) (3)

可以发现,公式(3)表现出PTAT的特性,两个器件必须工作在亚阈值区。

我们的初始电路设计如图1所示。正如传统的带隙基准一样:一个二极管电压加上了一个合适系数的PTAT电压。

晶体管M1、M2、M11和M12用来产生带隙基准的偏置电流(IBIAS)。令SM1=SM2=SM3,偏置电流由公式(4)给出:

IBIAS =(VGSM11-VGSM12)/RPTAT (4)

对于我们的电路而言,我们选择了357 nA的偏置电流,这要求RPTAT约为100 kΩ。这个电阻可以用一个工作在深三极管区的MOS管替代。

输出电压VREF由公式(5)给出:

VREF =VD14+VDS7+VDS9 (5)

通过M4、M5、M6的电流分别为:(S4/S2)·IBIAS、(S5/S2)·IBIAS 和(S6/S2)·IBIAS。

当体效应可以忽略时,用公式(3)和电流镜的各晶体管的尺寸比,公式(5)可以被写为式(6):

VREF =VD14+

UT·n·ln (6)

通过公式(6)我们发现,通过M4~M10合适的尺寸选择,可以对VREF进行合意的温度补偿。

在公式(6)中,将VREF对温度T求导,令其等于0,我们可以得到公式(7):

TCVD /(TCUT)=ln (7)

在电路进行仿真后,我们发现其功率超过指标,为了降低功率,我们要降低管子的电流,这又造成了输出很难维持在1.5 V,于是我们在提供负温度系数的管子(M14)上,叠加了一个电阻,以提高输出电压。

电路采用1.8 V的电源电压。

如总电路图中的M13,在我们选取的电流下,其栅极电压呈现负的温度系数,同时,在其至上叠加的电阻的压降呈正温度系数,两者叠加后,再加上M7~M10组成的电路网络上的正温度系数的电压,最后调节参数,即得到较好的主输出1.5 V。

在实现了1.5 V(Vref)的基准输出后,我们用其分压实现1.1 V(Vref11)与0.9 V(Vref09)输出,由于本基准不是利用基准电路流过电阻生成的,所以用电阻网络分压会对前级电路造成影响,使输出不准确。

在分压网络中,采用了PMOS Cascode 结构的源极跟随器,隔离对前级输出的影响,并进行电压跟随与分压,而M01、M02、M03三个管子构成启动电路。

2 电路设计指标总览

电路设计指标总览,见表1。

参考文献:

[1] 毕查德·拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2002.

[2] C.J.Fayomi,G.Wirth,H.Achigui,etc.Sub 1 V CMOS Bandgap references design techniques:a surVey[J].Urnal of Analog Integrated Circuits and Signal Processing,2010,(62).

[3] A.E.Buck,C.L.McDonald,S.H.Lewis,etc.A CMOS bandgap reference without resistors[J].IEEE Journal of Solid-State Circuits,2002,(37).