基于FPGA的三相电网不平衡下的锁相环设计

李鹏飞, 刘淮涛, 吴平志

[1.江苏省建筑设计研究院有限公司,江苏南京 210029;2.中船重工鹏力(南京)新能源科技有限公司,江苏南京 211106]

基于FPGA的三相电网不平衡下的锁相环设计

李鹏飞1, 刘淮涛2, 吴平志2

[1.江苏省建筑设计研究院有限公司,江苏南京 210029;2.中船重工鹏力(南京)新能源科技有限公司,江苏南京 211106]

针对现有的数字锁相环在三相电网电压不平衡下精度降低的问题,提出了一种基于双同步坐标系解耦软件锁相环(DDSRF-SPLL)的控制策略。分析了DDSRF-SPLL的数学模型,根据DDSRF-SPLL解耦控制策略,采用硬件描述语言VHDL设计了基于FPGA的各个模块。仿真结果表明,基于FPGA的锁相环抗干扰能力强,对频率波动具有很好的适应性,锁相效果稳定、准确。

双同步坐标系解耦软件锁相环;电网电压;FPGA;锁相精度

0 引 言

锁相环(Phase_Locked Loop,PLL)是能锁定输入信号相位的闭环控制系统。随着光伏、风能等分布式发电和柔性交流输电系统(Flexible Alternative Current Transmission Systems,FACTS)的广泛应用,为保证系统快速稳定运行,需要对电网电压相位实时跟踪检测,确保在电网电压不平衡或频率突变时,锁相环依然能够准确地获取电压相位,这就使得锁相环成为系统的重要组成部分。常用的锁相环基本设定电网电压频率固定为50 Hz,忽略频率变动带来的影响,实际电网电压频率并非理想化,这样会降低锁相精度。FPGA不占用CPU资源,依靠硬件优势,基于FPGA的三相锁相环能快速、准确锁相。

电网电压不平衡与频率突变在实际电网系统中是不可避免的,文献[1]虽然在算法上进行了优化,但在电网电压不平衡下无法实现准确的电网锁相。文献[2]采用基于双坐标解耦变换来消除不平衡,但仍未考虑电网电压频率波动带来的锁相精度不高问题。

本文针对电网电压频率波动造成采样不准而导致锁相精度降低的问题,提出设计新型基于FPGA的锁相环,包括三相锁相环的系统原理、算法以及仿真。

1 单同步坐标系软件锁相环

1.1 系统建模

单同步坐标系软件锁相环(SSRF_SPLL)在电网电压平衡时,能迅速、准确获得正序分量,进而有效地检测出电网电压的相位与频率,其矢量图如图1所示,U和UPLL分别为在dq坐标系下实际电网电压矢量与锁相环输出的电压矢量。当锁相环准确地获得电网电压相位时,U和UPLL应该是重合的,即θ′与θ相等,显然通过闭环控制使得q轴分量为0,其控制原理图如图2所示。

图1 SSRF-SPLL矢量图

图2 SSRF-SPLL控制结构图

假设电网电压三相平衡,并令A相电压的初始相位为0,则三相电压可表示为

式中:U---电网电压的最大值;

ω---电网电压角频率。

转到两相静止αβ坐标系和同步旋转dq坐标系,可得

式中:ωt---电网电压矢量的实际角度;

θ′---锁相环的输出角度。

当准确锁相后,有

此时,系统开环传递函数为

闭环传递函数为

利用MATLAB/Simulink进行了SSRF_PLL仿真,结果如图3和图4所示。可见,SSRF_PLL在电压平衡时能迅速锁相,当电网电压突变不平衡时输出角度有偏差,不能精确地跟踪电网电相位。

图3 SSRF-SPLL三相系统电压

图4 SSRF-SPLL在电压不平衡时的输出角度

2 双同步坐标系软件锁相环

2.1 系统建模

为应对电网电压负序分量的干扰,双同步坐标系软件锁相环(DDSRF_SPLL)将电网电压矢量分成正序、负序两个分量,正序分量对应以ω逆时针旋转的dq+坐标系,其角度为θ′,负序分量对应_ω′顺时针旋转的dq_坐标系,角度为_θ′。U+1和U_1分别为电网电压正负序分量,分别以ω角速度逆时针和顺时针旋转。锁相环分别对U+1和U_1进行坐标变换,再经过解耦控制和低通滤波器(LPF),最终通过PI控制得到电压频率和相位。其原理结构图如图5所示。

图5 DDSRF-SPLL原理图

当PLL锁定相位后,θ′可近似认为与ωt相等,则有

其中:

由图5可知,基于双坐标系变换的解耦控制策略含有非线性环节,对其进行准确的建模比较困难,只能进行近似的建模分析。在误差比较小时,其等效传递函数与SSRF_SPLL的相同。由图5及式(7)、(8),可得开环传递函数和闭环传递函数为

2.2 仿真结果

搭建MATLAB/Simulink仿真,分别模拟t=0.1 s时电网电压突变频率及系统锁相效果,如图6、图7所示。

图6 DDSRF-SPLL系统频率突变

图7 DDSRF-SPLL频率突变时锁相结果

含有谐波且不平衡时的电网电压及锁相效果如图8、图9所示。

图8 DDSRF-SPLL电网电压含有谐波且不平衡

图9 DDSRF-SPLL电网电压含有谐波且不平衡锁相结果

DDSRF_SPLL在电网电压不平衡时,能够准确检测出电压的相位及电压频率。当电网频率发生变化时,锁相环的准确度不受影响,并对谐波表现出良好的适应性。

3 三相锁相环的FPGA设计

3.1 控制策略

为避免电网电压频率波动或突变造成系统电压采样的不准,本文设计基于FPGA的三相锁相环,采用DDSRF_SPLL控制策略,全部模块均采用VHDL语言编写。设定频率为50 Hz的标准正弦波,频率对应FPGA中n个计数单位,设定每个电网周期采样点数为2 000。FP模块的作用类似于分频器,系统输出的电网频率反馈给FP模块,然后输出与之对应的电网电压采样频率,送给A/D采样模块和DQ解耦模块。对于A/D采样模块,当电网电压频率波动时,每个周期采样点数保持不变,但采样频率随反馈的电网电压计数单位而改变。经过坐标变换得到一个周期的存放在FIFO中,当电网电压频率波动时, FIFO的输出与输入不相等,其偏差经过比例积分环节的调整,能迅速调整角频率,进而改变采样频率,保证采样精度,提高锁相效果。同时,FIPI模块输出开始信号用来采样,输出的锁相环角度送给正弦、余弦模块,计算后再输出到DQ解耦模块。

为方便仿真,模拟三相电网电压频率突变和三相不平衡并将三相电网电压值固化在ROM中,存放在A/D模块中。

3.2 试验结果

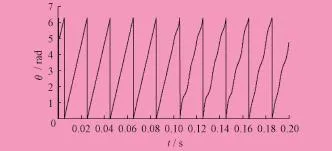

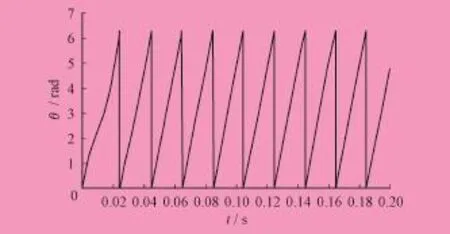

基于FPGA的三相不平衡电压下的检测结果如图10所示。可以看出,基于FPGA硬件的三相锁相环设计能够实时检测并追踪三相电压的相位。

图10 基于FPGA的三相不平衡电压下的检测结果

4 结 语

本文分析了三相锁相环的基本原理,针对单/双同步坐标轴系软件锁相环建立模型并进行Simulink和FPGA仿真。仿真结果表明,基于FPGA硬件实现的三相PLL可实时跟踪三相电压频率和相位,其动态和静态特性均良好,完全适应分布式发电和柔性交流输电系统中锁相的要求。

[1] SUN B,DAI N Y,CHIO U F,et al.FPGA-baSed decouPled double SynchronouS reference frame PLL for active PoWer filterS[J].IEEE Conference on InduStrial ElectronicS and APPlicationS,2011(6):2145-2150.

[2] 洪小圆,吕征宇.基于同步参考坐标系的三相数字锁相环[J].电工技术学报,2012(11):203-210.

[3] 孔雪娟,罗昉,彭力,等.基于周期控制的逆变器全数字锁相环的实现和参数设计[J].中国电机工程学报,2007(1):60-64.

[4] 张兴,张崇巍.PWM整流器及其控制[M].北京:机械工业出版社,2012.

[5] ZHANG Z J,LI H,ZHANG X,et al.Simulation and modelling of SoftWare PhaSe-locked looPbaSed on Single/double SynchronouS coordinate SyStem [J].PoWer SyStem Protection and control,2009,39(11):138-144.

DeSign of PhaSe-locked LooP Under Unbalanced Three-PhaSe PoWer Grid BaSed on FPGA

LIPengfei1,LIU Huaitao2,WU Pingzhi2

[1.Jiangsu Provincial Archtectural Design&Research Institute Ltd.,Co.,Nanjing 210029,China;2.CSIC Pride(Nanjing)New Energy Technology Co.Ltd.,Nanjing 211106,China]

Aiming at the lower precision problem of existing phase_locked loop under the condition of unbalanced three_phase grid voltage,this paper proposed a control strategy of decoupled double synchronous coordinate system software phase_locked loop(DDSRF_SPLL).Themathematicalmodel of DDSRF_SPLL was analyzed.According to the decoupled control strategy of DDSRF_SPLL,various modules based on FPGA were designed by using hardware description language VHDL.The simulation results show that the phase_locked loop based on FPGA has advantages of strong anti_interference capacity,good adaptability for frequency fluctuation,stable and accurate phase_locking.

decouPled double SynchronouScoordinate SyStem SoftWare PhaSe-locked looP(DDSRF-SPLL);grid voltage;FPGA;PhaSe-locked PreciSion

TU 852

A

1674-8417(2015)12-0049-05

2015- 11- 10

刘淮涛(1985-),男,工程师,从事电子技术方面的研究。

吴平志(1990-),男,从事配电网谐波治理及无功补偿技术方面的研究。