基于实验平台的数字逻辑实验教学

田淑珍, 全成斌, 李山山, 杨士强

(清华大学 计算机科学与技术系,北京 100084)

基于实验平台的数字逻辑实验教学

田淑珍, 全成斌, 李山山, 杨士强

(清华大学 计算机科学与技术系,北京 100084)

针对传统实验和基于EDA技术的大规模可编程逻辑器件实验在实验教学中的特点,我门将两种实验方式进行了结合,以便充分发挥各自的优势。介绍了在此思想指导下,基于实验平台的数字逻辑实验教学探索。在自己开发的实验平台上规划了实验内容,合理安排了上述两类实验的比重,并添加了学生自主选题的大实验,综合评定学生的实验成绩。实践证明,将两种类型的实验结合后,既可促进学生更好地掌握数字逻辑的基本知识和原理,又可提高学生的动手实践能力,将有利于学生在软硬件两方面都得到很好的训练。

数字逻辑; EDA技术; 可编程逻辑器件; 传统实验

0 引 言

清华大学数字逻辑实验课是在春季学期为大二学生开设的一门必修课程。它虽从理论课中分离出来,独立设课,有独立的学分,能给学生提供更多的实践机会,但又与理论课密不可分,是一个整体[1]。传统的数字逻辑实验是以传统的硬件搭试为主,采用常规的TTL逻辑器件(如逻辑门、计数器、触发器等中小规模集成电路)以手工连线的方法来实现一定的数字逻辑电路功能,是纯硬件的实验。随着EDA技术的成熟和发展,器件已由中、小规模的TTL集成电路发展到大规模可编程逻辑器件。可编程逻辑器件作为当前数字设计的主流器件,已经被大量应用于数字电路和数字系统中,代表了电子设计技术和应用技术的最新技术方向和潮流[2-5]。为了让学生能够及时掌握先进的电路设计方法,培养学生的创新能力,在实验内容的设置上安排基于EDA技术的大规模可编程逻辑器件(CPLD)的实验是极为必要的[6-9]。由于它是以软件设计为主来进行电路的设计和调试,在实验进度和实验成本上都有着对传统实验非常好的互补效果。我们在自己开发的数字逻辑实验平台上尝试将传统实验和CPLD实验进行了结合,取得了较好的教学效果。

1 实验模式的比较

1.1 数字逻辑实验传统模式

在传统的数字逻辑实验中,由实验室向学生提供74系列固定功能标准芯片,学生在了解了实验原理和认识标准芯片功能的基础上,在实验箱上手工接线来实现电路的功能。对于简单的小型逻辑电路而言,这种方式基本上能够保证学生比较容易地完成自己的设计,但当实验电路的规模达到一定程度时,电路的可靠性会大大下降,故障往往是由接线错误如断线等或由芯片接触不良等因素引起。另外,由于各器件之间需要许多连线,一旦改变设计方案,不但需要更换器件,还需要重新进行大量的连线工作,学生在实验过程中会有相当一部分的精力被牵扯进连线和查错等这些琐事中,因此会感到枯燥、乏味。这种模式缺乏灵活性,效率较低,在一定程度上制约了学生实验兴趣的培养和创新能力的发展。这种方法的优点,是便于学生建立起硬件概念,可以将课本上的符号与实际的元器件联系起来,直观、易懂,学生能够掌握典型芯片的基本特性和主要应用,并能养成良好而规范的布线风格,同时熟悉常规的故障调试方法,有利于培养学生细致、耐心和严谨的工作作风[10]。

1.2 基于EDA技术的CPLD实验模式

基于EDA技术的CPLD实验模式是以EDA软件为开发平台,以大规模可编程逻辑器件(CPLD)作为电路载体,以硬件描述语言(VHDL)表达其电路的逻辑关系,学生只需在计算机上先用硬件描述语言编写代码,然后通过编译、下载等步骤下载到CPLD器件中,就可以完成电路的设计[11-13]。用这种方式,学生可以把主要精力放在代码的编写上,避免了因接线错误、芯片接触不良等所带来的问题,使得电路设计从传统的硬件搭接转到了软件设计和仿真调试上来。即使要改变设计,也只需在计算机上进行,然后重新进行编译、下载即可,而不用象传统实验方法那样要更换芯片、检查硬件连线甚至重新搭接电路。同时,CPLD芯片具有极大的灵活性和通用性。由于设计周期短、修改容易且系统可靠性高,利用CPLD的可配置性,再配合适当的外围电路,就可以做出多种不同的应用,这使其成为了符合现代数字系统设计技术发展趋势的新型设计手段。其缺点是,学生往往会缺乏硬件概念,对实物元件缺乏感性认识,实际电路调试等能力得不到很好的训练。

1.3 数字逻辑实验教学模式

在数字逻辑实验课上,我们采用的是传统实验和基于EDA技术的CPLD实验相结合的实验教学模式。传统实验采用的是“自底向上”的纯硬件的设计方法,而基于EDA技术的CPLD实验采用的是“自上而下”的硬件设计软件化的方法。我们在控制好传统实验和CPLD实验比例的基础上,优化实验项目,使得两种方法的实验相辅相成,相互补充,达到软硬结合的目的,学生既能学会用中小规模器件设计简单数字部件,又能掌握基于可编程逻辑器件(CPLD)设计复杂电路的知识。

2 数字逻辑实验平台

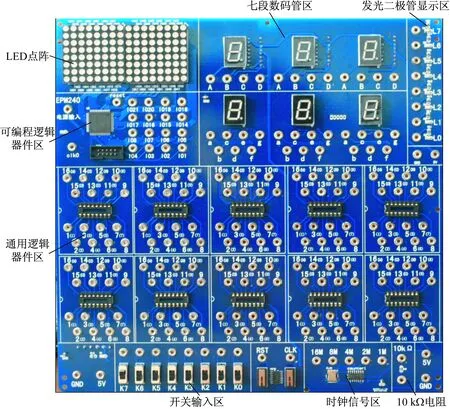

为优化实验教学环境,实现实验教学手段的现代化,我们专门为数字逻辑实验课程设计开发了实验平台。该平台整合了通用逻辑器件的连线实验和可编程逻辑器件实验,配备了齐全的工具设计,实验平台的整体结构见图1。具体来说,它包括:

(1) 通用逻辑器件区。内有10个16脚的双列直插器件的管座,支持实验中的通用逻辑器件(主要是74系列的器件)的安装,每个管座的管脚都被引出到一个台阶插座上,可以通过连接线将管脚连接起来形成所需电路。

(2) 可编程逻辑器件区。内有一片可编程逻辑器件CPLD、时钟输入插座、复位插座、连接USB下载线的插座、电源输入的台阶插座、16个通用输入/输出端口的台阶插座。

(3) 数码管区。有6个七段数码管,3个带译码电路的和3个不带译码电路的。

(4) 开关输入区。有8个拨动开关和2个微动开关。

(5) 发光二极管显示区。有8个发光二极管。

(6) 五组TTL电平时钟信号区。频率分别为16、8、4、2、1 MHz。

(7) LED点阵区。有两片8×8的LED双色点阵,其管脚均已直接与CPLD相连,点阵为红绿双色点阵。

做传统实验时,学生可根据设计的电路选择TTL集成电路芯片的型号,将芯片插在芯片插座上,通过手工连线,再使用开关、数码管或指示灯等来完成分立器件的实验。做CPLD实验时,学生首先以Altera公司的QuatrusⅡ为开发平台,在计算机上用硬件描述语言VHDL完成电路的设计,再通过编译仿真,将.sof文件下载到数字逻辑实验箱的可编程逻辑器件EPM240T100C5中,最后通过简单的连线(开关、数码管、灯等)来实现电路的功能。

3 实验的规划和内容

为使学生既能在有限的课时内高效地完成实验,又能在软硬两方面都得到训练,在数字逻辑实验平台上合理地规划传统实验和基于EDA技术的CPLD可编程逻辑器件实验的比重就显得尤为重要。

图1 实验平台的整体结构

例如,对于仪器的使用、芯片参数的测试等内容,就适合用传统的实验方法来完成,而对于复杂的组合逻辑电路、时序逻辑电路等内容,就适合运用EDA手段来进行实验。另外,还有一些原理上大致相同内容的实验,我们会安排让学生分别用这两种方法来实现。例如,要实现两位加法(减法)电路的设计,可让学生在实验平台上用传统的实验方法来实现,实验过程中要使用的芯片有若干个、导线几十根,学生在接线时容易出现错误,实验的完成进度可能会受到影响,但这对于学生建立硬件概念,对增加对实物元件的感性认识以及提高实际电路调试能力等都是很好的训练,因此该实验的设立是必要的。对于四位加法器的设计实验,可安排学生用CPLD来实现,实验过程中电路的接线复杂程度会大大减少,导线只需十几根即可,主要的工作是通过编写程序代码来完成的。通过这样的实验安排,可让学生亲身体验到用这两种方法来实现大致相同实验目标的不同之处,辨析二者的优缺点,同时软硬两方面的知识也得到了巩固和提高。

目前我们开设的数字逻辑实验有:① 示波器实验;② 与非门电路的测试(传统实验);③ 点亮数字人生(CPLD实验);④ 两位加法(减法)电路设计(传统实验);⑤ 四位加法器设计(CPLD实验);⑥ 计数器设计(CPLD实验);⑦ 串行密码锁设计(CPLD实验);⑧ 定时控制电路的设计(传统实验)。

除数字逻辑实验课程中的内容外,在理论课的最后几周安排了自主选题的大实验[14]。学生通过综合运用在理论课和实验课中所学的知识,自主选题,实现自己感兴趣又有创意的大实验项目。兴趣是最好的老师,有兴趣才会有动力去掌握好理论知识和实验技能,并不断积累经验,在此基础上才会有创新的成果[15]。通过以上这些数字逻辑实验环节(传统实验、CPLD实验、设计型和研究型实验)的设计,学生将会得到较完整的训练,这也为其随后顺利完成“计算机组成原理”、“系统结构”等课程的学习提供了知识保障。

4 考核方式和成绩的评定

客观合理地对学生的实验成绩进行评定是实验教学环节的重要内容之一。我们不以实验最终完成的情况作为惟一的判定标准,而是更加注重学生在实验过程中知识和能力的表现。学生在实验中可能会犯各种各样的技术性错误,只要得到及时的纠正,都不会影响到最终的成绩,因为这些过程都是其知识和能力积累由量变向质变进行转变的必要阶段。实验的主要考核指标包括实验预习报告、实验过程、实验结果、实验报告、实验考试等。对于自主选题的大实验,除要求完成实验报告外,还要组织学生进行公开答辩和演示自己的实验装置,综合给出最终的成绩。

5 结 语

我们在自己开发的数字逻辑实验平台上将传统实验和CPLD实验进行了结合,合理设计和规划了数字逻辑实验教学,目的是发挥传统实验和CPLD实验在实验教学中各自的优势,使学生既能熟悉符合现代数字系统设计技术发展趋势的新型设计手段,又能建立起硬件概念,在实际电路的搭建和调试等方面得到训练,并能培养严谨和细致的工作作风。实践证明,这种基于实验平台的数字逻辑实验教学不仅能够帮助学生很好地理解和掌握理论课上学过的基本原理和知识,而且也使其在软硬件两方面都得到了很好的训练。

[1] 全成斌,杨士强,赵有健,等. 计算机实验教学示范中心的建设[J]. 实验技术与管理, 2009,26(2):110-112.

[2] 薛延侠. “数字电路”实验教学的创新与研究[J]. 实验室研究与探索, 2007,26(2):84-86.

[3] 冼志妙,李廷洪. 数字逻辑电路实验教学改革[J]. 实验室研究与探索, 2004,23(9):75-77.

[4] 唐智强. 计算机专业数字逻辑实验的改革与创新[J]. 实验室研究与探索, 2013,32(10):182-184.

[5] 王振宇. “数字逻辑电路”课程教学改革体会[J]. 电气电子教学学报, 2002,24(2):18-20.

[6] 李永华,李 国. 计算机专业《数字逻辑电路》实验教学探讨[J]. 实验室科学, 2008(1):37-38.

[7] 田 东. 数字电路课程设计的改革与探讨[J]. 实验技术与管理, 2006,23(5):118-120.

[8] 叶雪军. 计算机硬件类课程群实验教学改革[J]. 计算机教育, 2011(9):82-84.

[9] 徐莹隽. 基于开放教学模式的数字逻辑电路实验教学改革[J]. 电气电子教学学报, 2006,28(6):64-66.

[10] 陈莉平,王 红,秦 俭,等. 电子技术课程设计数字部分的一次实践[J]. 电子电气教学学报, 2008,30(2):75-76,79.

[11] 汪 宁,汪朝霞,张迎春. EDA技术在我校数电实验改革中的应用研究[J]. 山东轻工业学院学报, 2011,25(3):64-67.

[12] 高金定,邬书跃,孙彦彬,等. EDA技术创新型实验教学体系的构建与实践[J]. 实验技术与管理, 2011,28(2):158-160.

[13] 崔国玮,李文涛. 基于EDA技术的数电课程设计新模式的探索与实践[J]. 实验技术与管理, 2008,25(1):123-125.

[14] 田淑珍,杨士强. 在硬件实验中培养学生的创新实践能力[J]. 计算机教育, 2012(19):39-41.

[15] 李 慧. 高校开放性实验教学的研讨[J]. 实验技术与管理, 2003,20(5):172-174.

Digital Logic Experiment Teaching Based on Experimental Platform

TIANShu-zhen,QUANCheng-bin,LIShan-shan,YANGShi-qiang

(Department of Computer Science & Technology,Tsinghua University,Beijing 100084,China)

Traditional experiments and EDA technique-based CPLD experiments have their own characteristics in digital logic experiment teaching. Therefore, we try to combine such two kinds of experiments in teaching with the aim of taking full advantage of them. This paper introduces the practice in digital logic experiment teaching based on experimental platform, which is under the guidance of such ideas. We scheduled experimental contents to be performed on the platform developed by us, which considers the ratio of the two kinds of experiments, also arranges the comprehensive experiment with topics selected independently by students, and grades students taking comprehensive performances into consideration. The results prove that the combination of such two kinds of experiments is beneficial to train students in improving their software and hardware application ability, not only in mastering the digital logic course effectively, but also in strengthening the ability of practice.

digital logic; EDA technique; programmable logic devices; traditional experiments

2014-06-23

田淑珍(1966-),女,北京人,学士,工程师,主要从事计算机和电子技术的相关教学工作。

Tel.:13641328575;E-mail:tiansz@tsinghua.edu.cn

G 420

A

1006-7167(2015)05-0195-04