基于EZ-USB FX3 的FPGA 在线配置设计方法

梅茹 卢欢 汕头市超声仪器研究所有限公司 (汕头 515041)

当今,电子技术发展迅速,FPGA 以其集成度高、编程方便、速度快等特点被越来越广泛地应用在各个领域。可重复编程型FPGA 采用SRAM 开关元件,其中每个逻辑块的功能以及逻辑块之间的互联模式都是由存储在SRAM 中的数据决定的。而这种FPGA 中的数据在掉电后具有易失性,故每次重新加电时,FPGA 都要重新加载配置数据,同时只有配置数据正确时FPGA 才能正常工作。本文针对其FPGA 的这种特点,提出了一种比较灵活实用的在线配置方式。

1.系统设计原理

本系统中计算机作为主控设备,配置数据以文件形式存储在计算机中。EZ-USB FX3 作为USB3.0 的接口控制器,利用其通用可编程接口GPIF II 与逻辑器件连接后,产生FPGA 所需的配置信号,这些配置信号再与FPGA 中的专用配置引脚连接形成配置链路。软件通过一定的控制方式,将存储在计算机中的配置数据文件组合成FPGA 能识别到的配置数据以及控制信号,通过配置链路传送给FPGA 完成整个FPGA 的配置。其系统框图如图1 所示。

图1. 系统实现框图

1.1 EZ-USB FX3 工作模式

EZ-USB FX3 是CYPRESS 公 司 的 高 带 宽USB3.0 外设控制器。它具有一个可实现5-Gbps USB3.0 数据传送能力的通用可编程接口GPIF II,数据传输速率可高达每秒400 兆字节,这个通用可编程接口GPIF II 可以使EZ-USB FX3 能与任何处理器或FPGA 直接通讯。

本设计中,EZ-USB FX3 的通用可编程接口GPIF II 在上电时被设置成Slave FIFO 接口模式。这种模式使得EZ-USB FX3 成为从设备,而外部FPGA 作为主设备。由于在上电时FPGA 处于还没有配置的状态,即使作为主设备也无法控制EZ-USB FX3 的GPIF II 接口,因此需要设计额外的硬件电路,一方面来满足在FPGA 配置完成前对GPIF II 接口的控制,另一方面要产生FPGA配置所需信号线。

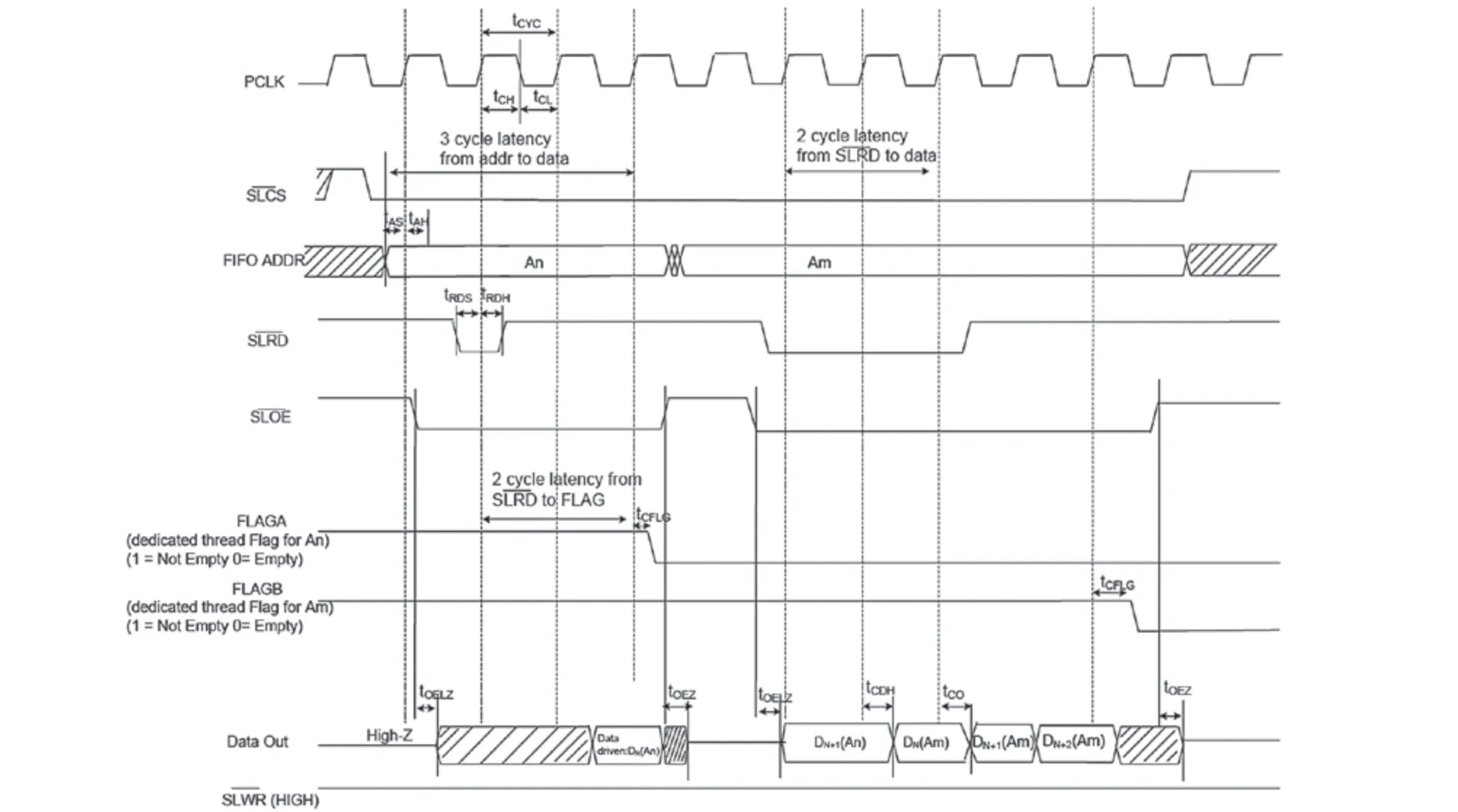

在FPGA 配置过程中,EZ-USB FX3 的GPIF II 接口需要从计算机传输数据到FPGA 的配置端口,此时,GPIF II 接口信号需要满足同步Slave FIFO 读的时序要求,如图2 所示。

1.2 FPGA 在线配置模式原理

Xilinx 公司的FPGA 有多种配置模式,各种配置模式由配置模式引脚M0、M1、M2 的连接方式来决定。而Spartan-6 系列FPGA 只有M0 和M1 两个配置模式引脚,只需要设置这两个引脚的状态即可决定其配置模式。

表1 中列出了Spartan-6 系列FPGA 的各种配置模式,同时还列出了各模式对应的配置模式引脚状态和配置数据位宽以及配置时钟传输方向。

图2. GPIF II 接口同步Slave FIFO 读时序[1]

本设计中,为了实现计算机端到FPGA 端的在线配置,FPGA 的配置模式拟采用从串(Slave Serial)的配置模式,此时需要将FPGA 的M0和M1 两个信号引脚连接成高电平状态,同时为了保证在配置过程中FPGA 的其他引脚状态稳定,可以将HSWAPEN 信号引脚拉低到地,此时FPGA 的所有通用引脚会通过上拉电阻连接到各个板块的电源信号。

当FPGA 采用从串配置模式时,除了M0和M1 两条配置模式信号外,还有6 条配置信号线,分别为PROG、CCLK、DIN、DOUT、INIT和DONE。其中,PROG 为FPGA 的一条异步控制输入信号,当它为低电平时,复位FPGA 同时初始化配置存储器,当这条信号由低电平变为高电平时,FPGA 开始配置;INIT 作用很多,在配置初期低电平,表示正在清除配置存储区的内容,当配置进行中时,若该信号变低则表示CRC 校验错误;CCLK 为配置时钟信号,根据配置模式的不同,其时钟源也不同;DIN 为配置数据输入信号;DOUT 为配置数据输出信号,当串联多个FPGA时,该引脚输出的配置数据作为下一个FPGA 的输入数据,若系统中只有一个FPGA 则该信号可忽略;DONE 信号在配置过程中为低电平,当配置完成后则会变为高电平。

表1. Spartan-6 系列FPGA 配置模式[2]

图3. 配置信号时序图

为了保证FPGA 能够正常配置起来,这几条配置信号需要满足一定的时序关系。

图3 中,t1 为配置清空期;t2 为配置初始化;t3 为配置时钟周期。

2.硬件设计

本设计中,为了产生FPGA 需要用到的配置信号,同时为了满足GPIF II 接口在SLAVE FIFO 读模式下的时序要求,硬件电路拟采用SN74LVC74A、SN74LVC374A、SN74LVC245A三个逻辑器件与EZ-USB FX3 搭建实现。配置信号产生的硬件电路连接如图4 所示。

图4. 配置信号产生硬件电路

在对FPGA 进行配置时,GPIF II 使用线程1 进行配置数据的传输,此时FLAGB 表示当前是否有数据从PC 端传到FPGA 端,若有配置数据传输时,FLAGB 为高电平,若配置数据传送完成则FLAGB 为低电平。SN74LVC74A 是一片有两路上升沿触发的锁存器,其输出端有两种状态,分别为锁存输入的状态或对输入状态取反。SN74LVC374A 是一片8 路上升沿触发的锁存器。为了实现GPIF II 接口的读数据传输,需要将GPIF II 接口的SLRD 和SLOE 信号置为低电平才能从GPIF II 接口读出数据,同时SLOE信号需要延时SLRD 信号两个时钟的时间才能读出正确的数据。本设计中,当FLAGB 信号有效时,锁存器SN74LVC74A 将FLAGB 状态锁存并取反,同时利用SN74LVC374A 得到能满足时序要求的SLRD 和SLOE 信号。

为了简化电路的设计,对于软件的控制设置了输出信号的通道,而没有输入信号的通道,即软件通过GPIF II 接口的数据引脚D0、D1、D2发出数据控制PROG、CCLK、DIN 三个信号,而软件不能读取INIT 和DONE 信号状态。这就需要对配置过程中的两个状态进行检测,一是PROG 由低电平变为高电平以后FPGA 初始化完成状态,通过测试得到初始化时间t2 大约1ms 左右,可以控制软件在PROG 信号变为高电平后自行延时1ms 的时间,然后再输出CCLK 和DIN信号来开始配置FPGA;二是检测数据接收完成后配置状态是否成功,此时可以在软件发送完FPGA 的配置数据后,对FPGA 中事先规定好的一些寄存器或状态位进行操作,一旦这些寄存器或者状态位能够被正确的操作或者读取,则表明FPGA 配置是成功的。

本设计中软件除了需要下载三路配置信号外,还需要控制SN74LVC245A 的使能端,即图4 中的OE 信号。配置过程中,需要通过GPIF II 接口的数据引脚D3 下载数据控制SN74LVC245A 的使能端有效,以保证能够顺利的进行配置数据传输。当配置数据发送完成后,需要额外的发送一组数据来控制SN74LVC245A 的使能端无效。当SN74LVC245A 的使能端无效时,配置链路就会断开,GPIF II 接口的SLAVE FIFO 读控制信号SLRD、SLOE、SLCS 会切换到由FPGA 端来控制。

3.软件设计

本设计中,配置控制信号PROG、配置时钟CCLK 以及配置所用的数据DIN,相对软件来讲其实都是数据。软件只需要将数据组织好,通过USB3.0 向GPIF II 接口的线程1 写入数据即可。

根据电路的设计要求,配置清空期需要首先设置OE 为0,设置PROG 信号为0,一段时间后设置PROG 信号为高,此时CCLK 和DIN 信号无关紧要可以一直设置为1。配置清空期t1 的时间大约为300ns ~500us,本系统中 GPIF II接口时钟为50MHz,每发送一个数据最少需要20nS 的时间,可以通过发送至少15 个数据达到延时的目的。配置初始化时期需要软件自行延时1~100mS 来完成配置初始化。表2 简单示例了数据的发送情况。

表2. 初始化时配置数据组合形式

当发送配置数据时,软件需要根据读取的配置文件,将文件中的配置数据和配置所需的时钟整合在一起产生所需的配置时序。配置时钟信号CCLK,需要软件循环设置一个数据为0 一个数据为1 来得到;配置数据DIN,需要在一个配置时钟循环中保持配置数据的一个位不变,在下一个配置时钟循环中输出下一位。

图5 对如何将配置数据0xA5(1010_0101)整合到所需信号的时序做了描述。

由于FPGA 的配置时钟一般在1MHz~15MH之间,而EZ-USB FX3 中的GPIF II 总线时钟为50M,按照图5 中数据形式,一个时钟循环只有一个1 和一个0 占了两个数据,产生出来的时钟达到25MHz,故图5 中数据产生的时序是不能满足FPGA 配置的时序要求的。为了达到降低配置时钟的要求,需要设置时钟循环长度是可以变化的,例如设定一个时钟循环为4 个0 和4 个1,则配置时钟为6.25MHz,才可以满足FPGA 对配置时钟频率的要求。

软件进行多次的循环读取数据进行转换,直到将整个配置文件的所有数据都转换和输出到EZ-USB FX3 以后,再设置OE 为高电平,之后则完成了所有的数据输出和时序。最后的数据形式如表3 所示。

当所有配置数据传输完成后,根据硬件电路连接可知,此时GPIF II 接口的读写控制信号转为由FPGA 进行控制,此时可以对FPGA 中既定的寄存器或者状态位进行操作,从而可以判断配置是否成功。

图5. 发送配置数据0xA5 时数据组合时序

表3. 配置数据传送完成后数据组合形式

4.结论

在电路调试过程中,可能出现配置完成后读FPGA 中既定的寄存器内容不正确的情况,此时需要软件重新下载配置数据进行配置。若尝试多次后依然不能正确的读取FPGA 既定寄存器中的内容,则软件需要提示配置出错,此时需要检查电路连接或配置数据是否正常。经过调试,最终能正确的将配置数据传送给FPGA,配置完成后FPGA 能正常开始工作。

综上,采用这种在线配置的方式,能够灵活的对FPGA 逻辑设计进行升级,对于硬件升级比较频繁的系统具有一定的实用价值。

[1] Rama Sai Kvishna V. 利用EZ-USB FX3TM 从设备FIFO 接口进行设计[DB/OL]. www.cypress.com. 文档编号:001-92219 版本**.

[2] Spartan 6 FPGA Configuration User Guide[DB/OL]. UG380(V1.0) June 24,2009. www.xilinx.com