PICO384非制冷红外焦平面驱动成像方案研究

胡仕明,陈益新

PICO384非制冷红外焦平面驱动成像方案研究

胡仕明,陈益新

(南京理工大学 电子工程与光电技术学院 南京 210094)

非制冷红外焦平面热像仪可用于将人眼不可见的红外光信号转化为可见光图像,具有无需制冷、便携式和成本低的优点。对法国ULIS公司在2012年推出的带I2C标准片内接口的17mm像元尺寸型号为PICO384的非晶硅焦平面探测器进行了驱动成像研究,主要工作包括硬件电路板的设计和基于FPGA的驱动成像程序开发,最终达到了预期结果获得了清晰的红外图像。文中详细介绍了硬件系统的组成,对驱动程序核心模块的设计进行了说明和给出仿真验证结果,并就软硬件设计过程中的几个重要问题进行了探讨。

PICO384;非制冷;红外焦平面;红外成像

0 引言

PICO384为法国ULIS公司生产的一款非制冷凝视型红外焦平面探测器,并首次做到将在许多电子器件中广泛使用的I2C(Inter Integrated Circuit bus)接口集成到探测器内部,从而更便于器件的开发应用。凝视型红外焦平面[1-3]的优点有:①热灵敏度高:凝视红外焦平面探测器通过提高积分时间可获得画质优良的热或红外图像;②帧频高:凝视红外焦平面探测器采用电子扫描读出信号,速度比光机扫描快;③体积小、重量轻。ULIS公司是基于非晶硅技术的非制冷红外焦平面生产的领导者,专注于设计和制造高性能红外成像探测器并用于热成像仪、安防、交通和军事应用等领域,使得消费电子和红外器件生产厂家能够大批量生产便携式、低功耗和低成本的红外相机[4]。

目前国产热像仪的核心器件红外焦平面大部分依赖国外进口,而国产的红外焦平面探测器在分辨率、像元间距和灵敏度等方面性能与国外相比还有一定差距。在成本上,由于ULIS公司的PICO384焦平面已实现量产,其单片价格也比国产相同分辨率类型产品价格要低,且由于在片上集成了I2C通信接口,其驱动开发也更容易实现。为此本文将展开对PICO384型红外焦平面的具体研究。

1 PICO384红外焦平面介绍

该探测器是法国ULIS公司生产的一款先进的、高可靠性、体积小、重量轻、功耗低的非制冷红外焦平面探测器,采用非晶硅(-Si)微测辐射热计技术将红外辐射转化为电信号来用于热像仪成像[5]。探测器内部采用了硅读出集成电路,像素阵列集成在一个专门设计的真空陶瓷封装中。其外形封装如图1所示。

图1 ULIS PICO384型非制冷红外焦平面外形封装

主要技术参数如下:

• 光谱响应:长波红外(8~14mm)

• 工作温度范围:-40℃~+85℃

• 像素分辨率:384×288

• 像素尺寸:17mm

• 总功耗:<65mW(模拟功率)

• 供给电压:数字1.5V,模拟3.6 V

• 读出方式:逐行读出

• 模拟视频输出动态范围:0.5~2.9V

• 灵敏度:14.8 mV/℃

• 标称帧频:50 Hz

• 输入时钟:主时钟(MC),最大14 MHz

• 输出时钟:像素时钟(PSYNC),行同步信号(HSYNC),帧同步信号(VSYNC)。

PICO384红外焦平面与ULIS公司以往推出的焦平面的不同之处在于它是通过I2C对内部的寄存器进行配置来驱动焦平面工作的,这样就节约了芯片外围的配置引脚,简化了芯片的驱动操作。焦平面内部总共用来读写的寄存器数目有20多个,通过I2C通信对相应寄存器写入数值,就可以设定焦平面的积分时间、窗口大小、扫描方式、行间间隔、帧间间隔、偏置电压等参量。正确配置好内部寄存器后,在复位信号和时钟信号的控制下,焦平面输出模拟视频信号,像素时钟同步信号,行同步信号和帧同步信号。然后就可以以此为基础开始后续的模数转换,数字图像处理显示等工作。

2 焦平面驱动成像设计

2.1 系统整体结构设计

PICO384非制冷红外焦平面阵列(IRFPA)驱动成像系统结构如图2所示。该系统主要由电源系统、FPGA芯片、A/D转换器、D/A转换器和数据/程序存储器等组成,可实现对IRFPA的数据通信和程序控制以及对其输出的模拟视频信号进行采集、数字图像处理和视频合成等功能。

2.2 电源系统模块

PICO384焦平面所需的供电电压主要有:模拟电压输入3.6V,数字电压输入1.5 V,偏置电压VSK固定3.6V输入以及两个可调偏压GSK和GFID。其中GSK涵盖的可调电压范围需满足1.7~3.6V,GFID涵盖的可调电压范围需满足1~2.9V。另外,CTIA(Capacitance Trans-Impedance Amplifier)参考电压VBUS无需外部提供,可通过配置内部寄存器产生2.3V固定电压,所有电压输入管脚端口都必须并联100nF和10mF的两个解耦电容。

本系统中选用的电源芯片均为Linear公司出产,所选的芯片型号有:LT1086-3.6,LT1963-1.5,LT1129-5,LT1963-3.3,LT1963-2.5,LT3021-1.2和LT1762。其中LT1086-3.6和LT1963-1.5分别产生固定3.6V和1.5V电压用于给焦平面提供固定电压输入;LT1762为可调电源芯片,通过外接电位器调节可提供给焦平面连续可调的偏置电压输入;LT1129-5,LT1963-3.3,LT1963-2.5和LT3021-1.2分别产生固定5V,3.3V,2.5V和1.2V来用于给FPGA芯片,A/D转换器和D/A转换器等供电。

图2 PICO384 非制冷IRFPA驱动成像系统结构

2.3 FPGA硬件平台及外围模块

FPGA(Field Programmable Gate Array)即现场可编程门阵列[6],具有灵活性和并行性的特点,适应于逻辑设计,逻辑粘连,数字信号处理和实时控制等领域。本系统选用Altera公司Cyclone Ⅲ系列型号为EP3C55F484的FPGA芯片作为主处理器,其逻辑资源[7]介绍如表1所示。FPGA完成的功能主要有:①时钟管理。将晶振输入的24M时钟通过FPGA芯片内部锁相环进行分频输出,供给焦平面,A/D转换器和D/A转换器使用。②驱动控制。完成对PICO384 IRFPA的程序控制和数据通信,以及驱动电机控制挡板进行非均匀校正等。③信号处理。将A/D转换器采集的数字图像信号依据焦平面输出的同步时钟时序要求进行处理和缓存等。④视频合成。将经过处理缓存的图像数据根据电视PAL制协议输出,然后再经过外部D/A芯片编码即可送到显示器显示。

外围模块主要包括A/D转换器、SRAM、EPCS和D/A转换器等。其中A/D转换器选用ADI(Analog Devices,Inc.)公司的AD9240模数转换芯片,用于将PICO384输出的模拟视频信号转化为14位的数字信号输送给FPGA。SRAM选用Cypress公司型号为CY7C1061AV33产品,容量为1M×16bit,用于缓存非均匀校正时存储的一帧背景图像数据。EPCS可用于上电时对FPGA的数据配置。D/A转换器选用ADI公司的ADV7123芯片,可用于将FPGA处理后的图像数据进行PAL制编码输出。

2.4 PICO384驱动程序设计

PICO384红外焦平面驱动程序设计的关键部分主要是对I2C通信模块的程序编写。I2C为内部IC控制的双向串行总线,是微电子通信控制领域广泛采用的一种总线标准[8]。它是同步通信的一种特殊形式,具有接口线少,控制方式简单,器件封装形式小,通信速率较高等优点。在设计时需要依据焦平面的I2C读写通信协议和内部读出集成电路控制寄存器各项参数设定的意义,编写FPGA程序来配置焦平面内部寄存器,从而使得焦平面按照设定的参数值进入预期的工作状态。

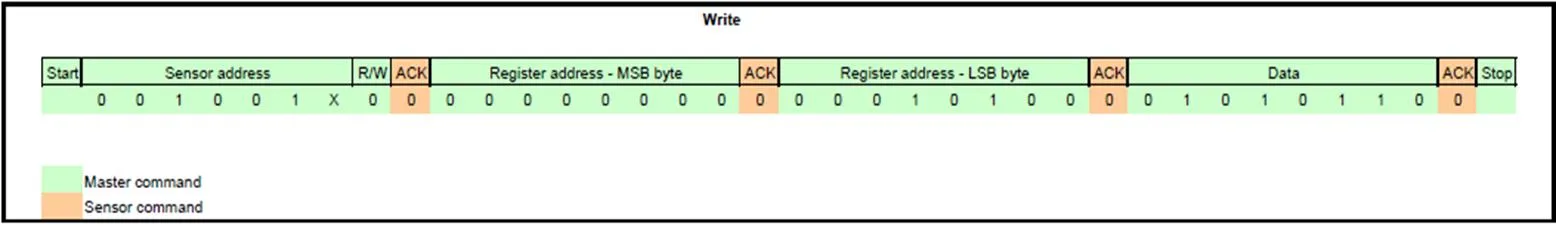

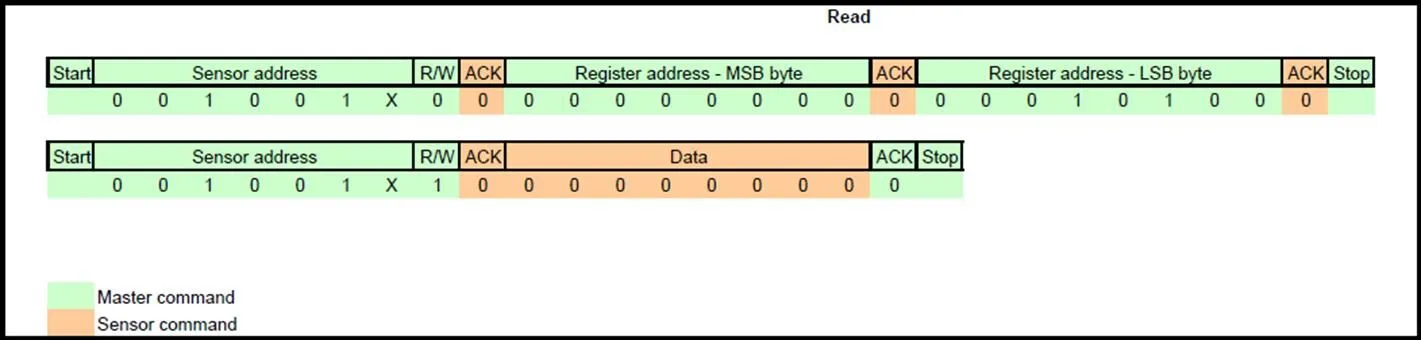

焦平面I2C通信的写时序和读时序分别如图3和图4所示。执行写操作时FPGA先向PICO384发送器件地址和写命令,等待焦平面返回一个低电平应答信号,随后FPGA再分别发送16位寄存器地址的高8位和低8位地址数据,之后就可以将8位的寄存器设定值数据写入到指定的控制寄存器当中了,在此过程中,每次从FPGA向PICO384成功写入一个8位数据后,PICO384会向FPGA返回一个低电平应答信号。执行读操作时前一部分与写时序类似,也是先从FPGA向PICO384发送器件地址和写命令,随后发送地址数据,只是在发送完地址数据和接收到应答信号后就停止,然后再重新开始并发送器件地址和读命令,就可以读出和接收指定寄存器中的数据了。

PICO384 IRFPA内部单个寄存器的位宽指定为8位,可通过I2C串行接口与外部进行通信。所有的寄存器大体分为两类:一类是只读寄存器,其内部数据在出厂时已设定好,不能再次通过程序更改;另一类为可读写寄存器,可由用户通过编程读取和重新配置。其中只读寄存器有:DACGFID,DACGSK_A,DACGSK_B,FEEDBACK,READ_ ONLY_A,READ_ONLY_B和READ_ONLY_C。读取DACGFID寄存器内的数据就可用于计算GFID输入端的偏压设定值,读取DACGSK_A和DACGSK_B寄存器内的数据则可用于计算GSK输入端的偏压设定值,相应的计算公式分别如式(1)、式(2)所示。其余的寄存器均为可读写寄存器,通过I2C通信对相应寄存器写入数值,就可以设定焦平面的积分时间,窗口大小,扫描方式,行间间隔,帧间间隔,VBUS偏压等参量。

表1 EP3C55F484器件逻辑资源

图3 PICO384 I2C写时序

GFID(V)=0.01025 [DACGFID]+0.777V (1)

GSK(V)=0.00254×[DACGSK]+0.416V (2)

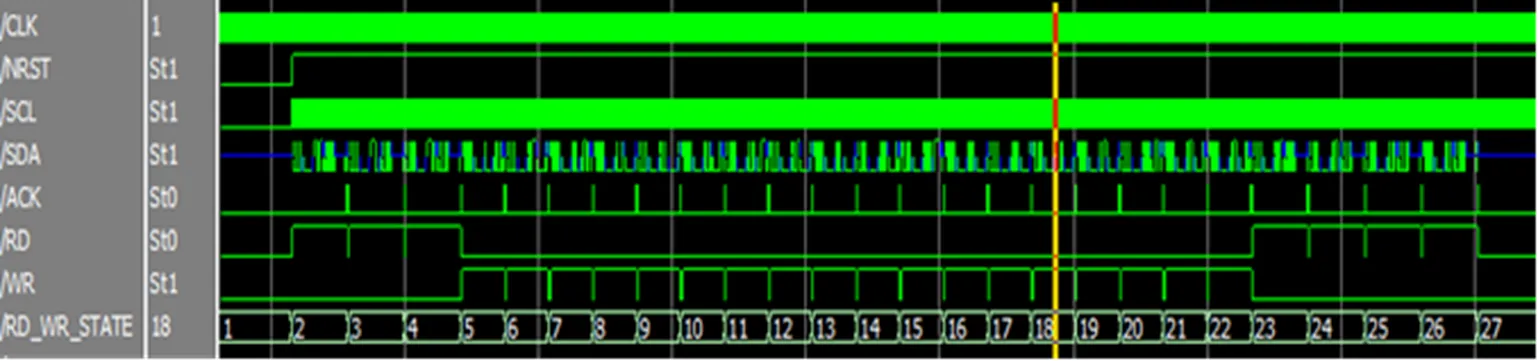

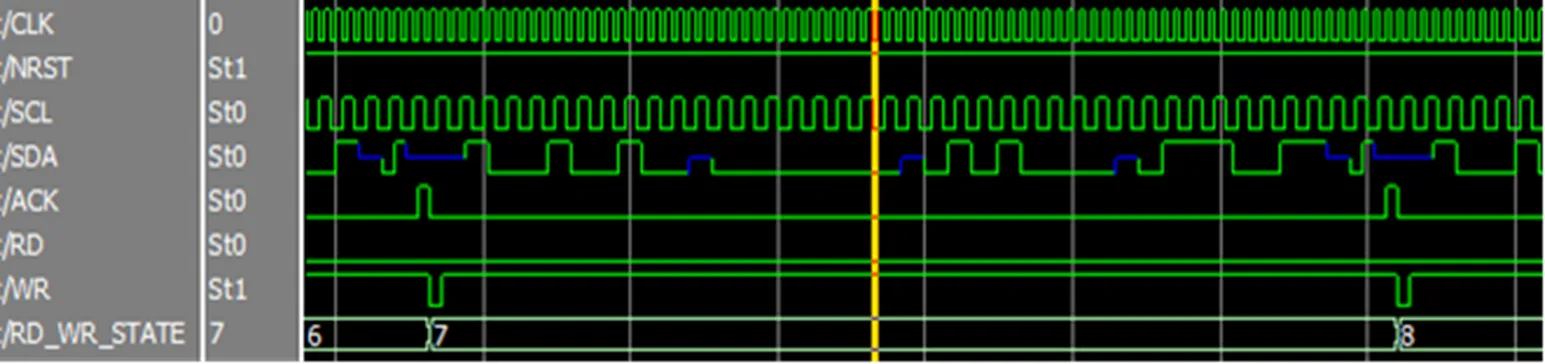

在本设计中通过参照焦平面的I2C读写时序,完成了对I2C通信模块的程序编写,实现了对PICO384内读出集成电路控制寄存器的读写操作。使用ModelSim仿真软件对I2C程序模块进行仿真,得到的波形如图5所示。其中RD_WR_STATE为I2C读写状态机,数值为1代表空闲状态,数值为27代表停止状态,表明对焦平面内部寄存器的配置操作已完成。当RD_WR_STATE数值为2~26时,表明当前正处于对焦平面内部各寄存器的读或写状态。RD为高电平代表正对当前寄存器进行读操作,WR为高电平代表正对当前寄存器进行写操作。图6为对图5进行波形放大后显示对单个寄存器的写时序,此时RD_WR_STATE数值为7,RD为0,WR为1,正对寄存器地址为0×0050的 INTEGRATION_B寄存器写入数据0111_0011,由波形图可以验证此程序模块的功能得到了正确实现。

3 红外成像结果

在正确配置好PICO384 IRFPA内部寄存器后,焦平面开始进入正常的工作状态,在同步时钟的时序约束下输出模拟视频信号,再经过AD9240采集转化为14位宽的数字信号输送给FPGA,FPGA依据焦平面输出的3个同步时钟:PSYNC,HSYNC和VSYNC对AD9240传送过来的数据进行选择性地接收并缓存连续的一帧图像数据到内部双口RAM中。如果此刻是处于电机带动挡板进行单点非均匀校正模式下,还会同时将该情形下的一帧背景图像数据存储到外部SRAM中,以便之后用于实时的校正处理。之所以采用单点非均匀校正而不是两点校正,是因为此种方式对FPGA的处理资源占用较低,且只需一片外部SRAM芯片,比较容易实现,同时也能获得较好的图像质量。

图4 PICO384 I2C读时序

图5 I2C通信程序模块的ModelSim仿真波形

图6 图5中单个寄存器的写时序经放大后的波形

为了将缓存的红外图像数据以PAL制输出显示,需要依据PAL制协议在FPGA内编写视频合成模块,产生时钟信号,复合同步信号、复合消隐信号和有效数据输出,并控制好各信号间的时序关系,然后经过ADV7123编码成PAL制视频流输出,就可以连接到外部显示器上显示。在完成整个硬件系统的设计和软件程序的开发后,最终获得了清晰的红外成像结果,如图7所示。

图7 PICO384 IRFPA成像显示

4 几个重要问题的探讨

1)负载阻抗的匹配。根据PICO384用户手册要求,VIDEO模拟视频输出端的负载电阻要大于1MW,负载寄生电容要小于20 pF。为此,设计时在VIDEO模拟输出端连接了一个由有源放大器构成的电压跟随器,满足了参数要求。

2)积分时间的设定。由于一行的像素数为384个,行与行之间的间隔至少为17个PSYNC,总共有288行,帧频50Hz,并且主时钟MC频率为像素时钟频率的2倍,所以MC的最小频率值为:(384+17)×288×50×2=11.5488MHz,本系统设计中选择的主时钟频率为11.56MHz,基本满足每秒50帧的设计要求。此时的积分时间,当TINT(Integration time)≤(384-13)=371个PSYNC时,最大为(371×2)/11.56=64.2ms。当TINT>371时,如果主时钟不变,则此时破坏了每秒50帧的时序要求,不可行;如果提高主时钟频率(最大14MHz),则在各项约束下通过计算可获得的最大积分时间为65.16ms。本系统在设计时设定TINT值为371,积分时间为64.2ms。

3)乒乓操作的弃用。本系统设计中,在FPGA内缓存了一帧红外图像数据,用于解决数据接收处理与外部PAL制读出显示不同步的问题。如果采用乒乓操作,在一个数据缓存模块中缓存一行数据的同时读取另一个数据缓存模块中已缓存的一行数据,两个缓存模块交替进行读写,以流水线的方式工作,就可以大量节省FPGA内部的存储空间,总共只需要缓存2行数据就可以替代缓存一帧共384行所占用的存储空间。只是由于乒乓操作对焦平面工作时序和PAL制协议两者协同工作有时序同步的要求,焦平面输出一行数据的时间要与PAL制一行显示的时间相同(为64ms),焦平面输出帧间间隔也要对应于PAL制式的场消隐时间,在经过改变行间间隔和帧间间隔并进行计算推导后,排除了这种方案的可行性。

5 结论

通过对法国ULIS公司PICO384非制冷红外焦平面进行研究,我们完成了整个硬件系统的设计和软件程序的开发,实现从焦平面到热像仪的完整的设计成型过程,并获得了清晰的红外成像结果。整个系统具有便携式和低功耗的优点,对热像仪生产厂商而言具有一定的借鉴和实用价值。

[1] 蔡毅, 王岭雪. 红外成像技术中的9个问题[J]. 红外技术, 2013, 35(11): 678-679.

[2] Dieter Lohrmann, Roy Littleton, Colin Reese, et al. Uncooled long-wave infrared small pixel focal plane array and system challenges[J].,, 2013, 52(6): 061305.

[3] Jean-Luc Tissot, Sébastien Tinnes, Alain Durand et al. High -performance uncooled amorphous silicon video graphics array and extended graphics array infrared focal plane arrays with 17-mm pixel pitch[J].,., 2011, 50(6): 061006.

[4] Carol Leslie. ULIS debuts I2C infrared sensor Pico384ETM[EB/ OL] [2012-04-24]. http: //www. ulis-ir. com/ uploads /news/ ULIS%20120424%20Pico384E%20EN%20FINAL. pdf.

[5] User guide PICO384TMLWIR imaging sensors[Z]. Preliminary Technical Specification, 2014.

[6] 王诚. Altera FPGA/CPLD设计(基础篇)[M]. 北京: 人民邮电出版社, 2005.

[7] Altera Corporation. Cyclone III Device Handbook[EB/OL][2012-08- 03].http://www.altera.com/literature/hb/cyc3/cyclone3_handbook.pdf.

[8] 夏宇闻. Verilog数字系统设计教程[M]. 北京: 北京航空航天大学出版社, 2008.

Research on Driving and Imaging Project of PICO384 Uncooled Infrared Detector

HU Shi-ming,CHEN Yi-xin

(&,,210094,)

Uncooled infrared focal plane thermal imager can be used to convert the human eye invisible infrared light signals into visible light images which has the advantages of eliminating the need for a cooling system, portable structure and low cost. A research is made on driving and imaging of PICO384 amorphous silicon(-Si) infrared detector which is a new product launched by the French company ULIS in 2012 with I2C interface and 17mm pixel pitch. The main work includes the hardware design and driver and imaging development based on FPGA, and ultimately achieves the expected goal of obtaining clear infrared images. This paper introduces the constitution of the hardware system in detail. The core module of driver program is described and verified by simulation. And finally several important problems in the process of software and hardware design are discussed.

PICO384,uncooled,infrared focal plane array,infrared imaging

TN215

A

1001-8891(2015)08-0680-05

2015-01-28;

2015-02-28.

胡仕明(1991-),男,湖南衡阳人,硕士,主要从事红外成像、差分视频传输技术的研究。E-mail:hsmnjust@sina.com。