TMS320VC5416与单片机AT89C51通信设计

李胜勇(厦门蒙发利科技(集团)股份有限公司,福建厦门 361008)

TMS320VC5416与单片机AT89C51通信设计

李胜勇

(厦门蒙发利科技(集团)股份有限公司,福建厦门361008)

摘要:给出了一种实现DSP TMS320VC5416与单片机AT89C51通信设计的方法,在分析TMS320VC5416串行口特点和AT89C51串行通讯的基础上,进行TMS320VC5416与AT89C51串行通信设计,提出了电平匹配,通信协议匹配和波特率匹配的方法,该方法对实现DSP与AT89C51的通讯具有指导意义。最后给出了部分程序流程和实现方法。

关键词:单片机;DSP;串行通讯;程序设计

0 引言

随着家电性能的不断提高,数据处理的也越来越多,对处理速度的要求也越来越高,原有以MCU为核心的系统,逐渐不能满足要求,因此,具有高速处理数据的DSP芯片,逐渐开始应用。而通过DSP处理的数据往往需要传输给MCU进行运动控制,所以,DSP与MCU的通信设计就成为各种家电产品必须的技术要求。

TMS320VC5416 DSP是TI公司的一款高性能16位定点DSP,具有的McBSP,即多通道缓冲串口能够与同步通信串口外部设备进行通信。但对于AT89C51单片机来说,并无同步通信接口,所以当320VC5416使用McBSP串口与AT89C51通信时,将McBSP串口进行一定扩展硬件的情况下,将同步变为异步进行通信,充分利用DSP片上资源,硬件系统简化可行。

1 TMS320VC5416多通道缓冲同步串行口McBSP特点

TMS320VC5416具有3个全双工、多通道、高速缓存串行口,每个串行口最大可以支持128通道。McBSP支持SPI协议,它的主要特点是:(1)可全双工串行通讯;(2)最大可选择32位数据宽度,允许传输连续数据流;(3)帧同步信号可以为数据发送和接收提供独立支持。图1所示为McBSP的内部结构[1]。

其结构由控制通路和数据通路两部分组成,并有7个引脚可以连接外部器件。接收引脚DR,通过数据总线以接收数据;发送引脚DX,与McBSP相连接发送数据;接收帧的同步引脚为FSR,发送帧的同步引脚为FSX;接收时钟引脚为CLKX;在时钟信号和帧同步信号的控制下,外部器件与发送DX引脚和接收DR引脚直接通信。对McBSP的操作,内部CPU通过16位控制寄存器,以片内外设总线访问控制,McBSP接口信号如表1所示[2]。

图1 McBSP内部结构

表1 McBSP接口信号

产生帧同步信号和产生内部时钟,控制此类信号和选择多通道等构成了控制通道任务。由控制通道产生的中断信号发送给CPU,DMA控制器接收同步事件通知,如表2所示[3]。

McBSP有两种工作模式:第一种工作模式中,当(R/X)MC⁃ME=0时,类似于在5410,MCB⁃SP正常32位通道默认选择。第二种工作模式中,当(R/X) MCME=1时,它拥有128通道选择能力。多通道控制寄存器的位9,即(R/X)MCME,被用作128通道选择是能位。一旦(R/X)MCME=1,12个新的寄存器被用作控制128通道。MCBSP中的时钟停止模式提供了串行口兼容协议。时钟停止模式工作时,每帧只有单一图像或字节。MCBSP提供的字节可编程位8,12,16,20,24或32位。当MCBSP设置工作在SPI模式时传送器和接收器一起工作在主或从存储器。虽然BCLKS管脚在PGE和GGU没有封装,但是芯片仍能够同步到外部时钟源。BCLKX或者BCLKR可以当作外部同步的频率采集器。为了适应这种选择频率采样时钟模式扩展出来的位于PCR上。

表2 McBSP CPU中断和DMA同步事件

2 AT89C51的串行通信

AT89C51具有的数据通信方式为串行和并行。并行通信方式是多位数据同时传送的通信。其特点是速度快,但传输距离短,占用单片机I/O口过多的缺点。串行通信是指数据一位一位顺序传送的通信方式,它只需要一对数据线,具有传输距离远,存在数据传送速度低的缺点。这两种通信方式示意如图2所示[4-5]。

串行通信有两种基本通信方式,即异步通信和同步通信,其传输方式又分为单工、半双工和全双工方式。

图2 两种通信方式

AT89C51单片机具有可编程的全双工通用异步接收/发送器(UART),可用于串行通信,由TxD(P3.1)脚发送数据,由RxD(P3.0)脚接收数据。串行口的数据发送和接收操作都是通过特殊功能寄存器中的数据缓冲寄存器SBUF进行的,两个数据缓冲器SBUF是独立的,一个用于接收,一个用于发送,它们的地址都是99H,对发送缓冲器写以实现发送,对接收缓冲器读以实现接收。接收缓冲器是双缓冲的,以避免接收的前后两帧数据重叠问题,AT89C51的串行通信口有4种工作方式,分别是0~4方式,0方式用于I/O扩展或同步传输,由串行口控制寄存器SCON中的选择位来确定选用的工作方式。1方式主要进行定义串行通信的为8位异步通信串口。一帧信号的长度为10位:包括低电平的起始位1位,数据位8位,低位在先,高电平停止位1位。波特率可变。

3 TMS320VC5416与AT89C51串行通信设计[4-8]

(1)TMS320VC5416与AT89C51电平问题

TMS320VC5416的I/O引脚的逻辑电平是3.3 V,而AT89C51采用5 V逻辑电平。320VC5416最小输出高电平为2.4 V,而89C51最小输入高电平为2.0 V。因此AT89C51的输入能够直接连接到320VC5416的输出。但是320VC5416输入最大高电平是3.6 V,而89C51的高电平输出一般都超过4.6 V。所以AT89C51的输出和320VC5416的输入在电平转换后,才能连接。对于引脚多的芯片,采用专用电平转换芯片,如TI 74LVC16245A是较好的选择。采用分压电阻进行转换,可以简化设计。连接如图3所示。

图3 TMS320VC5416与AT89C51串口连接

(2)串口协议

如图3所示,时钟信号并没有在通路中显示,由AT89C51的低速串行口与TMS320VC5416的高速McBSP端口不匹配,将McBSP传输多个位合并成AT89C51的一个位,这样输出/输入速度一致。

在异步方式下AT89C51串行口的工作方式有4种。这里采用方式1,设置为8位异步通信口,每帧数据有10位:1位低电平起始位,数据位是8位,1位高电平停止位。在工作方式1下,串行口的89C51与C5416通信。发送数据时,C5416的McBSP端口首先对数据进行编码如下:将数据的每位扩展成完全相同的16位,组成一个字,即“0”扩展成为“0000”,“1”扩展成为“FFFF”,这样一个字的8位就被扩展成为8个具有相同16位的字。同样,起始标志为16位0的数据“0000H”放在每帧的前面,结束标志的16位1的数据“FFFFH”放在每帧的后面。DSP的McBSP高速端口接收到数据之时,将接收的1个帧作为AT89C51数据的1个字节,设置接收数据格式是每帧为10个16位字。共计160个位。在接收到一帧的完整数据之后,C5416再根据前面设置的编码规则解码后,就可以得到正确的数据。

发送数据时,AT89C51执行指令写入数据到SBUF,就启动了发送串行数据,由TXD发送数据,发送一帧结束后,发送中断标志TI被置位;接收数据过程中,AT89C51在RI中断标志位为0的情况下,REN置位就启动一帧接收数据的过程,并使数据进入移位寄存器,并加载到SBUF,同时置位RI。

AT89C51的数据传输是以低电平时钟为起始位,在输入时320VC5416的McBSP端口可用此低电平为320VC5416同步信号的输入帧;在输出时,由McBSP的采样率发生器发生和输出。

(3)波特率

上述论述中将320VC5416端口McBSP信号的一个16位字当作AT89C51的一个位,即AT89C51的一个位发送数据被320VC5416的McBSP读16次,而320VC5416的McBSP的16位发送数据只被89C51读1次,因此AT89C51波特率需等于320VC5416的McBSP的串行时钟移位速率的十六分之一。

计算McBSP端口移位时钟的速率可以采用以下公式:

频率CLKG=时钟频率(发生器输入)/(CLKDV+1)

(1)

CLKDV为寄存器SRGR1的D0到D7位。一般来说,AT89C51采用9 600 b/s波特率时,由式(1)得到:

CLKDV=时钟频率(发生器输入)/频率CLKG-1=时钟频率(发生器输入)/(16×9600)-1

(2)

采样率发生器可选两种时钟之一,一种为DSP输入的外部时钟CLKS,另外一种为CPU的时钟。任何情况下,AT89C51工作的频率比320VC5416的工作频率低很多。后者的工作频率以PLL锁相环对CLKS进行倍频获得,通常在160 MHz以上。通常外部时钟CLKS频率比较低,以20 MHz为例,这个频率依然比AT89C51工作的频率高。若以CPU时钟作为采样率发生器的输入,设定为160 MHz,代入式(2),结果是0x410,可以看出CLKDV是8位,由于结果12位而无法容纳;而如果以CLKS作为其输入,以20 MHz为例,代入式(2),得出结果是0x81,可以被CLKDV容纳。这样一来,在320VC5416与AT89C51高通信速率的情况下,采用CPU时钟作为输入采样率发生器的时钟比较合适。一般说来,通信速率没有很高的要求,为了取得双方的匹配的通信速率,输入采样率发生器的时钟以采用频率低的CLKS比较合适。

初始化TMS320VC5416:

STM #SRGR1,SPSA1

STM #00FEH,SPSD1;FSG帧同步脉冲宽度为1个CLKG,

;波特率为160MHz/(0x00FF)=627450 b/s

STM #SRGR2,SPSA1

STM #3000H,SPSD1;内部采样率发生器时钟由CPU驱动

AT89C51初始化:

MOV TMOD,#20H

MOV TL1,#FFH

MOV TH1,#FFH;C51波特率= (2SMOD/32)* (fosc/12)*(1/(256-initialization))=24509 b/s

MOV SCON,#50H;设置串口方式1,每帧10位数据,允许接收

MOV PCON< #80H;设置SMOD=1

为了避免发送和接收数据频繁地打断CPU的运行,以DMA和McBSP联合使用的方式来操作数据的接收和发送。由RRDY信号驱动McBSP直接向DMAC REVENT事件、接收数据事件;由XRDY信号驱动McBSP直接向DMAC XEVENT事件、发送数据事件。

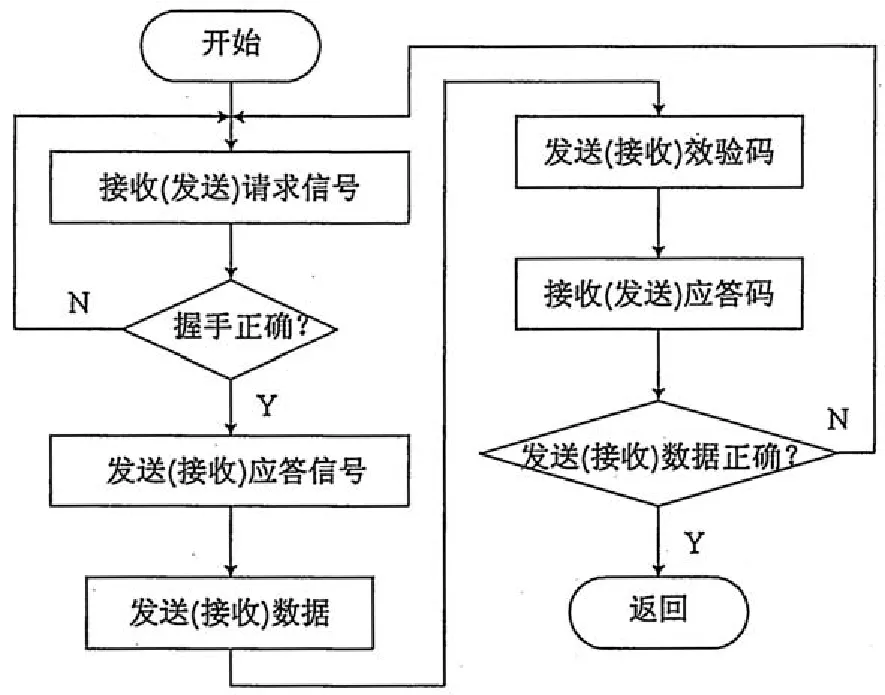

如图4所示为SCI通信协议。

图4 串口SCI通信协议流程

4 结论

本文提出了TMS320VC5416与单片机AT89C51通信设计方法,对320VC5416多通道缓冲串行口McBSP特点进行阐述,在介绍AT89C51的串行通信特点的基础上进行TMS320VC5416与AT89C51串行通信设计,充分考虑了电平匹配问题,通信协议和波特率匹配等方面的问题,最后给出了部分程序实现方法。

参考文献:

[1]TMS320VC5416 Fixed-Point Digital Signal Processor Da⁃ta Manual[Z]. Texas Instruments,2008.

[2]Tai Nguyen. TMS320VC5402A / VC5409A / VC5410A / VC5416 Bootloader. Application Report SPRA602F [Z]. TEXAS INSTRUMENTS,2006.

[3]TMS320C54x DSP Reference Set Volume 5:Enhanced Peripherals[Z]. Texas Instruments,1999.

[4]Atmel 8051 Microcontrollers Hardware Manual[Z]. 2007.

[5]何立民.单片机应用系统设计[M].北京:北京航空航天大学出版社,1990.

[6]胡剑凌,徐盛.数字信号处理系统的应用和设计[M].上海:上海交通大学出版社,2003.

[7]TMS320C54x DSP Reference Set Volume 4:Applica⁃tions Guide[Z]. Texas Instruments,1996.

[8]罗大晖. TMS320VC5416与89C51的串行通信设计[J].常州信息职业技术学院院报,2007,6(3):28-30.

(编辑:向飞)

Communication Design for TMS320VC5416 and MCU AT89C51

LI Sheng-yong

(Xiamen Comfort Science & Technology Group Co.,Ltd,Xiamen361009,China)

Abstract:It is presented in this paper the realization of communication design method for DSP TMS320VC5416 and MCU AT89C51,on the basis of the analysis of characteristics of TMS320VC5416 serial port and 89C51 serial communication design,the communication design is proposed in this paper as well as the level match,communication protocol and baud rate match method,which has guiding significance to realize the communication of DSP and 89c51. The part procedure realization method is presented in the last.

Key words:MCU;DSP;serial communication;program design

作者简介:李胜勇,男,1971年生,山东海阳人,博士,高级工程师。研究领域:数控技术、电子控制系统分析与设计及移动互联网、云服务、智能家电控制技术等。已发表论文50篇。

收稿日期:2015-05-06

DOI:10. 3969 / j. issn. 1009-9492. 2015. 11. 022

中图分类号:TP311.1

文献标识码:A

文章编号:1009-9492 ( 2015 ) 11-0081-04

- 机电工程技术的其它文章

- TinyOS环境下交通信息采集自组网系统设计**国家自然科学基金资助项目(编号:50878088);广东省高等学校学科建设专项项目(编号:2013WYXM0133);广东省高等学校优秀青年教师培养计划资助项目(编号:Yq2013180)。

- 舵机加载系统及其伺服驱动器控制参数设置方法**航空科学基金资助项目(编号:20130863006)

- 基于海马号ROV富钴结壳的钻取技术研究**国家高技术研究发展计划(863计划)资助项目(编号:GZH201100307-04-01)

- 大摆锤驱动头动力学建模与仿真研究**国家质检总局科技计划项目(编号:2014QK255)

- 基于最小二乘法和递推最小二乘法的雷达伺服跟踪系统建模

- 基于ArtCAM的十二生肖浮雕加工研究**江苏省大学生实践创新计划项目(编号:201412808005Y)