PDH标准的E3次群测试序列发生器的FPGA设计

PDH标准的E3次群测试序列发生器的FPGA设计

周鹏

(抚顺职业技术学院 机电工程系,辽宁 抚顺113122)

摘要:为了提高PDH标准下E3次群信号通信设备的可靠性及功能的多样性,设计了一种基于FPGA器件的测试序列发生器系统。在整个设计过程中,完成了测试系统各个功能模块的设计与硬件实现,其中主要包括系统控制模块、PRBS生成模块、误码生成模块和HDB3码转换模块。利用Quartus II软件内嵌的SignalTap II Logic Analyzer对序列发生器进行了实时的测试,结果比较准确,能够完成测试所需的基本工作任务,因此该测试系统的设计具有一定的实用价值。

关键词:PDH;E3;测试序列发生器;FPGA

目前在光纤通信中,虽然PDH(准同步数字系列)体系已被SDH(同步数字体系)体系取代,且SDH体系的优点也逐步突显出来。但与之相比,PDH体系却因其容量适中、配置灵活、成本低廉、功能齐全,并且可以进行“私人订制”等特点,在实际应用中极受客户的欢迎;同时,PDH标准下的E3次群信号的时钟速率为34.368 MHz,正好可以应用在彩色电视视频信号速率级别的分析上[1],所以,为了提高E3信号通信系统的可靠性及功能的多样性,有必要设计一种E3信号的测试序列发生器,来完成对PDH设备性能的测试。FPGA器件由于具有静态可重复编程和动态系统重构的特性,极大地提高了电子通信系统设计的灵活性和通用性[2]。因此,本文提出了采用FPGA来设计PDH通信设备的E3信号测试系统。

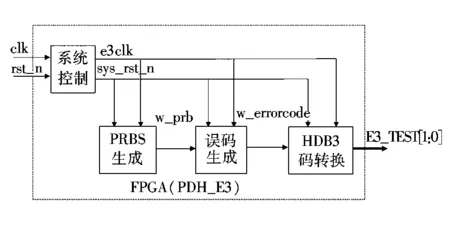

1序列发生器的整体设计

本序列发生器主要由系统控制模块、PRBS生成模块、误码生成模块和HDB3码转换模块构成。其整体结构如图1所示。

图1 测试序列发生器的整体结构简图Fig.1 Overall structure diagram of test sequence generator

其中clk为FPGA的50 MHz系统工作时钟,rst_n为系统复位输入。系统控制模块主要用于实现E3次群时钟信号e3clk及各模块的同步复位信号sys_rst_n;PRBS生成模块用于生成系统测试所需的伪随机序列;w_prbs将二进制伪随机码传递给误码生成模块,以完成测试误码的插入工作;w_errorcode将插入误码后的测试序列传递到HDB3码转换模块,用于形成符合PDH标准的E3信号要求的HDB3编码格式;E3_TEST[1:0]为最终用于进行设备测试的序列信号。

2测试序列发生器的FPGA设计

序列发生器的硬件主要采用FPGA核心板,其中核心芯片使用的是Altera公司目前较新的Cyclone IV系列器件,芯片型号为EP4CE6E22C8N,具有6 272个逻辑资源、276280Bit内置SDRAM,92个用户I/O引脚[3]。核心板上具有FPGA开发的最小系统,包括电源电路、时钟电路、SDRAM存储电路、JTAG下载电路等。软件部分采用Verilog HDL硬件描述语言对各模块进行编写设计,通过Quartus II软件完成代码的编辑输入、编译、综合及硬件电路实现的工作,下面给出各模块的具体设计过程。

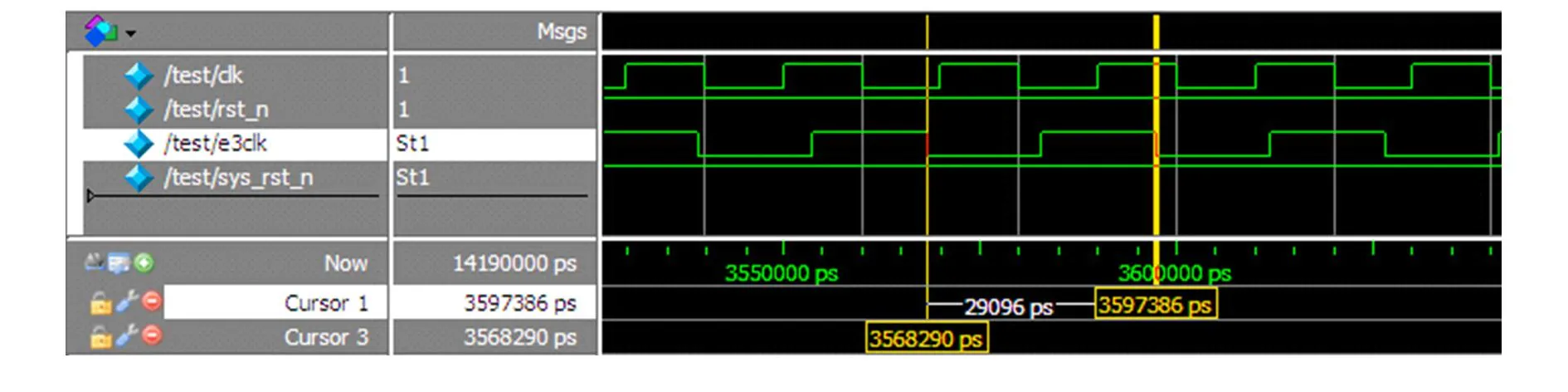

2.1 系统控制模块设计

本模块主要完成E3信号的时钟频率e3clk(34.368 MHz)及各个模块同步复位信号的设计。e3clk的时钟主要通过FPGA内部的PLL对系统的基准时钟50 MHz进行倍频和分频处理来实现。经过多次的测试与仿真,其中倍频系数设为2 148、分频系数设为3 125,即可得到时钟周期为29.096 ns、频率为34.368 MHz的e3clk时钟信号,其modelsim仿真波形如图2所示。

图2 e3clk时钟信号Fig.2 e3clk clock signal

各模块同步复位信号sys_rst_n主要由系统复位信号与FPGA内部的PLL输出锁定信号作相与运算来实现。即锁定信号为高电平时,e3clk输出才有效,这时将锁定信号与系统复位信号相与便得到同步复位信号,目的是为了保证系统的各个模块能够在同一时钟及同一复位信号下同步的工作。

2.2 PRBS生成模块设计

本模块主要完成测试所需的伪随机序列信号(PRBS)的生成。PRBS是通过仪器设备产生的类似于随机信号统计特点的可重复的周期二进制序列,本文主要使用PRBS对PDH标准下E3次群信号的通信设备进行性能测试。

这里使用M序列来实现PRBS的产生。M序列是一种应用比较广泛的伪随机序列,序列中“1”和“0”码出现的概率是相等的,因此常把M序列称为伪随机序列。M序列的生成主要由1个n级线性反馈移位寄存器(如图3)所产生的二进制序列来实现,M表示序列的周期,其长度为2n-1[4]。

图3 M序列n级线性反馈移位寄存器Fig.3 M sequence of n-stage linear feedback shift register

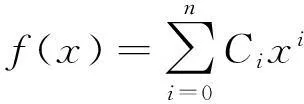

长度不同的M序列由不同的线性反馈移位寄存器构成,可以用本原多项式表示:

(1)

其中Ci为第i级的反馈系数,取值可为0或1。为了便于说明和观察设计过程,这里取n=4,即4级反馈移位寄存器,相应的本原多项式为:

(2)

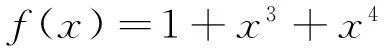

具体实现过程为:在FPGA内部定义1个4位移位寄存器,在每个e3clk的时钟上升沿将1、2位寄存器的输出异或后反馈到第4位寄存中,即可得到1个周期长度为15的伪随机序列,其modelsim仿真波形如图4所示。

从图4中可以看到输出的PRBS_4每隔15个e3clk时钟就重复产生1次,在每个序列周期内,序列的数值0和1是随机出现的。

2.3 误码生成模块设计

本模块主要完成序列误码插入的工作,目的是为了测试PDH设备的误码性能。具体设计过程为:在e3clk的上升沿,对每个输入的PRBS序列码进行计数并将该序列直接输出,当计数值为1 000时,将计数器的进位输出与PRBS当前序列作异或运算,使其作为1个误码出现在PRBS序列中。以此类推,每1000个PRBS序列中就会出现1个误码,其modelsim仿真波形如图5所示。

图4 PRBS波形仿真图Fig.4 PRBS simulation waveform

图5 测试序列的误码插入仿真波形Fig.5 Error code insertion of test sequence simulation waveform

从图5中可以看到当计数器计数到999时(此时已经计数了1 000个PRBS序列),计数进位输出为1,PRBS序列当前值为0,两者异或结果为1,因此看到ERROR_PRBS带有误码的测试序列输出1,实现了误码的插入。

2.4 HDB3码转换模块设计

本模块主要完成测试序列的HDB3码转换,目的是使发生器所输出的序列符合E3次群信号的接口标准。

HDB3的编码规则如下[5]:

(1)当序列中连0数小于4时,HDB3码和AMI码相同;

(2)若出现4个或4个以上的连0时,则将1后的第4个0变为与前一非0符号相同极性的符号,用V表示。

(3)检查相邻V符号间的非0符号的个数是否为偶数,若为偶数,则再将当前的V符号的前一非0符号后的第1个0变为+B或-B,且B的极性与前一非0符号的极性相反,并使后面的非0符号从V开始再交替变化。

图6 HDB3码转换的整体结构图Fig.6 Overall structure diagram of HDB3 code conversion

为了便于HDB3码转换的FPGA实现,首先将带有误码输出的测试序列进行V码变换,再将V码变换为B码,最后是码元极性的变换,实现的整体过程如图6所示。 图6中insert_v为V码变换模块,对输入的序列进行连0检查,当发现连续4或4个以上的连0时,第4个0变为V码(V码用2位二进制数11表示),否则序列直接输出(码元0用“00”表示,1用“01”表示);insert_b为B码变换模块,对输入的V码进行相邻V符号间非0符号个数的检查,若为偶数,则将当前V符号的前一非0符号后的第1个0变为B码(B码用2位二进制数“10”表示)。

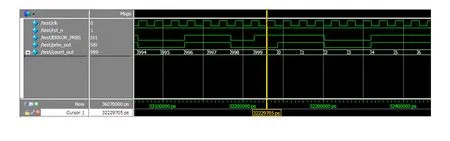

polar为极性变换模块,对插入V码和B码后的序列进行极性的正负交替变换。在模块内部有1个极性标志位even(1表示极性为正,0表示极性为负),初始化时设其值为1。当检测到V码时,若even为1,则模块输出“01”(正电平用“01”表示,负电平用“11”表示),否则输出“11”;当检测到1或B码时,若even为1,则模块输出“11”,进行输出码的正负极性交替,同时对even清0,方便后续代码的极性转变,若even为0,则模块输出“01”, 同时对even设置为1;当检测到0码时,直接输出“00”。具体的仿真波形如图7所示。

图7 HDB3转换模块输出仿真波形图Fig.7 Output simulation waveform of HDB3 code conversion module

现取图7波形的一部分进行分析说明。从左侧第1根黄色时间线开始error_in(误码输出)序列为:000000001111;由于对error_in序列进行了V码和B码的变换,B码内部有1个4位移位寄存器,因此B码输出落后error_in序列5个时钟(即从第2根黄色时间线开始),B输出序列为:00 00 00 11(V码)10 (B码)00 00 11(V码)01 01 01 01;第3根黄色时间线为HDB3码输出(序列极性翻转),其落后B码输出1个时钟,输出序列为:00 00 00 11(-1负电平)01(+1正电平) 00 00 01(+1正电平)11(-1负电平)01(+1正电平)11(-1负电平)01(+1正电平),由此可见本模块的设计符合HDB3编码规则。

3验证测试

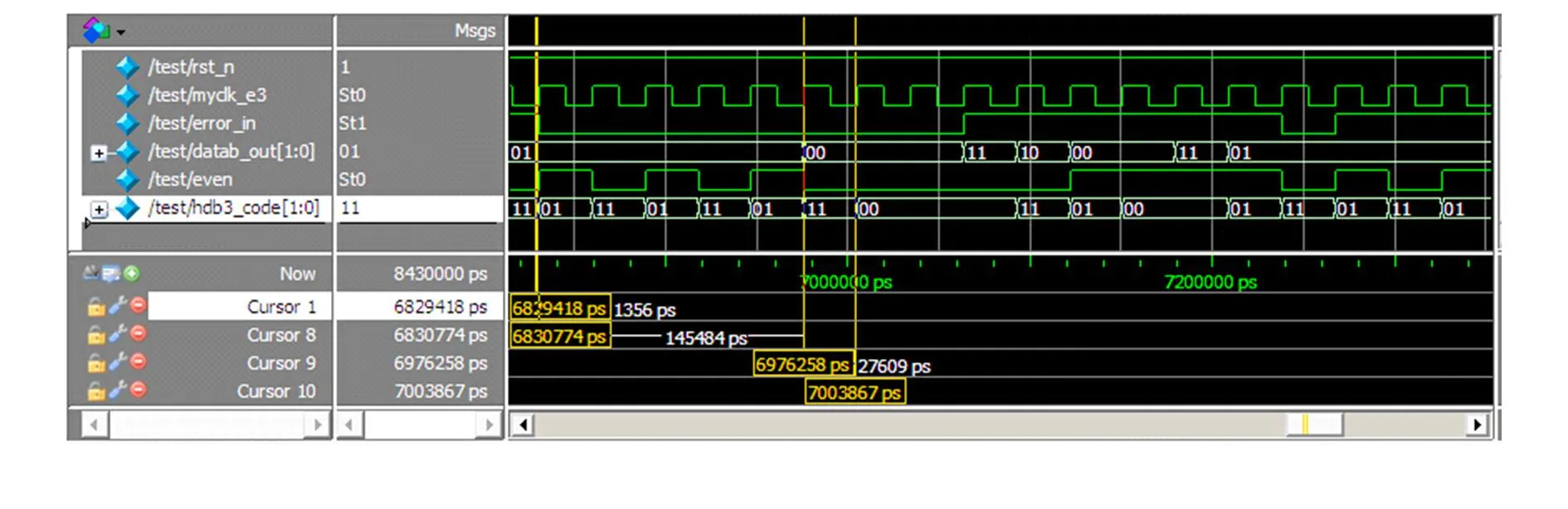

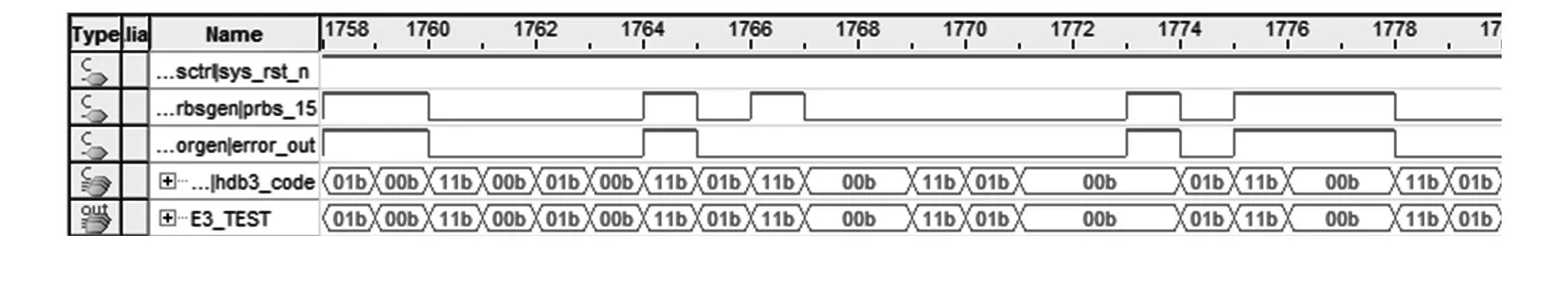

本文使用Quartus II软件内部自带的SignalTap II Logic Analyzer对测试序列发生器进行了实时测试,结果如图8所示。

图8 序列发生器的实时测试波形结果Fig.8 Waveform results of sequence generator in real time test

为了便于对测试波形的观察与分析,这里设置SignalTap II Logic Analyzer的采样时钟为34.368 MHz(即E3信号的时钟频率),取PRBS生成序列的长度为215-1。根据波形图,从第1758个时间点开始分析到1774时间点结束,prbs_15为伪随机序列;error_out为测试误码输出;E3_TEST为发生器的输出序列(与hdb3_code的输出结果相同)。

由于HDB3编码模块本身设计结构的特点,致使发生器输出的序列落后误码输入6个时钟,下面给出输出的对比结果:

PRBS:1100001010000001

ERROR:1100001000000001

HDB3_CODE:11 01 11 00 00 11 01 00 00 00 01 11 00 00 11 01

(两位二进制数表示1位输出序列)

E3_TEST:11 01 11 00 00 11 01 00 00 00 01 11 00 00 11 01

(即-1+1-B00-V +1000+V-B00 -V +1)

从上述结果分析可知本发生器的设计十分正确,完全可以满足实际设计的需求。

4结论

本文采用FPGA器件实现了PDH标准下E3次群信号通信设备序列测试系统的设计。在单一的FPGA芯片上,采用Verilog HDL硬件描述语言,完成了系统控制模块、PRBS生成模块、误码生成模块和HDB3码转换模块的设计,经过Quartus II软件的综合与布线,最终实现了测试序列发生器的设计。同时对各设计模块及序列发生器进行了仿真和实时的硬件测试,结果表明,该序列发生器工作稳定、可靠,可以根据不同的需求进行灵活的修改,能够满足实际的测试要求,具有较好的应用价值。

参考文献:

[1] 胡辽林,刘雪峰.SDH中E3复用/解复用系统的FPGA实现[J].光通信技术,2013(2):44-46.

[2] 孙玥,吴彬.基于FPGA的E1信号校验电路的设计[J].中国新通信,2014(8):97-98.

[3] 杨少东,覃琴.基于FPGA的图像采集处理平台的设计[J].电子世界,2014(4):118-119.

[4] 刘亚娟.基于Simulink的m序列仿真分析[J].长江大学学报:自然科学版,2014,11(22):52-54.

[5] 李春晖.基于SystemView的HDB3编码器设计[J].信息通信,2014(9):41.

(责任编辑:张英健)

Test Sequence Generator of E3 Group with

PDH Standard Designed by FPGA

ZHOU Peng

(The Department of Electrical Engineering, Fushun Vocational Technology Institute, Fushun Liaoning113122, China)

Abstract:In order to improve the reliability and the diversity of function of E3 group signal communication equipment with PDH standard, we designed a test sequence generator system based on FPGA device. In the whole process of design, we completed the implementation of hardware and the design of each function module of test system, which mainly included the system control module, PRBS generation module, error code generation module and HDB3 code conversion module. Using SignalTap II Logic Analyzer module embedded in Quartus II software for real-time testing of the sequence generator, the result is more accurate. The sequence generator can complete the basic tasks required to test, so it has certain practical value to design the test system.

Keywords:PDH; E3; Test sequence generator; FPGA

作者简介:周鹏(1983-),男,山东兖州人,讲师,硕士,主要研究方向为数字信号处理及应用、嵌入式系统设计。

收稿日期:2014-11-19

中图分类号:TN914.3

文献标识码:A

文章编号:1671-5322(2015)01-0056-05

doi:10.16018/j.cnki.cn32-1650/n.201501013