基于FPGA的延时精确校准在等效采样中的应用

刘文彬,朱名日*,郑丹平,姚 鑫,潘 凯

(1.桂林电子科技大学电子工程与自动化学院,广西桂林541004; 2.桂林电子科技大学计算机科学与工程学院,广西桂林541004)

基于FPGA的延时精确校准在等效采样中的应用

刘文彬1,朱名日1*,郑丹平2,姚鑫1,潘凯1

(1.桂林电子科技大学电子工程与自动化学院,广西桂林541004; 2.桂林电子科技大学计算机科学与工程学院,广西桂林541004)

摘要:对一些高频信号如超宽带雷达回波信号,由于其带宽通常在几百兆以上很难对其进行实时采样,通常利用FPGA配合可编程延时芯片对回波信号进行等效采样。由于延时芯片延时值存在温度漂移和各个延时芯片之间的延时值存在差异的问题。设计了一种基于FPGA的延时精确校准方案,使延时芯片的延时值随温度漂移最小化。实验结果表明该延时精确校准方案可行,在高频信号的采集中有很好的参考价值。

关键词:FPGA;等效采样;延时精确校准;温度漂移

近年来,随着数字化技术的发展,对高频信号的采集越来越多,但由于受现有元器件的性能和成本的限制,普通的A/D转换器很难对高频信号实行实时采集,而取而代之的是等效采样技术,可以实现周期信号或者重复信号的数字化,它利用信号的周期性,以增加采集时间为代价,降低对高速采样电路的压力,通过重组恢复原始信号。由于是将不同周期的采样点重新组成一个完整的周期信号,任何定时抖动或触发点的变化都将导致采样点的相位误差,相位误差的存在使得在重组信号时导致重建波形失真,这样就降低了恢复波形的精度[1]。所以等效采样技术中需要设计精密延时电路,才能保证采集高精度的高频信号,因此,精密延时电路的设计是高速数据采集系统中的关键技术之一。

1 等效时间采样原理

对于脉冲超宽带雷达发射脉冲为高频窄脉冲信号,其中心频率一般在几百兆以上。受限于模数转换的带宽和成本,通常采用等效采样方式接收模拟回波信号,即在每个重复周期内进行适量次数的采样,然后综合所有采样合成完整的输入信号,从而将高频信号变化为波形相似的低频信号。取样变换后新组成的重建信号是被采样信号在频域上被压缩的低频信号,该信号完全保留了原始信号包含的所有信息。由此可见,延时式等效采样时序控制的关键在于同步时钟信号的精准相对延时控制[2-3]。

对一个完整雷达反射波的数据采集需要进行多次采样,每采一个样,其延时时间要改变一次,这样才能在多次采样过程中,等效获得一个雷达反射波不同时刻的样点幅值[4-5],这也是等效采样技术的关键所在。因此,要求该延迟时间具有精度高的特点[6-7]。但是针对现有的延时芯片存在延时时间不够精确,具体表现为延时时间有温度漂移现象和各个延时芯片之间的延时有差异,导致采样点的相位误差,相位误差的存在使得在重组信号时导致重建波形失真,针对这个问题我们设计了对延时芯片延时值进行延时精确校准。

2 系统的结构与工作原理

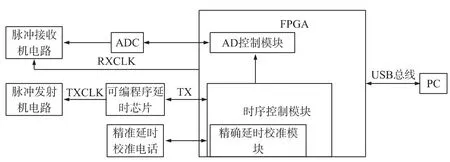

系统结构框图如图1所示。由时序控制模块提供2路重复频率相同的同步时钟信号,其中一路信号作为接收机触发脉冲,另一路时钟信号通过可编程延时在每个取样脉冲递增一个固定的延时量作为发射机的同步触发脉冲。

图1 超宽带雷达数据采集系统结构框图

工作原理:时序控制模块接收到上位机通过USB总线[8-9]下发的指令后开始发出固定重频周期的两路参考时钟信号。其中TX相对RXCLK固定提前几个时钟,RXCLK作为接收机触发脉冲,TX经过可编程延时芯片时再延时一段时间保证RXCLK相对TXCLK有一个固定的延时量,TXCLK作为发射机的同步触发脉冲。本设计中是固定RXCLK,靠时序控制模块控制延时控制字的设置和参考时钟信号TX来产生的TXCLK依次提前RXCLK一个固定的延时量来达到顺序等效采样。对一个完整雷达反射波的数据采集需要进行多次采样,每采一个样,其延时时间要改变一次,延时时间的改变是根据延时控制字的大小来控制延时芯片来实现延时值的大小。选用的可编程延时芯片的位宽为10,延时单元为10 ps。首先对延时控制字进行初始化存在一个位宽为10深度为25的存储器中,存储器中不同的控制字对应着不同的延时时间。在进行延时校准时采用的是对存储器中的延时控制字的动态调整。经过延时精确校准后的延时控制字再用于下一周期的回波信号的采集。在参考时钟信号RXCLK之后AD开始启动采集窄脉冲回波信号,最后通过USB总线将采集到的数字化回波信号上传到上位机系统。

3 延时精确校准

在利用FPGA和可编程延时芯片实现等效采样时延时芯片延时数值存在温度漂移以及芯片间的特性误差,导致系统延时误差存在长时积累。FPGA的粗延时量与延时芯片的细延时量不一致,导致延时调整时,在粗延时刻度的调整存在较大误差。上述两个问题归结为FPGA设置的延时值Tset与相对FPGA时钟刻度的实际延时值Ttrue存在误差。导致上述误差的主要原因有:延时芯片延时量的温度偏移,延时芯片存在温度漂移以及延时芯片的芯片间的延时量存在差异。

综上所述,延迟误差可由延时芯片的温度偏移引起,以及器件特性之间的差异导致。针对上述分析,要消除上述延时误差必须精确测量出:延时芯片的延迟量相对FPGA的实际延时值Ttrue。得到Ttrue即可得到其与FPGA设置的延时值Tset之间的精确误差,并通过延迟精确校准校正,相对误差最小化,从而解决上述问题。

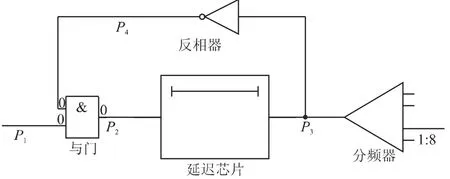

图2 延迟精确校准框图

3.1延时精确校准电路的设计

延迟精确校准框图如图2,P1为FPGA输出的测试脉冲; P2为与门输出脉冲; P3为延迟芯片延迟后脉冲; P4为P3反向后的脉冲信号。校准状态时: FPGA输出固定宽度的高电平脉冲P1,设t1为与门延迟量,P1与P4相与,延迟t1后变为P2。设Tture为延时芯片的实际延迟量,P2经过延迟芯片延迟Ttrue,后变为P3。P3经过反向器延迟t2,t2为反相器延迟量,反向后变为P4。P4反馈与门再次与输入P1相与后变为P2,此时P2状态从1反转为0。P2延迟Ttrue后,取反又与P1相与,此时P2状态从0反转为1。重复上述反馈流程,P2的状态在P1为高电平时一直保持1-0-1的反转,反转间隔时间为: Ttrue+t1+t2。由于P3指示P2的时间延迟,同样P3的也会保持间隔为Ttrue+t1+t2的高低电平反转。

由上所述,P3在P1为高电平状态时,其为间隔为Ttrue+t1+t2的0-1期翻转。故在该状态下,P3可视为周期为2·(Ttrue+t1+t2)的时钟信号。如果能够精确测量出该时钟信号的周期即可精确得到此时延时芯片相对于主处理时钟即FPGA的时钟的实际延时量Tture。此时问题简化为:输入信号为P3的高速频率计的实现。高速频率计的实现可看做:固定间隔T内高速计数器C的实现。若时间T已知,只要知道C,测被测信号周期为T/C。

如图2,把P3作为1: 2,1: 4,1: 8分频器的输入时钟,则1: 8分频器在P1为高状态时的输出翻转周期为16·(Ttrue+t1+t2)。由于延迟芯片的初始延迟值最小为1.8 ns,故1: 8分频器输出翻转周期为最小值为28.8 ns,即最高频率为34.72 MHz。1: 8分频输出到FPGA即几乎可无限扩展该分频器的位宽。结合该分频器以及FPGA内部的计数器,即可实现一个输入时钟为被测信号P3的高速高位宽计数器。校准状态时,P1脉冲宽度T已知,在P1为高电平状态时的翻转次数C可通过上述计数器得到,则P3的周期为T/C。至此得到P3相对与主处理时钟的实际精确延时值。

3.2延时精确校准的实现

FPGA时钟频率使用的是200 MHz的时钟,其周期为5 ns。本设计中每个步进延时间隔为200 ps,等效为5 Gsample/s的采样速率。一个时钟周期内延时调准点数TapIndex为25点。相应的延时控制字设为DlyTap_i,一个时钟周期内选取对应理想延时值为DlyPs_i,程序中设置的P1设置的高电平时间ajtime为固定的时钟周期。可以计算出一个时钟周期内选取对应理想的计数值DlyCnt_i。关键代码如下:

TapIndex=0: 24;

DlyTap_i=200+20·TapIndex;

DlyPs_i=6000+200·TapIndex;

DlyCnt_i=floor(ajtime/2./DlyPs_i) ;

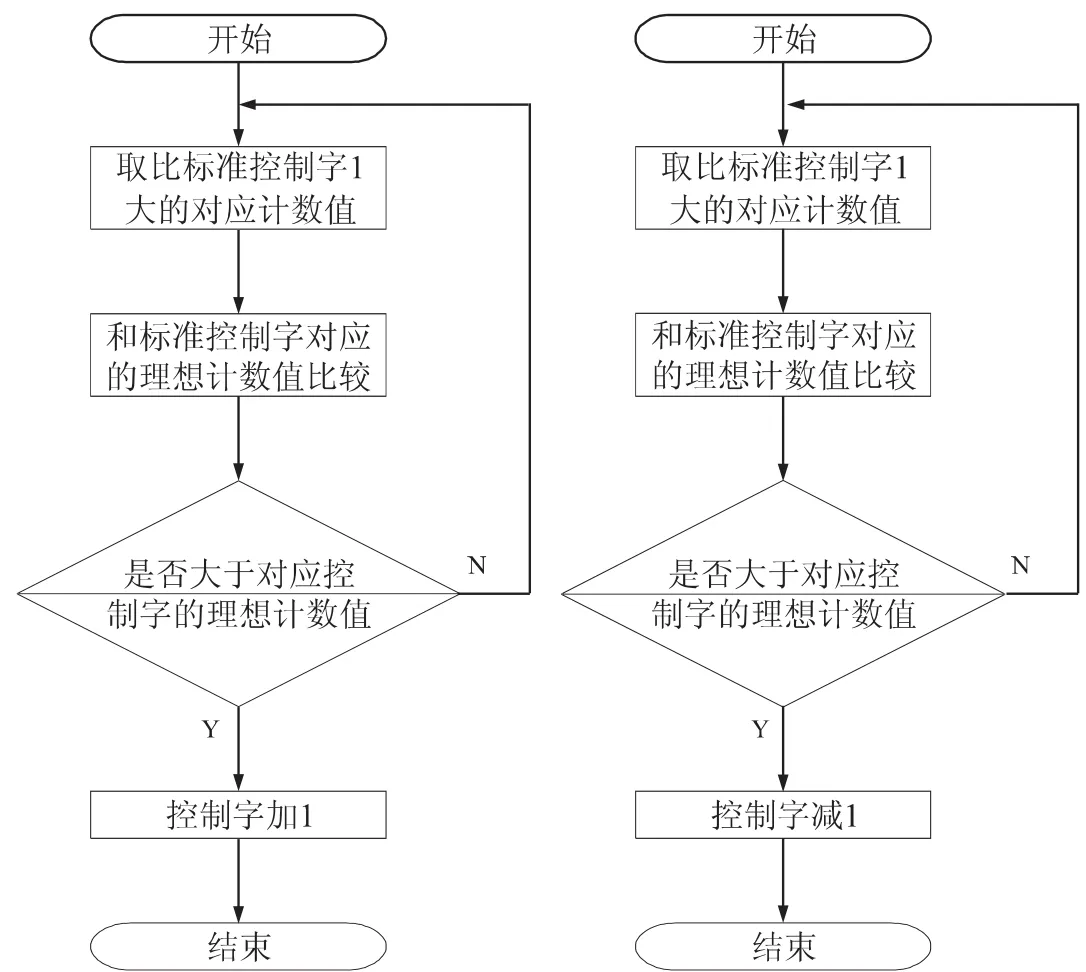

图3 延时精确校准流程图

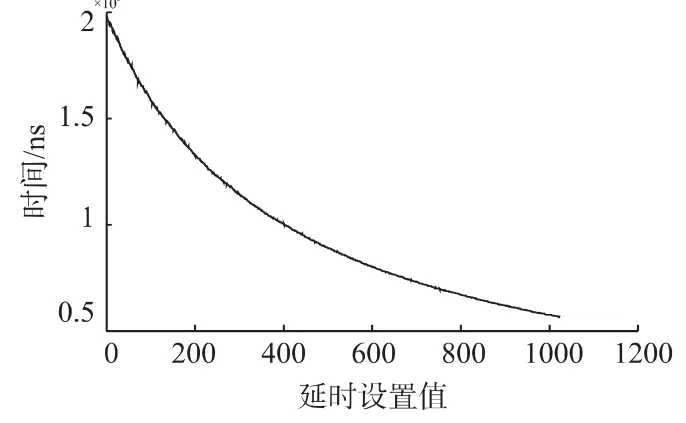

延时精确校准具体流程见图3所示。在每个延时控制字的上下各设置一个延时控制字,一个时钟周期内延时精确校准点数为50个点。经过延迟精确校准电路出来的时钟信号P3再经过分频器进入FPGA内的计数单元,计数单元的采用的是200 MHz时钟,对时钟信号P3的上升沿进行计数。每个控制字对应的理想计数值和计数单元在P1为高电平期间的计数值进行比较,再对相应的延时控制字进行加一或减一动态调整。在延时校准状态时,首先延时精确校准模块设置一个延时控制字,该延时控制字比相应的的标准延时控制字大1,写入延时芯片进行延时校准。对于延时芯片而言延时控制字越大延时时间越大,则从延时校准电路出来的时钟信号P3的周期就越大,那么在P1为固定的高电平期间计数单元的计数值就相对较小,即延时设置值和计数值在P1固定高电平期间是成反比的,如图4所示。由于温度的影响,该计数值可能比标准的控制字对应的计数值大,说明延时时间偏小,则对控制字进行动态加一调整。

图4 延时设置值与计数值关系图

3.3精确延时控制状态机的设计

状态机开始处于无效状态,当检测到延时校准的触发信号rAdjSta时开始进入设置延时控制字状态DLYADJ_DAT,在该状态时设置的延时控制字比标准的延时控制字小1,理想情况下该控制字写入延时精确校准模块后出来的计数值应该比标准的的计数值大。若小于标准的计数值则需要动态调整延时控制字。下一状态进入延时状态DLYADJ_LEN,即从设置好延时控制字到计数单元开始统计时钟信号P3的上升沿之间的延时时间;当延时时间结束有一个标志信号,当wDlyDatEnDone置1时开始进入计数状态DLYADJ_CNT,此状态完成对时钟信号P3上升沿的计数,在此状态设置P1高电平的时间;当P1高电平时间到有一个标志信号wDlyDatCntDone,当此信号为1时开始进入读计数值状态DLYADJ_ RED,此状态统计的计数值存进一个寄存器中;下一状态进入比较状态DLYADJ_ADJ,在此状态比较设置的控制字对应的计数值和标准的计数值的大小,并相应的动态调整控制字并存储在一个位宽为10深度为25存储器中;下一状态进入比较结束状态DLYADJ_DONE,此状态是对完成校准点数的统计,当完成的校准点数为50时结束整个延时精确校准,否则进入设置延时控制字状态继续延时精确校准。

图5 精确延时控制状态转换图

4 实验结果

4.1测试延时芯片的温度漂移

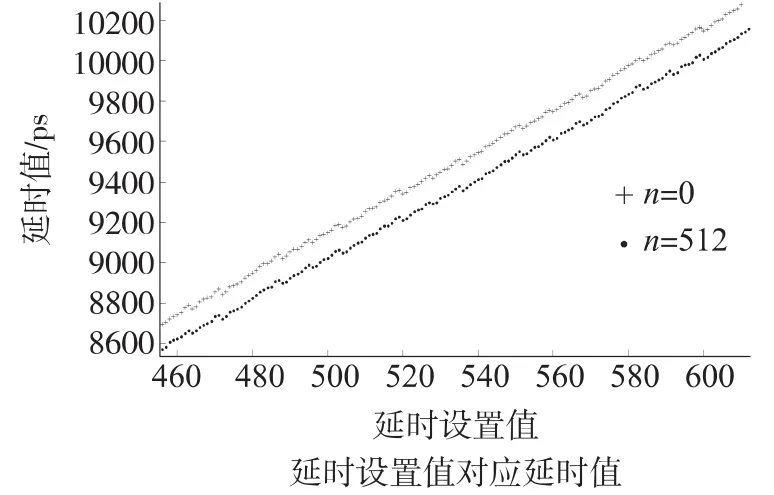

选用的可编程延时芯片数字输入位宽是10位,也即是最大的延时控制字可设置为1 023。延时控制字由0依次增加到1 023,经过延时精确校准模块可以得到相应的计数值,把这些数值通过USB总线上传到上位机保存下来,由于P1的高电平时间是已知的可以在MATLAB中画出不同延时控制字对应的延时时间,图6是在两个不同时间画出的不同延时控制字对应的延时时间,由图6可知可编程延时芯片延时值确实存在温度漂移,最大温飘达400 ps。

图6 可编程延时芯片延时值温度漂移示意图

4.2采用延时精确校准测试

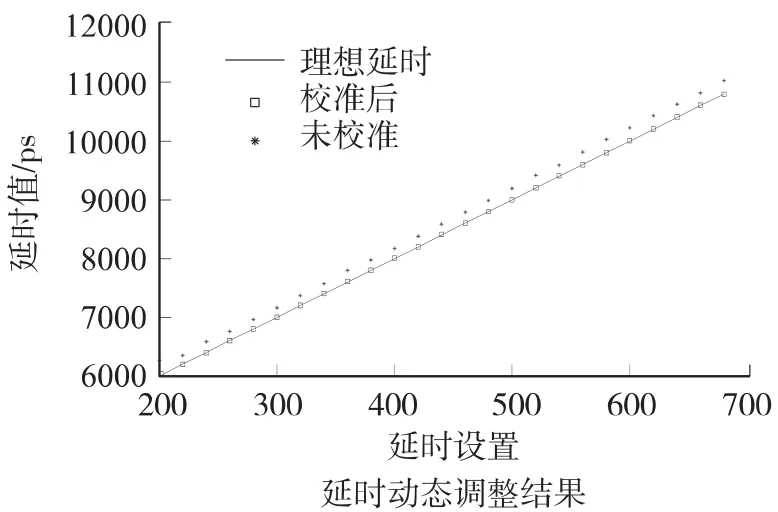

由于延时芯片存在上述温飘和器件间的不一致性,现考虑采用延时刻度动态调整。图7中黑色线条表示的是可编程延时芯片理想情况下不同延时控制字对应的延时值;星号表示没有经过延时精确校准时实际采集的数据不同延时控制字对应的延时值;方格表示经过延时精确校准时实际采集的数据不同延时控制字对应的延时值。从图中很容易的看出未经过延时精确校准的延时值平偏离了理想延时值,而经过延时精确校准的延时值是和理想延时值吻合的。所以设计的延时精确校准方案达到了预期的效果,使可编程延时芯片的延时值的温度漂移尽量的最小化。

图7 延时动态调整效果示意图

5 结束语

对高频信号的采集方案多采用等效采样技术来实现,本文介绍了等效采样的原理以及现有的延时芯片延时量存在温度漂移的显现,设计了一种基于FPGA的延时精确校准的方案,很好的解决了在利用FPGA和延时芯片实现等效采样时遇到的延时芯片延时量存在温度漂移的问题,实现了对窄脉冲等效转换速率为5 Gsample/s的采样。

参考文献:

[1]宋庆环,宋凤娟,朱全印.高速数据采集系统中精密延时电路的研究[J].机床与液压,2008,36(8) : 204-206.

[2]戴舜,方广有.脉冲探地雷达小型化控制与采集系统的设计[J].现代雷达,2011,33(2) : 5-8.

[3]沈绍祥,刘丽华,方广有,等.时域反射仪高精度步进延迟系统的设计[J].深证大学学报:理工版,2013,30(3) : 242-247.

[4]刘丽华,猛升卫,陈浩,等.测雷达接收机的设计[J].仪器仪表学报,2009,30(6) : 179-182.

[5]黄守麟.超宽带穿墙探测雷达信号采集和处理系统设计与实现[D].桂林:桂林电子科技大学,2009.

[6]常高嘉,冯全源.基于FPGA的高速数据采集系统的设计与实现[J].电子器件,2012,35(5) : 615-618.

[7]曾浩,王厚军.一种时延调整技术实现等效采样的方法研究[J].仪器仪表学报,2008,29(4) : 346-349.

[8]张杰,曹思樟,祝怀标,等.基于游标法的等效时间采样模块的设计[J].计量与测试技术,2012,39(4) : 59-63.

[9]EZ-USB FX2 Technical Reference[EB/OL].Manual.www.cypress.com.

刘文彬(1989-),男,安徽阜阳人,硕士研究生,主要研究方向为智能信息处理与嵌入式应用,568923465@ qq.com;

朱名日(1955-),男,广西桂林人,教授,硕士生导师,主要研究方向为智能传感器网络,嵌入式系统,541322259 @ qq.com。

Research of Static Synchronous Compensator Based on Modular Multilevel Converter

HUANG Rui*

(Chongqing College of Electronic Engineering,Chongqing 401331,China)

Abstract:As the broad application of multilevel inverters in high-power area,modular multilevel converter(MMC) is proposed in this paper to be used as a static synchronous compensator(STATCOM).This MMC-STATCOM has a high degree of modularity and good reliability,and is convenient for maintenance and capacity extension,which is a typological structure with high development potential.Firstly,this paper explains the operation principle and mathematical model of MMC-STATCOM.Then,a novel reactive power decoupling control strategy and a novel capacitor voltage-balancing control scheme are proposed respectively.The simulation and experiment result show that performance of proposed control strategy and MMC-STATCOM may be a new circuit topology with significant engineering application value in large-capacity reactive power compensation field.

Key words:modular multilevel converter; static synchronous compensator; power decoupling control; voltage-balancing control

中图分类号:TP247.2`

文献标识码:A

文章编号:1005-9490(2015) 03-0706-05

收稿日期:2014-07-27修改日期: 2014-08-25

doi:EEACC: 8110B10.3969/j.issn.1005-9490.2015.03.047