8位高速低功耗流水线型ADC的设计技术研究*

居水荣,刘敏杰,朱樟明

(1.江苏信息职业技术学院,江苏无锡214153; 2.西安电子科技大学,西安710071)

8位高速低功耗流水线型ADC的设计技术研究*

居水荣1*,刘敏杰2,朱樟明2

(1.江苏信息职业技术学院,江苏无锡214153; 2.西安电子科技大学,西安710071)

摘要:采用7级子ADC流水线结构设计了一个8位80 Msample/s的低功耗模数转换电路。为减小整个ADC的芯片面积和功耗,改善其谐波失真和噪声特性,重点考虑了第1级子ADC中MDAC的设计,将整个ADC的采样保持电路集成在第1级子ADC的MDAC中,并且采用逐级缩放技术设计7级子ADC的电路结构,在版图设计中考虑每一级子ADC中的电容及放大器的对称性。采用0.18 μm CMOS工艺,该ADC的信噪比(SNR)为49.5 dB,有效位数(ENOB)为7.98位,该ADC的芯片面积只有0.56 mm2,典型的功耗电流仅为22 mA。整个ADC性能达到设计要求。

关键词:集成电路ADC;设计技术;芯片面积;低功耗;信噪比

流水线型模数转换电路(Pipelined ADC)是模数转换电路大类中性能比较优越的一种,这种ADC既能像全并行结构ADC那样实现很高的转换速度,又能像子区结构ADC那样以较少的电路元件实现较高的分辨率和较低的功耗。尽管流水线型ADC具有以上优点,但如何进一步降低整个ADC的功耗、提高这种结构ADC的信噪比以及降低ADC的芯片面积等仍是目前业内同行研究的主要方向[1-2,5-6]。

本文介绍的一个基于0.18 μm工艺,采样速率为80 MHz的8位流水线型ADC旨在解决这些问题。通过对第1级子ADC中MDAC及其运放的优化设计,可以节省整个ADC的采样保持电路模块;另外在第2级~第7级子ADC的电路结构设计中采用了逐级缩放技术,并且采用优化的版图设计技术,这些创新性设计技术减小了整个ADC的芯片面积,降低了该ADC的功耗,提高了该ADC的信噪比,使得该ADC可以广泛应用于无线通讯、仪器仪表、超声系统、高分辨率图像处理和高清晰度电视(HDTV)等场合。

1 8位高速低功耗流水线型ADC整体设计思想

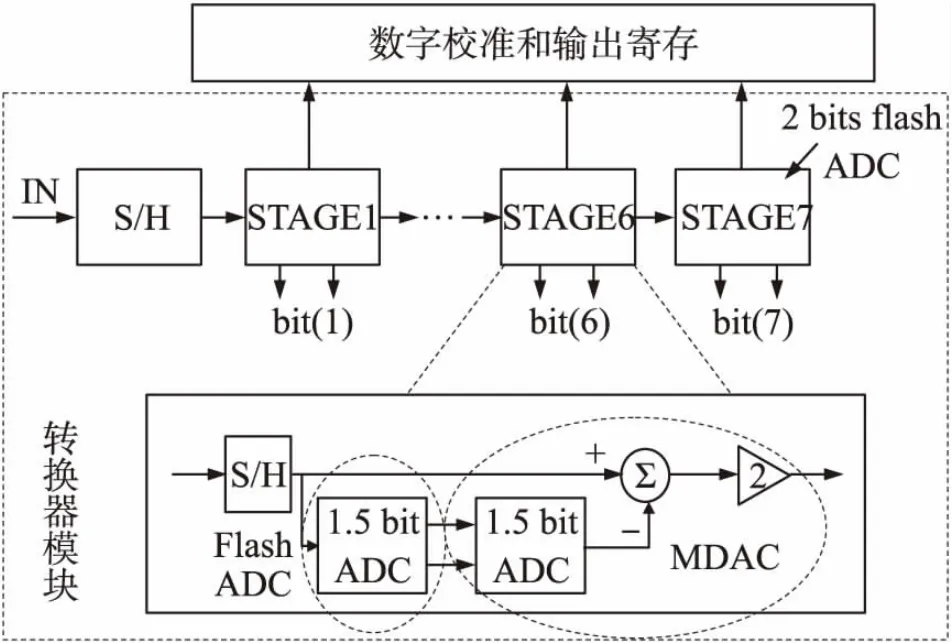

图1是一种8位高速低功耗流水线型ADC的结构框图,其中用虚线框起来的是整个ADC的核心模块——转换器模块,该模块主要由一个采样保持电路S/H和7级子ADC构成; 7级子ADC的输出最终经过数字校准和输出寄存模块,形成整个ADC的输出。

图1 流水线型ADC结构框图

图1中转换器模块的核心单元是7级子ADC,其中第1级至第6级的结构基本相似:每1级子ADC由采样保持电路S/H、1.5 bit精度的快闪ADC (Flash ADC)和相乘DAC(Multiplying DAC)组成,是整个流水线转换器的最为关键的环节,其性能决定了整个流水线型ADC的性能,而第7级子ADC是一个2 bit的快闪ADC。每一级子ADC的工作过程都是类似的:首先是对输入信号进行采样和保持,保持的信号被1.5 bit快闪ADC转换成数字信号;然后通过相乘DAC(MDAC)将其转换成模拟信号,这个模拟信号与保持信号相减求余量,余量被一个运算增益放大器放大之后送到下一级。

为了实现高速、低功耗、高信噪比等优越的性能,并且减小整个ADC的芯片面积,在以上流水线型ADC设计中有一些关键技术需要解决。首先,第1级子ADC的设计非常重要,决定了整个ADC的性能,因此如何设计出一个功耗低、速度高、信噪比符合要求并且芯片面积最小的第1级子ADC是流水线型ADC中的关键技术,尤其是其中MDAC中的运算增益放大器的设计;其次,第1级子ADC完成设计后,第2级到第6级可以采用与第1级子ADC完全相同的结构,但是从整个ADC的功耗、信噪比指标以及芯片面积等方面考虑,可以对这后面几级ADC进行优化设计,比如可以采用逐级缩放技术,即在满足整体ADC性能的前提下,后几级子ADC都较第1级子ADC的开关管尺寸、电容以及放大器的性能等有所降低,这样可以明显减小整个ADC的芯片面积,改善ADC的信噪比等性能指标。本文重点对以上两点关键技术进行相关研究。

2 第1级MDAC中放大器的设计

目前常见的流水线型ADC中都用到一个采样保持电路,如图1中的S/H模块,这个采样保持电路主要由采样网络和一个采样保持运算放大器SHA(Sample-and-Hold Amplifier)组成。SHA用来为第1级子ADC提供一个输入信号的保持信号。由于采样保持运放作为一个前端信号处理模块是在没有任何预放大的基础上处理一个大摆幅的输入信号的,因此噪声特性差,并且谐波失真也大,从而会显著降低整个ADC的谐波失真和噪声特性;另外这个采样保持电路还会引起较大的功耗。为了克服以上缺点,本文所研究的流水线型ADC采用了无采样保持运算放大器结构(SHA-less),在这种结构中,将采样保持电路集成到第1级子ADC的MDAC中,而没有专门的采样保持运放,这种结构能够节省功耗,提高谐波失真和噪声特性,这是本文ADC设计中的独特之处。但采用SHA-less结构容易造成MDAC与子ADC处理数据的不一致,必须对MDAC中运算放大器的性能指标进行精确的设计,以便匹配输入信号到MDAC以及与子ADC两条通路的采样网络。接下去就详细介绍MDAC中放大器性能指标的确定。

MDAC电路的误差可以分为静态误差和动态误差,静态误差与其中运放的直流增益相关,动态误差与运放的单位增益带宽及转换速率相关。

运放有限的增益和带宽会给MDAC的输出建立带来误差,其中有限的增益对精度带来误差,有限的带宽对速度带来误差,总体来讲,要达到一定的精度和速度,就是要求MDAC在某个特定的时间内达到某个特定的精度范围。根据经验,需要在半个时钟周期内使MDAC达到所要求精度对应的1/2 LSB (Least Significant Bit)。下面具体计算第1级子ADC中MDAC的运放增益和单位增益带宽。

2.1增益的计算

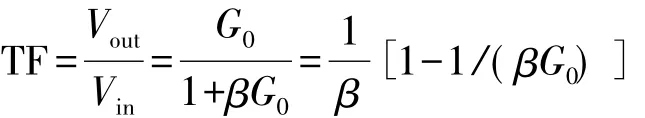

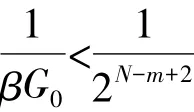

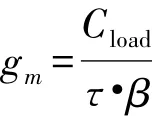

定义运放的反馈系数β,该反馈环路的传输函数TF为:

式中:G0为运放开环直流增益,那么由运放的有限增益带来的误差可以表示为:1/(βG0)。对于一个N位的ADC,假设要设计的MDAC的有效位数为m,则MDAC的输出应该具有N-m的精度,其误差需要满足:

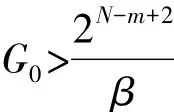

则运算放大器的增益必须满足:

对于第1级子ADC,N = 8,每一级MDAC的m 为1,β= 0.5,由此可以算出增益G0>60 dB,这个数值就是本文第1级子ADC中MDAC运算放大器的增益设计指标。

2.2单位增益带宽的计算

除了增益误差,MDAC的另外一个误差来源是运放的有限增益带宽积。

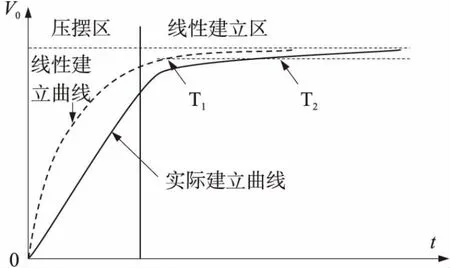

在保持阶段,MDAC电路可以当作一个对阶跃信号响应的闭环放大器。由于实际运算放大器的带宽并非无限大,因此对于MDAC而言,其输出电压达到确定的精度范围是需要一定的时间的。图2是采样保持电路中运放信号建立过程的示意图。

图2 信号建立过程示意图

由于MDAC的信号建立过程不存在较长时间的转换现象,可以用线性建立模型来模拟输出信号的建立过程,并且将MDAC近似为单极点系统,假设其时间常数为τ,则输出电压随时间的关系为:

式中:V∞为时间趋于无限长即运放稳定时的输出电压,所以由系统的有限带宽带来的建立误差为:

为了在保持阶段结束的时候满足精度的要求,那么闭环运放的建立误差必须满足:

式中:τ是闭环运放的时间常数,N为ADC的位数,m为MDAC的有效位数,t是保持阶段的时间,整理以上表达式得到:

对于本文的采样频率为80 MHz的8 bit ADC,如果设计第1级MDAC电路的保持相时间为6.25 ns,但是因为采用了SHA-less结构,则用于建立的时间可缩减为5.25 ns,代入以上表达式得到τ<0.825 ns。

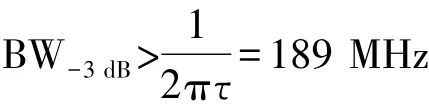

得到以上时间常数后,对于第1级MDAC电路,可计算得到其-3 dB带宽BW-3 dB为:

以上就是本文所研究ADC的第1级子ADC中MDAC运算放大器的单位增益带宽指标。

2.3运放结构

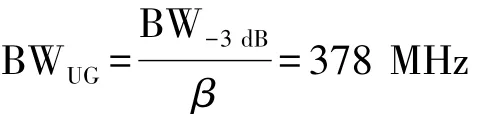

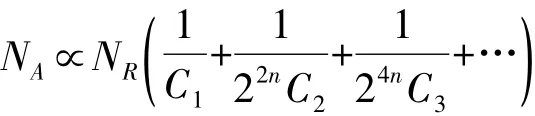

根据以上计算指标,MDAC中的放大器要采用两级运放结构,如图3所示。

从而得到MDAC中运放的单位增益带宽BWUG为:

图3 MDAC运算放大器结构

图3中第1级为折叠式共源共栅,提供大增益,第2级提供大的摆幅。图3中每一个管子的尺寸分别为:T1/T2为30 μm/0.18 μm; T3为72 μm/0.35 μm; T4/T5为87.6 μm/0.35 μm; T6/T7为60 μm/0.35 μm; T8/T9为58 μm/0.35 μm; T10/T11为36 μm/0.35 μm; T12/T13为85.8 μm/0.35 μm; T14/T15为98 μm/0.2 μm; T16/T17为72 μm/0.35 μm。

通过对第1级子ADC进行信号处理能力的仿真,输入一个频率为11.25 MHz差分正弦信号,通过理想DAC恢复,检测恢复的信号精度,然后进行快速傅里叶变换,得到第1级ADC的频谱图,可以计算出第1级ADC的信噪比(SNR)为74.2 dB;再将以上数据导出,采用MATLAB工具进行处理,可以得到第1级ADC的有效位数(ENOB)为11.2位。

3 后级ADC设计中的逐级缩放技术

图1所示的转换器模块中,第2级~第6级子ADC的结构可以采用跟第1级子ADC完全相同的结构,但在本文8 bit ADC的设计中,为了减小流水线型ADC的整体功耗和面积,优化信噪比等性能指标,后级ADC的结构设计过程中采用了一种逐级缩放的技术,在满足整体ADC性能的情况下,后几级ADC较第1级的开关管尺寸、电容和放大器的性能等都有所降低,将这种技术应用到本文ADC中是一个独特之处。当然这种设计技术对工艺的依赖程度很高,主要表现在电容的失配,另外设计过程中必须精确计算缩放系数。因此接下去首先分析MDAC中运放的功耗与负载电容以及运放的反馈系数等的关系,通过这种关系计算得到与第1级子ADC相比,第2级~第6级子ADC的缩放比例;然后由这种缩放比例设计采样电容,并确定第2级子ADC的MDAC中的运放结构,以及第2级子ADC的整体仿真。

3.1MDAC功耗及影响MDAC功耗的参数

ADC中量化器的功耗主要由MDAC电路的功耗和比较器电路的功耗组成。在通常使用的1.5 bit量化器中由于有校准算法,比较器的误差范围可以比较大,因此可以采用功耗较低的动态比较器,量化器的主要功耗来源于MDAC电路。图4所示是一个B1位的MDAC后面接一个B2位的量化器。

图4 MDAC及量化器结构

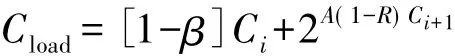

前一级MDAC的负载可用下式表示:

式中:Ci为本级量化器的反馈电容,即单位采样电容。以上表达式中的第1项(1-β)Ci表示反馈电容网络的等效负载,其中β为反馈系数;第2项2B2Ci+1表示后一级MDAC的输入电容;第3项Cp表示运放输出端的寄生电容:第4项CCMFB表示运放共模反馈带来的负载电容;第5项nCin表示后一级量化器中比较器的输入电容,n为比较器的个数,与具体采用的算法有关,与2B2成正比。

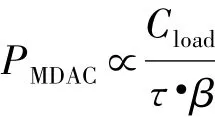

MDAC的功耗受等效负载电容、信号建立速度和反馈系数影响。下面以第2级子ADC的MDAC为例推导这些参数之间的关系。

图4中MDAC的功耗主要是其中运放的功耗PAMP,与工作电流成正比;而工作电流又与管子跨导gm和电压的变化(管子栅源电压Vgs和开启电压Vt之差)成正比,因此可用以下公式来表示:

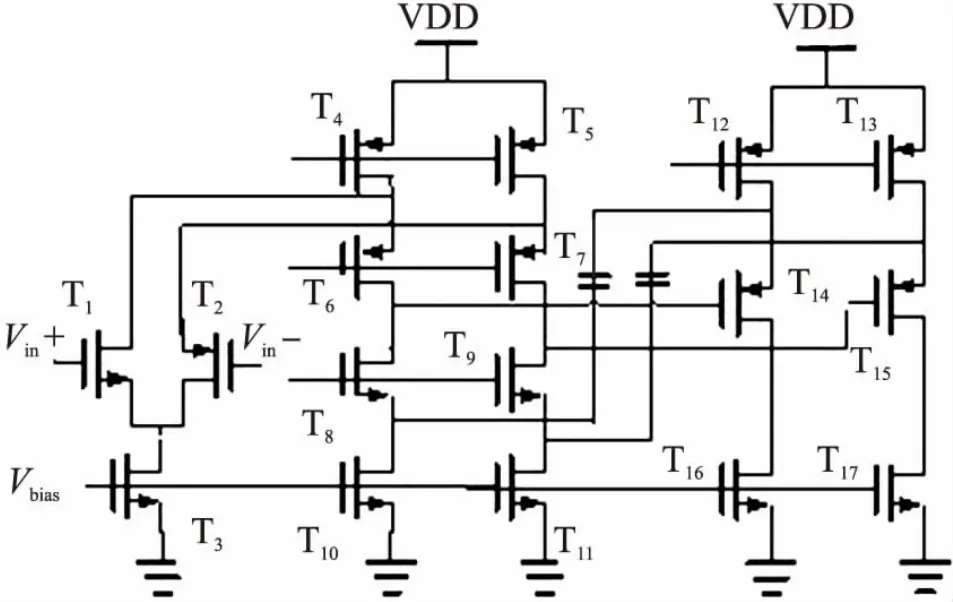

定义运放信号建立过程的时间常数为τ,由于每级MDAC信号的建立速度相等,因此可以当作一个常数,其应为-3 dB频率f-3 dB的倒数,而f-3 dB与单位增益频率fUG之间相差的倍数就是反馈系数β,fUG为跨导与负载电容的比值,因此时间常数可用以下公式表示:

由此公式可计算得到跨导为:

假设运放输入管的过驱动电压都相同,则工作电流仅与跨导成正比,即I∞gm;

因此运放功耗为:

从上面的表达式可以看出,MDAC中运放的功耗与负载电容成正比,与运放的反馈系数β成反比。

3.2缩放系数的计算

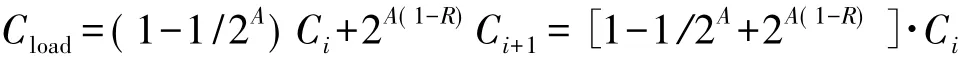

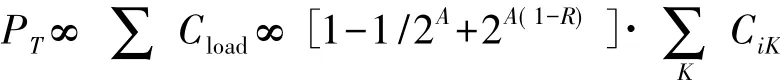

定义缩放系数为S,每级的有效精度A,相关系数R,即S=2-AR,假设本级采样电容为Ci,那么下一级采样电容Ci+1=SCi,只考虑下一级采样电容的情况下,由上面分析可以得到负载电容为:

反馈系数β=1/2A,因此负载电容为:

因此与每一级负载电容总和成正比的整个ADC的功耗PT可以用公式表示为:

每级ADC有效精度为2,在功耗最低时计算得到的缩放系数为0.25,作为第2级~第6级的设计依据。

3.3采样电容的设计

在Pipelined ADC中噪声NA主要来自采样开关电容和运放中MOS管的热噪声NR。假设每级都采用同样的精度n bit,可以得到每级采样电容Ci和噪声NA的关系:

由上面计算得出的缩放比例代入到上式,并把热噪声NR近似为8 bit量化噪声,就可以算出第1级采样的电容值;另外考虑本文ADC所采用的加工线参考工艺文件中所提供的电容失配比例,可以算出在保证8 bit精度的情况下所采用的电容值大小。综合考虑,选用了1 000 fF的电容作为第1级的采样电容,第2级250 fF。第2级的开关的尺寸也会根据相应的电容缩放比例进行缩放,来保证在信号通过快闪ADC与放大器的两条通路上的阻抗匹配。

3.4第2级子ADC的MDAC中运放结构的设计

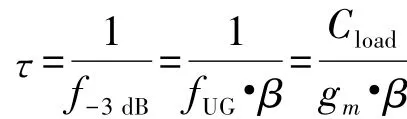

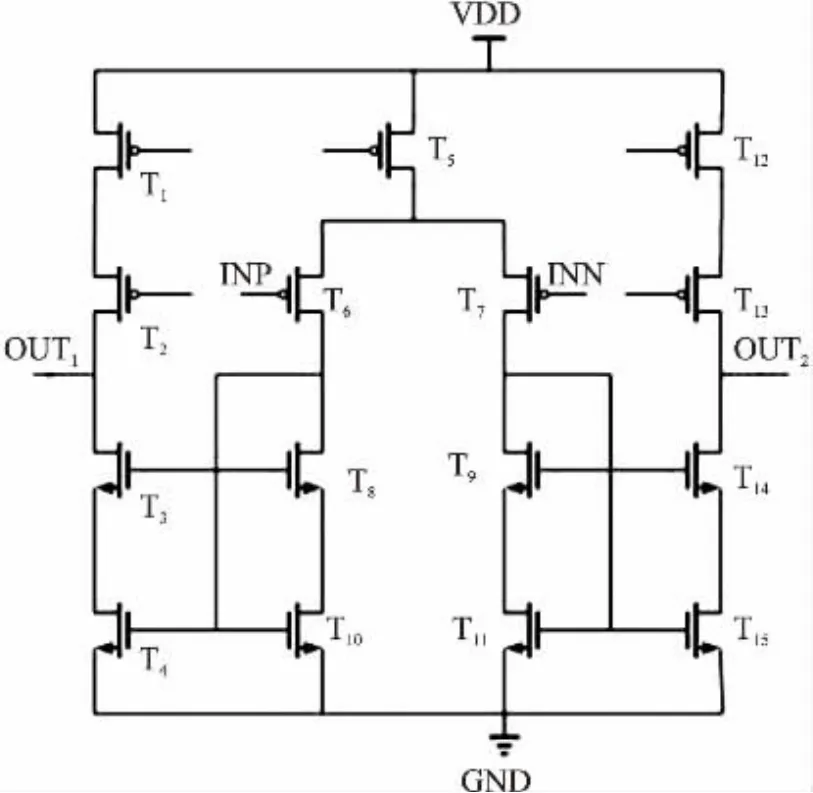

上面已经提到,第1级子ADC中的MDAC运放的增益要大于60 dB,单位增益带宽要大于378 MHz。采用与以上同样的方法,计算得到第2级子ADC中MDAC的增益要大于57 dB,单位增益带宽大于350 MHz。经过综合考虑,采用图5所示的对称型单级点放大器就可以实现这些指标。

图5中每一个管子的尺寸为:T1/T12为300 μm/0.6 μm; T2/T13为300 μm/0.5 μm; T3/T14为300 μm/1 μm; T4/T15为80 μm/0.2 μm; T5为120 μm/0.6 μm; T6/T7为36 μm/0.6 μm; T8/T9为30 μm/1 μm; T10/T11为8 μm/0.2 μm。

图5 第2级子ADC中MDAC的运放结构

3.5第2级ADC的仿真结果

对以上第2级ADC进行完整的仿真。仿真条件为:电源AGND = 0 V; AVDD = 1.8 V;温度为27 ℃;偏置电流101 μA;负载电容为250 fF。

3.5.1第2级ADC的功能仿真

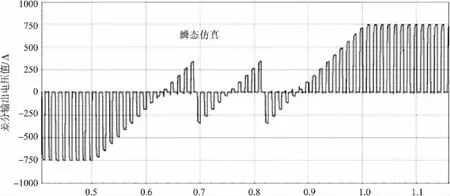

输入为差分斜波,300 ns为1.275 V,1 μs时为525 mV;仿真得到图6所示的传输函数。

图6是针对第2级ADC所作的瞬态仿真,其中横坐标是时间t,纵坐标是差分输出电压值,该仿真的主要目的是验证这一级ADC的传输功能。

图6 第2级ADC传输函数

3.5.2第2级ADC的性能仿真

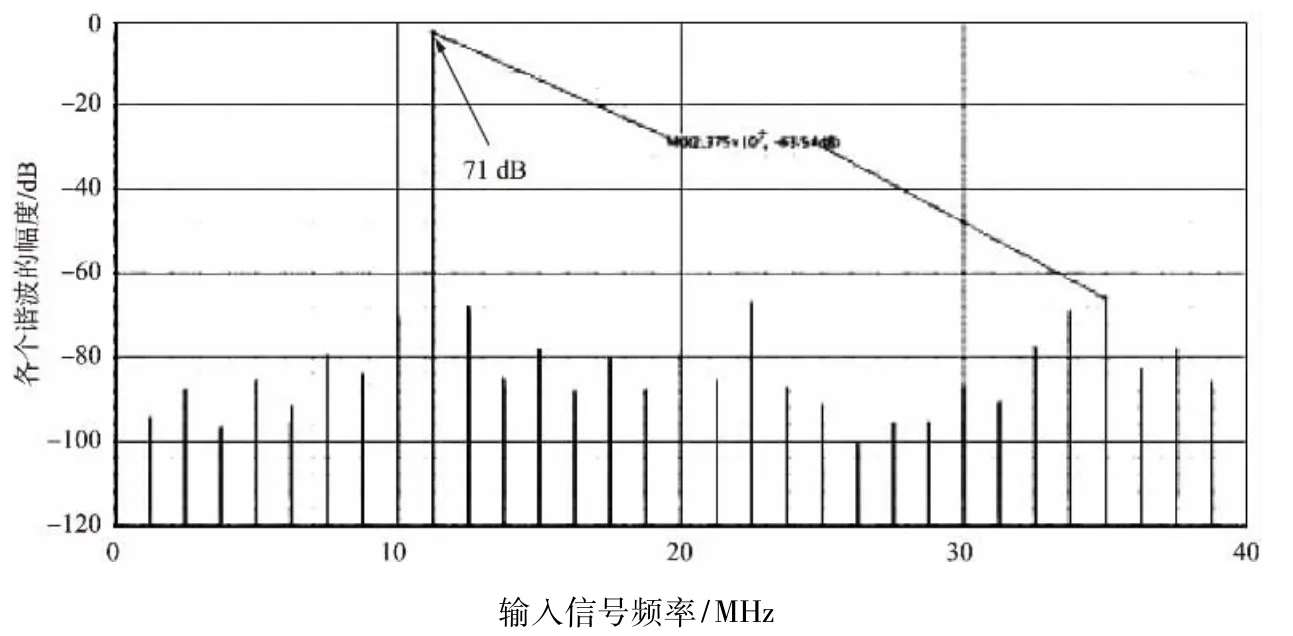

主要仿真第2级ADC的信号处理能力。输入一个频率为11.25 MHz差分正弦信号,通过理想DAC恢复,检测恢复的信号精度,然后进行快速傅里叶变换,得到第1级ADC的频谱图,如图7所示。

在图7中,横坐标是输入信号的频率,纵坐标是各个谐波的幅度,输入信号频率对应的幅度与次高谐波频率幅值之差就是该ADC的无杂散动态范围(SFDR),从图中可以看出,第2级ADC的SNR为71 dB,从中可以了解第2级ADC的信号失真情况。将以上数据导出,采用MATLAB工具进行处理,可以得到第2级ADC的有效位数ENOB为9.27位。这些性能指标跟第1级子ADC相比都略有下降,这就是逐级缩放技术,但整体ADC的信噪比和有效位数指标是可以保证的。

图7 第2级ADC的频谱图

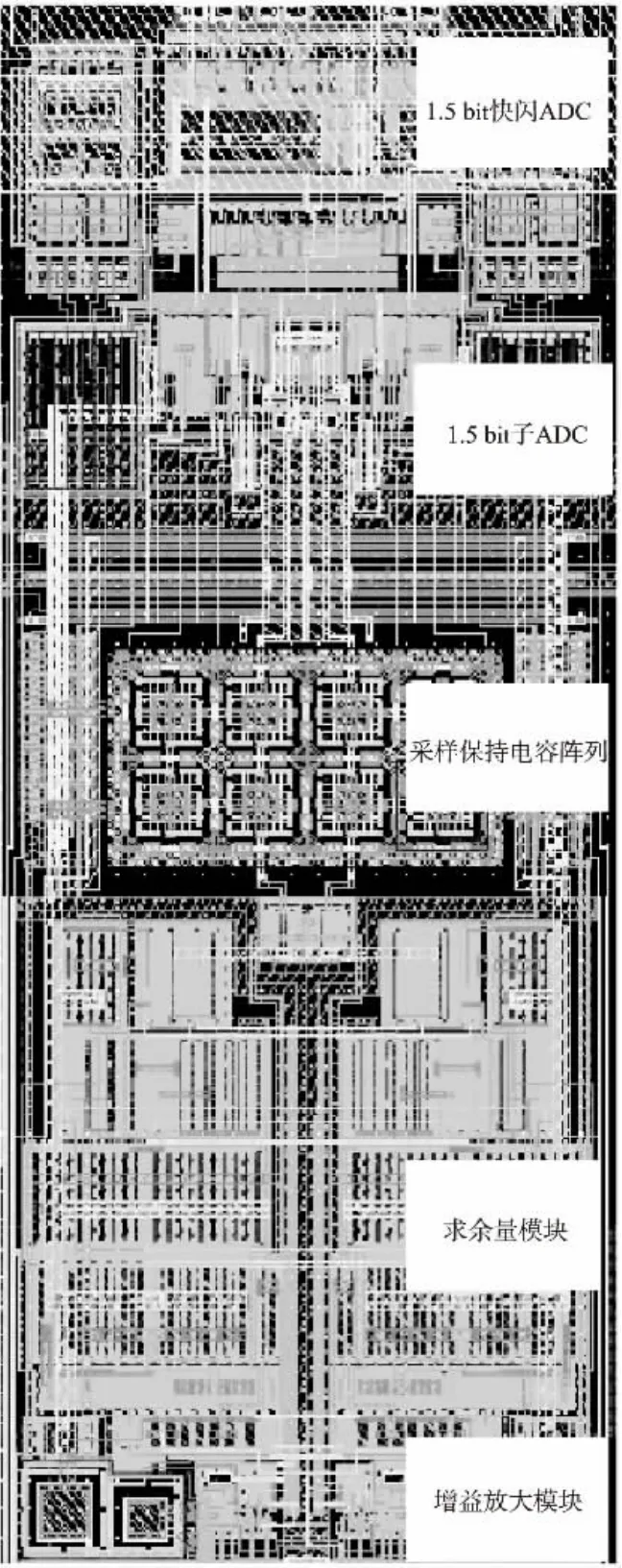

3.6第2级ADC的版图设计

采用以上逐级缩放技术进行第2级子ADC版图设计时要充分考虑其中MDAC电容的对称性问题,MDAC中的电容失配对整个MDAC的性能影响很大,因此在版图的规划中要非常注重对电容对称性的画法。另外由于整个MDAC是差分工作,因此MDAC中放大器的对称性也是必须要考虑的问题。图8为第2级子ADC的版图。

图8 第2级ADC的版图

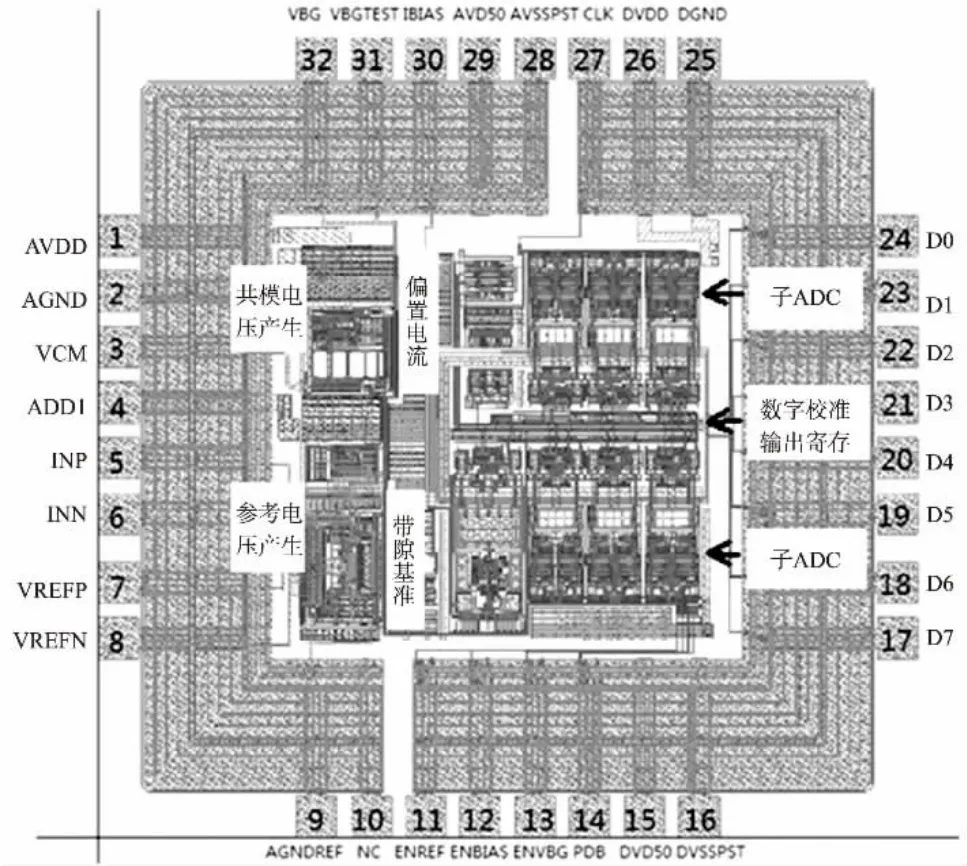

4 整个ADC的版图及实际测试结果

基于以上设计思想,完成整个ADC的设计,图9为整个8 bit Pipelined ADC的版图。

图9 8 bit流水线型ADC的版图

以上ADC基于0.18 μm工艺平台设计,经过流片后实际测试的结果为:功耗电流22 mA;在80 MHz采样率,11.25 MHz输入信号下,信噪比SNR可达到49.5 dB,有效位数为7.98 bit。

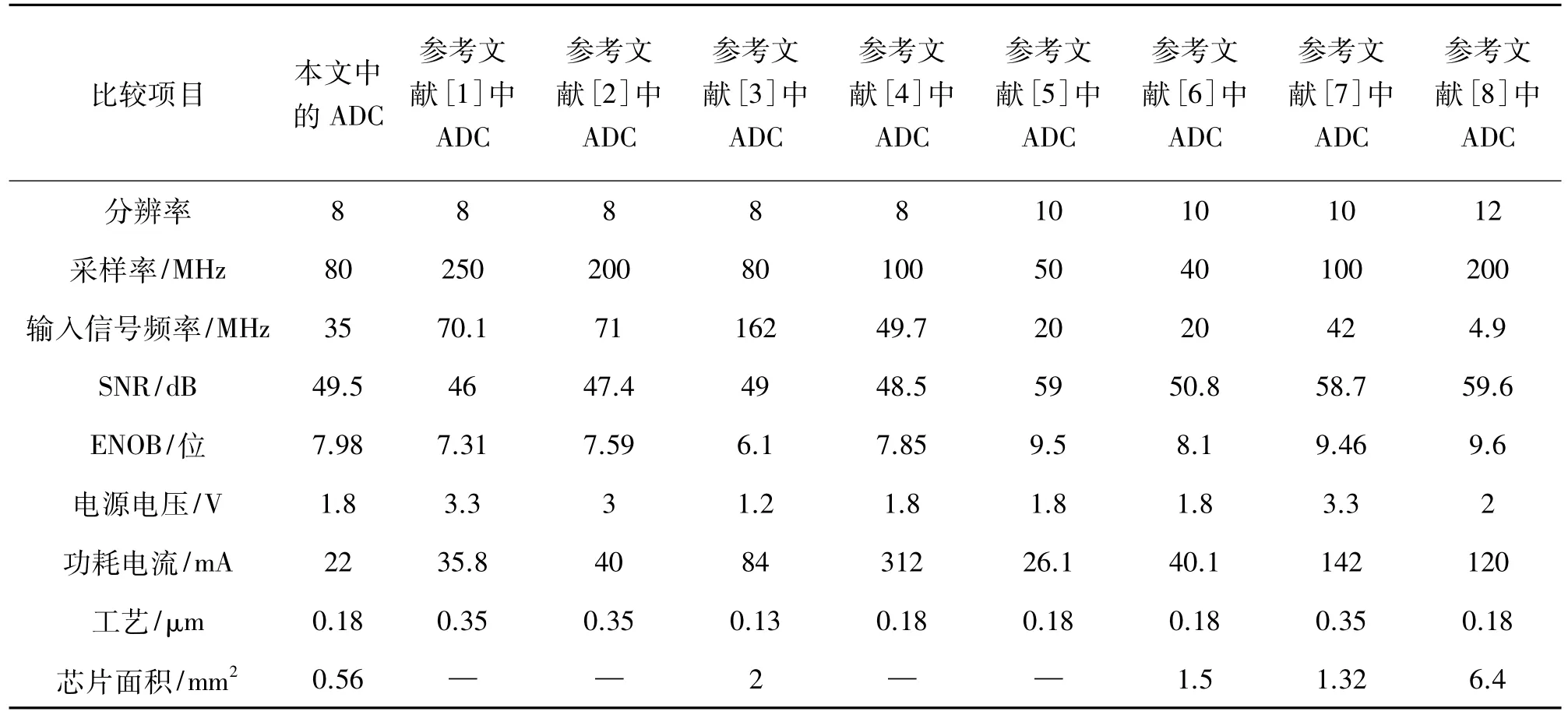

将以上ADC的实际测试结果和目前业内同类ADC的性能进行比较,结果如表1所示。

从表1可以看出,本文提出的ADC首先在信噪比(SNR)方面较其他ADC要高,在80 MHz采样率,11.25 MHz输入信号下达到49.5 dB,有效位数(ENOB)也达到7.98,其他8 bit ADC的信噪比都没有超过49 dB,有效位数也低,表中其他ADC因位数要高,分别为10 bit、12 bit,因此SNR和ENOB自然要高,不作为比较对象;其次本文提出的ADC功耗较低,在1.8 V下,其功耗电流只有22 mA,而表中其他大部分ADC的功耗电流都大大超过22 mA,其中高位数的ADC功耗尤其大;最后这个ADC的芯片面积较小,只有0.56 mm2,而其他ADC的面积都远远超过这个数值,因此本文提出的ADC非常适合于片上系统(SOC)集成应用。综合考虑功耗、信噪比和芯片面积等指标,本文提出的ADC较参考文献[1-8]中所描述的同类ADC有一定优势。

表1 本文ADC与同类ADC性能参数比较

5 结论

本文介绍了一种8位、基于0.18 μm工艺平台、采样率为80 MHz的高速ADC,该ADC采用流水线架构。在该ADC设计中,通过精确设计每一级子ADC中的运放结构实现无采样保持技术,另外在各级子ADC电路结构中逐级缩放等比较独特的设计技术,而版图设计中考虑每一级ADC中的电容及放大器的对称性,以减小电容失配对整个ADC性能的影响等,使得该ADC具有较小的功耗和芯片面积,且信噪比较高,整体性能比较优越。

参考文献:

[1]席改娟.8位250 Msample/S流水线型ADC的设计与研究[D].西安:西安电子科技大学,2010.

[2]宋静慧.一种双通道8-bit 200 Msample/s时间交织流水线ADC的研究与设计[D].西安:西安电子科技大学,2012.

[3]Nieminen T,Halonen K.An 1.2 V 440-Msample/s 0.13-μm CMOS Pipelinedd Analog-to-Digital Converter with 5 bit~8 bit Mode Selection[R].In proceeding of:NORCHIP,2010 Source:IEEE Xplore.

[4]Datasheet of AD9287,ADI[R].

[5]李天望,叶波,江金光,等.1.8 V 10 bit 50 Msample/s低功耗流水线ADC的设计[J].微电子学与计算机,2010,27(4):46-49.

[6]谭晓,郭桂良,杜占坤,等.1.8 V 10 bit 40 Msample/s的流水线模数转换器[J].半导体技术,2009,34(10):1046-1050.

[7]谭珺.3.3伏100兆采样频率10比特流水线结构模数转换器的设计和低功耗实现[D].复旦大学,2006.

[8]程华斌,魏琦,赵南,等.12位200 Msample/s交织A/D转换器设计[J].微电子学,2013,43(1):5-9.

[9]Walden R H.Performance Trends for Analog-to-Digital Converters [J].IEEE Commun Mag,1999,37(2):86-101.

[10]Cline D W.A Power Optimized 13-b 5 Msamples/s Pipelinedd Analog-to-Digital Converter in 1.2 m CMOS[J].IEEE 2002,31 (3):294-303.

[11]陈杉,杨银堂,朱樟明,等.一种应用于SOC的4位超高速CMOS Flash A/D转换器[J].微电子学,2008,38(1):85-88.

[12]Liechti I,Tajalli A,Akgun O C,et al.A 1.8 V 12-bit 230 Msample/s Pipelined ADC in 0.18 μm CMOS Technology[C]//IEEE ASIA Pacific Conf Circ Syst.Macao,China,2008,21-24.

居水荣(1968-),男,汉族,江苏苏州人,江苏信息职业技术学院专任教师,研究员级高级工程师,主要研究方向为模拟集成电路以及大规模数模混合集成电路的设计,jun1979wen@163.com。

Industrial Measurement Technology Based on Point Cloud Registration*

CHANG Jiang1,QIN Pinle1*,LIU Maomao1,CHEN Xiaoqing1,ZHANG Bin2

(1.College of Computer and Control Engineering,North University of China,Taiyuan 030051,China;

2.College of Economics and Management,North University of China,Taiyuan 030051,China)

Abstract:To match measurement point cloud of the products to be tested and the standard point cloud,manufacturing deviation value of products is obtained,so precision measurement can be evaluated.Firstly,principal component analysis is used for pre-matching.Next,by using random sample consensus the matching point pair of high contact ratio can be selected.Finally,closest point iterative is used for getting the point cloud registration with high precision.Using RANSAC to extract the matching point pair of high contact ratio is convenient to get the most optimal space coordinate transformation parameters,making higher registration accuracy.Estimating of the sampling frequency can infer point cloud registration iteration,and then may reduce operation time effectively.Experiment results show that the algorithm is effective.

Key words:products manufacturing; precision measurement; principal component analysis; random sample consensus; closest point iterative

doi:EEACC:721010.3969/j.issn.1005-9490.2015.04.042

收稿日期:2014-08-05修改日期:2014-08-21

中图分类号:TN432

文献标识码:A

文章编号:1005-9490(2015)04-0922-07

项目来源:国家“核高基”重大科技专项项目(2009ZX01034-002-001-005);国家863计划项目(2009AA01Z258)