一种用于并联LED驱动的分时复用控制电路

何业军,尹 婷,许 晶

(1.广东省中山职业技术学院,广东 中山 528404;2.中国电力科学研究院,湖北 武汉 430074)

引言

光源,LED已经广泛用于照明光源和背光光源[1-3]。与传统光源相比,LED光源色彩还原性好、寿命长、不含汞、环保,可以低电压工作,响应速度快,控制较为方便,且设计灵活[4]。

近年来,高亮度LED以节能和长寿命的优势开始替代白炽灯、卤素灯、荧光灯、HID灯等光源,在建筑照明、装饰照明以及标识牌照明等方面的应用,为LED的发展提供了更为广阔的前景[5]。

在背光应用方面,LED背光已经逐渐取代传统的CCFL背光,LED不仅可以使屏幕厚度减半,还可以使功耗降低50%[6]。

在LED的实际生产过程中,由于在晶圆生成、切割、封装等环节的环境不可能完全一致,在出厂前得到的LED产品之间实际上存在着较大的差异。由于LED器件本身特性,在导通发光时,其电流变化率远小于电压变化率[7],故出厂筛选时,大多基于一致电流发光值,并给出导通电压范围[8]。

这样在实际应用中,LED的亮度取决于流过它的电流,将多个LED组合使用时,各管电流均必须相同,整个组件才能产生一致的亮度。实现相同电流最简单的方法,是串联多个LED,这样不用再特别筛选LED, 就能确保流过各个LED的电流相同。但是串联时的总电压为多个LED的导通电压之和,一般需要使用具有升压功能的LED驱动电路,使得成本增加;且一个LED发生故障就会使整串LED失效。将多个LED并联的设计方法,一般无需的升压电路,电磁干扰较小,容错性较强,但难以保证各LED的电流相同。但为了保证并联LED亮度的均匀性,必须对LED进行特别差异筛选,使得相同的正向电压有相同的电流。 随着所用LED组合数量的增加,成本也会因差异筛选而增加。 即使经过差异筛选LED的导通电压值仍会存在一个变化范围,影响亮度的均匀性[9-10]。

本文讨论了一种无需对LED进行特别差异筛选的LED驱动电路。

1 原理

1.1 总体思路

采用分时复用的思路,对于多个支路并联的情况,轮流使用每个内部驱动通道驱动外部的LED。当分时频率足够高时,各个支路的平均电流相等,且肉眼无法识别。为了实现足够高的分时频率,使用了高速运算放大器。

1.2 连续可调的控制电路

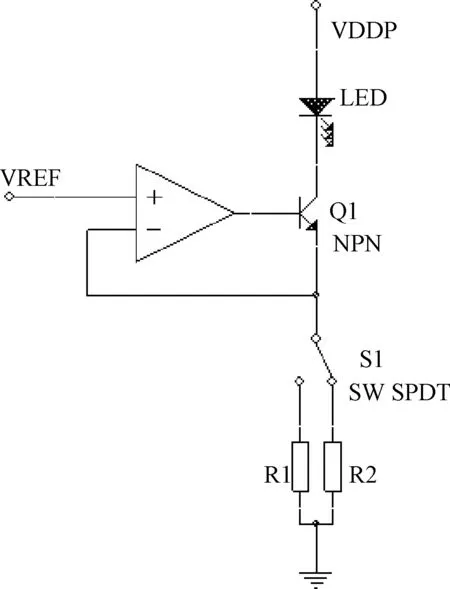

传统用固定参考反馈电压,几级可调反馈电阻,如图1所示,VREF为固定反馈点参考电压,通过运算放大器使得反馈点的电压保持等于VREF,通过调节开关S1选择不同的电阻R1或者R2来决定通过发光LED的电流大小,从而调节发光强度。由于开关的数量有限,因而能调节的发光亮度也是有限而不连续的。

图1 可调电阻反馈电路Fig.1 Feedback Loop with Variable Sense Resistor

本电路用可调参考反馈电压,固定反馈电阻[11-14]。如图2所示,IREF为参考电流,对Rv和R1取适当的比例,在集成电路里可以通过版图设计取得非常高的比例精度,于是通过发光LED的电流可以精确通过IREF取得。这里IREF可以在外部控制信号输入或者在内部通过控制信号生成,为连续模拟信号,因此通过发光LED的电流连续可调,发光亮度连续可调。

(1)

图2 可调输入电流反馈电路Fig.2 Feedback Loop with Variable Current Reference

1.3 高速反馈控制电路

传统用二级或者三级运放驱动末级NMOS/NPN,反馈环路速度限制于主级点以及单位增益带宽。

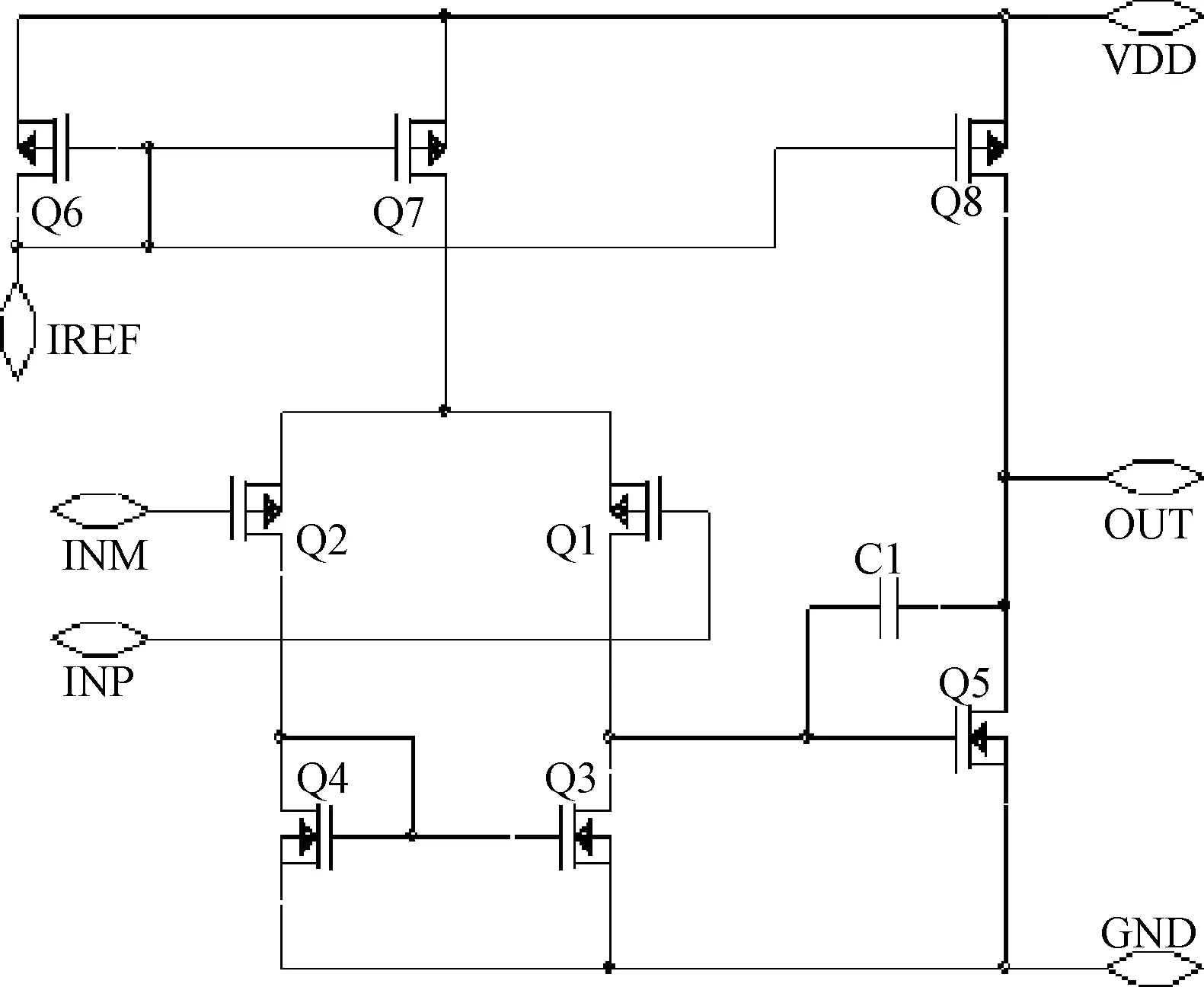

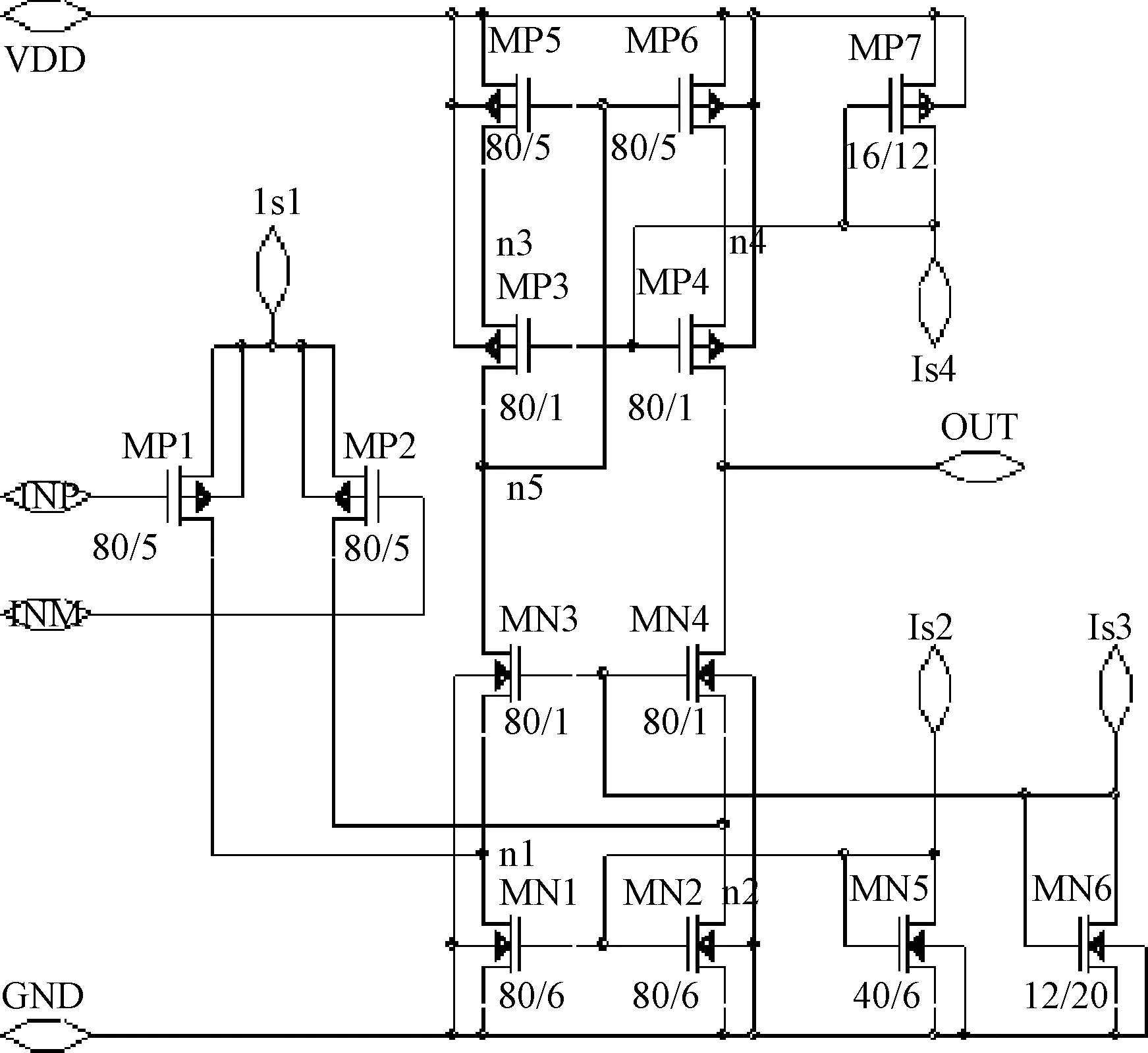

对于图1和图2中的运算放大器设计,传统如图3所示,整个反馈环路的主级点在于Q5的栅极,次级点在于运放的输出点OUT即图1中NPN Q1的基极。次级点决定了环路的单位增益带宽,直接限制了环路的相应速度。这里的次级点大小可以近似地计算为f0,即

(2)

图3 传统两级运算放大器Fig.3 Traditional Two Stage Op-Amp

Ro为OUT点的等效小信号电阻,Co为OUT点的等效小信号电容,近似为外部负载电容,即图1中NPN Q1的基级电容,这个电容大小取决于应用负载的需求和半导体工艺,很难在内电路设计改变。Ro近似为图3运放的输出阻抗。当运放的增益为A时,在保证环路稳定性的前提下,环路带宽近似为f,即

(3)

由于反馈电路需要足够的增益,A至少为70dB以上,即3000倍以上。在常见的CMOS工艺下,f0一般大约在几十到几百千赫兹,故整个环路带宽f一般在几十赫兹的量级,难以用于高速的分时电路。

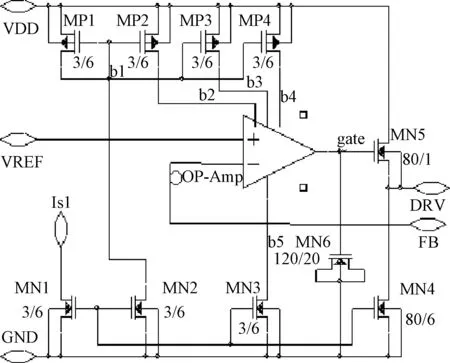

现在用单级折叠套筒运放加源跟随器[15],极大提高环路速度。

如图4所示,第一级放大采用折叠共源弓栅放大,取得足够大的增益和输出摆幅。第二级采用一个N MOSFET的源跟随器,取得很小的输出阻抗。对比图3中的运放,图4运放的输出阻抗显著降低,一般可降低近三个数量级,因此次级点往高频移动,环路单位增益带宽显著增大,环路反应速度大幅提高,基本可以满足时分电路的需求。

图4 高速带源跟随器的单级折叠套筒运放Fig.4 Signal Stage Folded Cascode Op-Amp with source follower

这种运放存在输出摆幅较小的缺点,最高为电源电压减去一个阈值电压,但是在系统应用中,可以通过恰当的选择,使得需求摆幅不需要达到太高,避免图4运放的这个弱点。

1.4 基于时分原理的驱动电路

传统运放反馈环路存在工艺失调。对于现在的集成电路工艺,在实际流片过程中必然存在各种精度问题,直接导致器件的实际性能尺寸变化。在电路设计中应该完全一样的器件,在实际生产出来之后,都存在一定的失配现象。这种失配对于运算放大器而言,体现在应用中就是失调电压。图1或图2的反馈环路中,失调电压会导致反馈点(电阻采样点)的电压和预设电压有一个固定的偏差。通常这种偏差经验上会导致发光LED的电流有5%左右的误差。

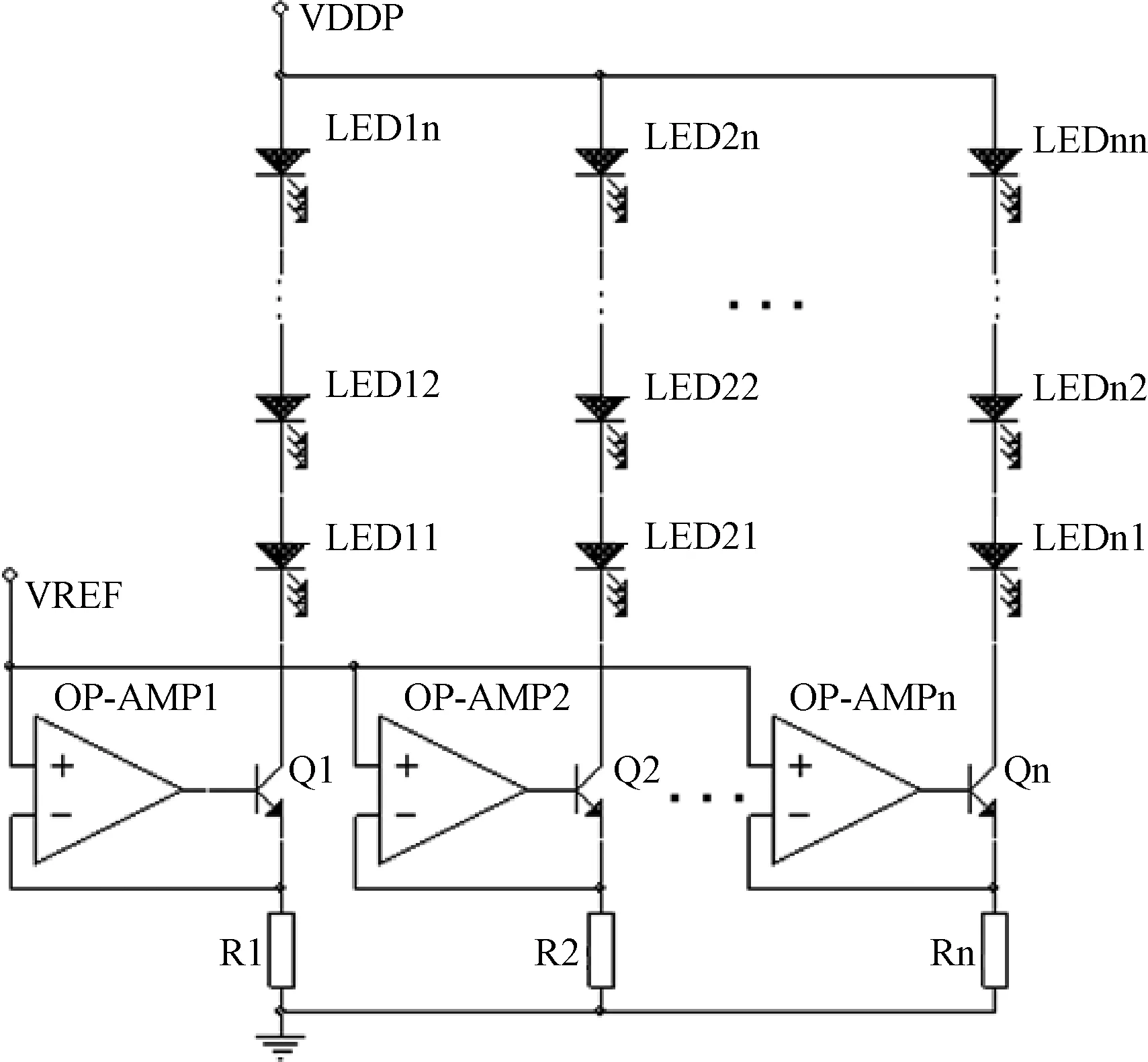

在实际应用中,如果使用单支路串联发光LED,这个不大的误差并不会导致严重的应用问题。但是,现在随着显示设备的尺寸不断加大,对于单一显示设备需要的背光LED越来越多,常见的大屏电视的背光LED可以多达十几甚至几十个[16-17]。如果这些背光LED采用单支路串联,需要LED的驱动电压达到一个很高的数字。例如,十五个3.2V的背光LED串联需要的驱动电压至少是四十八伏以上,过高的电压对应用电路的设计和外部分立器件的要求会更高,使得整个显示设备的成本上升,可靠性安全性下降。因此,比较多的时候,采用多支路并联的方式来驱动较多的发光LED[18],如图5所示。

图5 多支路并联LED驱动Fig.5 Parallel LED Driver

如图5所示,把多个发光LED分成几组,分别串联,降低每组发光LED个数,从而降低需要的LED驱动电压VDDP。如例中的十五个LED可以分成三组,每组五个,那么16V驱动电压就可以满足应用,降低整个系统需求。

多个并联支路会带来一个新的问题,即集成电路的工艺失配。如图5中运放OP-AMP1, OP-AMP2…OP_AMPn,有着不同的失调电压,R1,R2,…,Rn有着不同的电阻阻值,造成通过各支路的电路不完全同。在常规应用中,各支路的电流有着5%~10%的误差是比较常见的。对于发光LED来说,电流的变化直接反映到亮度的变化。对于大屏显示设备,如果背光LED的电流有5%~10%偏差,在显示设备上,则可以看到明显的亮度不均。

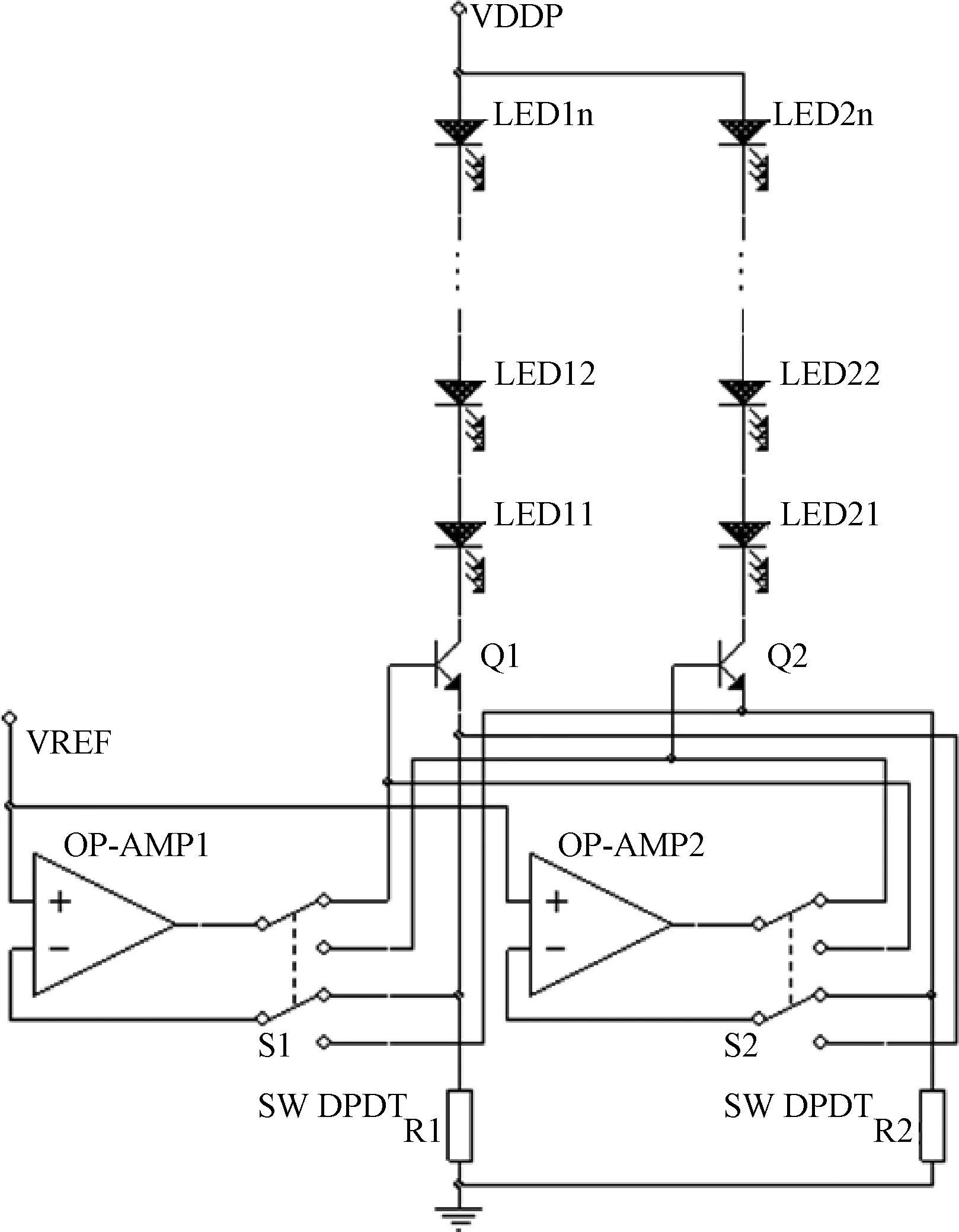

现在使用一种时分电路的方式,分时轮换使用每个通道轮流驱动各组背光LED,从而在宏观上,各个支路的平均电流近似相等,从而达到各支路亮度一致,图6所示为一个双通道的时分方式。两个通道驱动电路的控制系统轮流给两个通道使用,恰当的选择切换的时间和开关,可以使得两组LED的电流平均值接近相等。

图6 两路分时复用LED驱动Fig.6 Time-Division Rotation Driver with Two Channels

1.5 电路集成

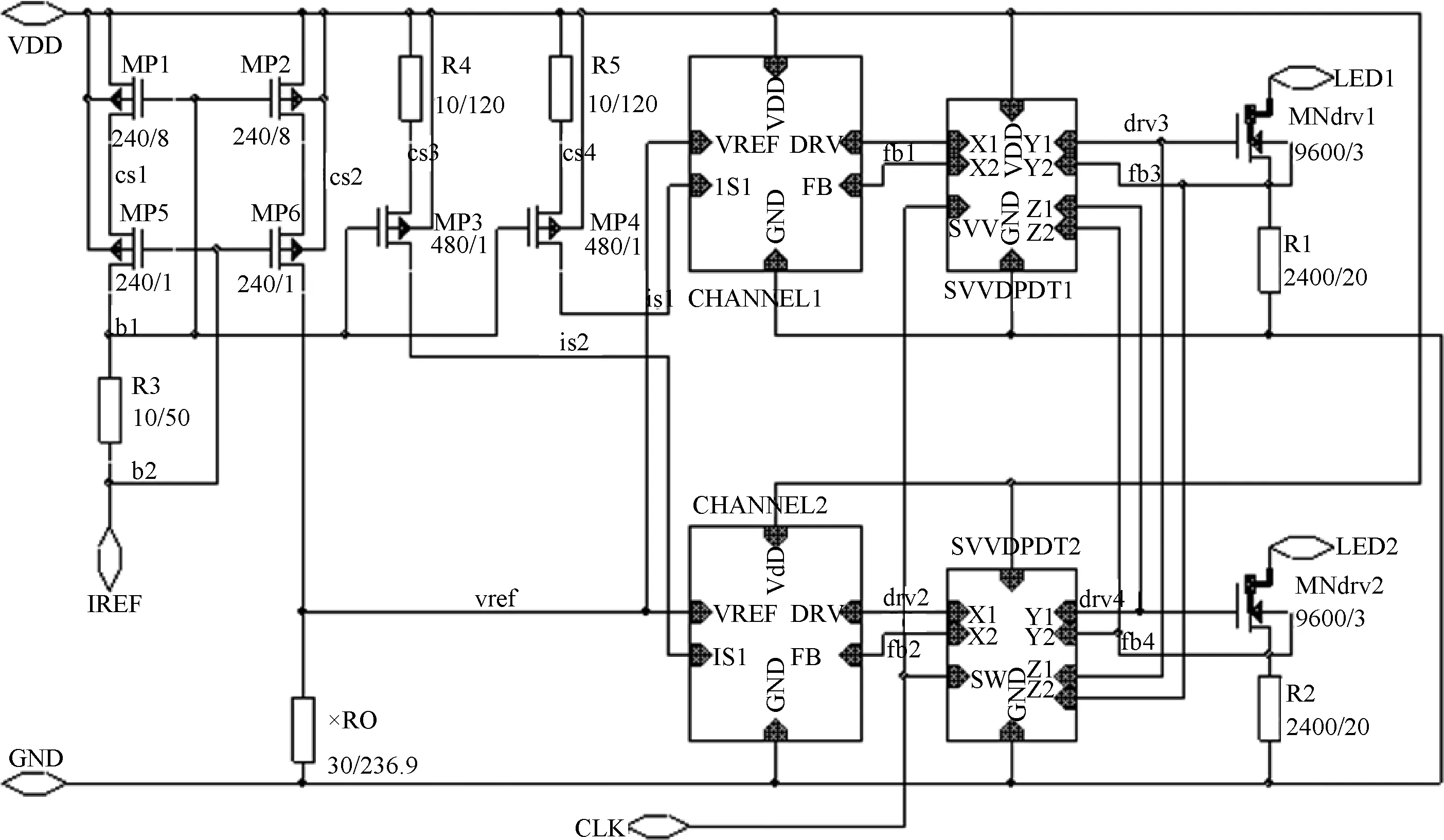

本电路设计目标为设计输出电流尽可能一致的多通道LED驱动电路,下面主要讨论双通道的驱动电路,多通道LED驱动电路可以简单类似推出。

由于时分电路的存在,LED的电流(亮度)会周期性的变化,如果时分的频率较低,可能被人眼察觉,因此,时分的频率不能太低。习惯上取1kHz以上可以取得较好的效果,频率越高LED的电路(亮度)均匀性越好,瞬态响应越快,但是电路实现难度越大。

对于时分的双通道驱动电路,有两个负反馈环路,并且两个环路部分以固定的频率交换使用部分电路,为了保证环路工作正常,每个独立环路必须有比时分调制频率更高的工作带宽,因此,反馈环路的中的运算放大器需要前文讨论的高速运算放大器。这里采用国内常用成熟的1μm模拟CMOS工艺来仿真这个电路。

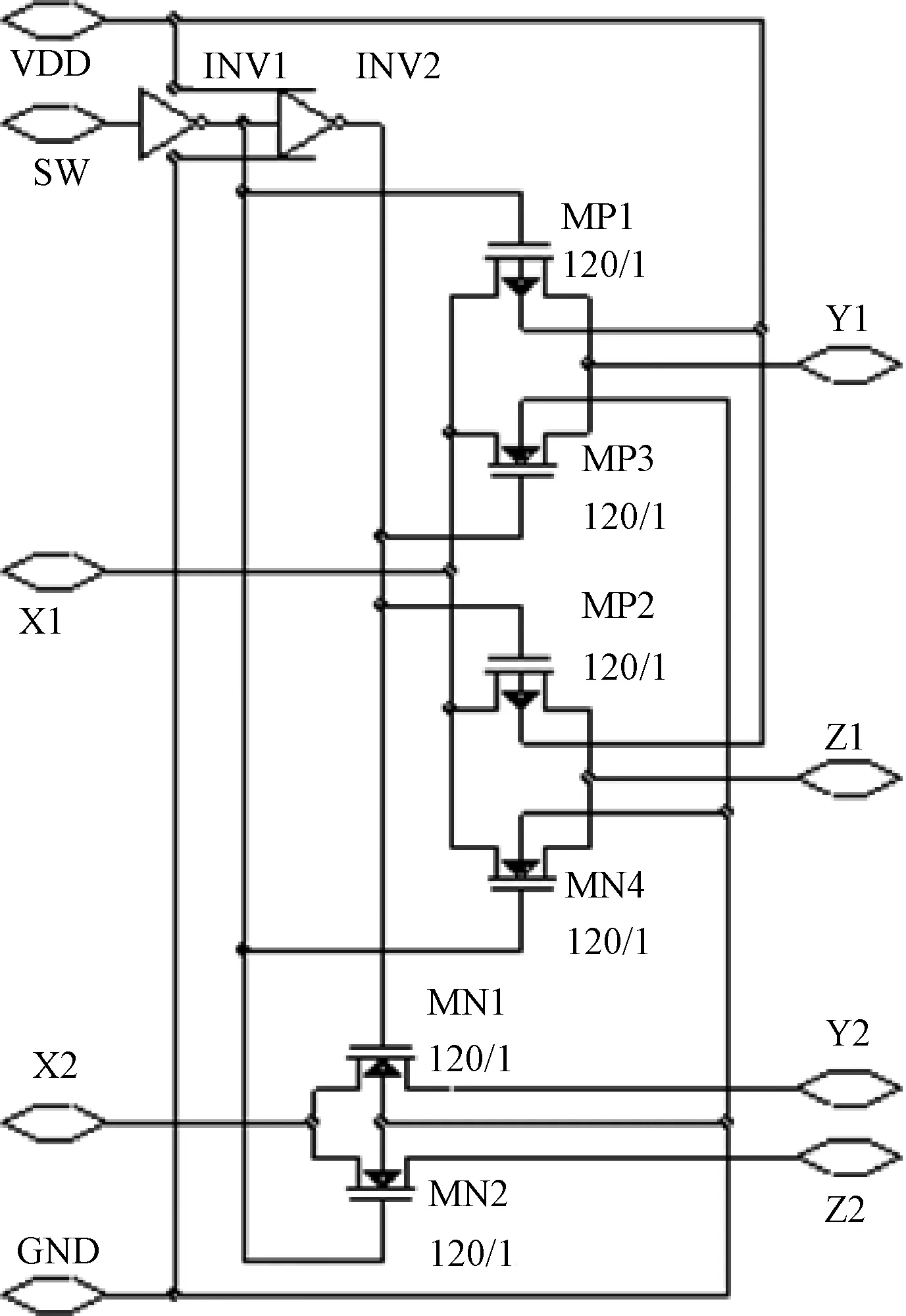

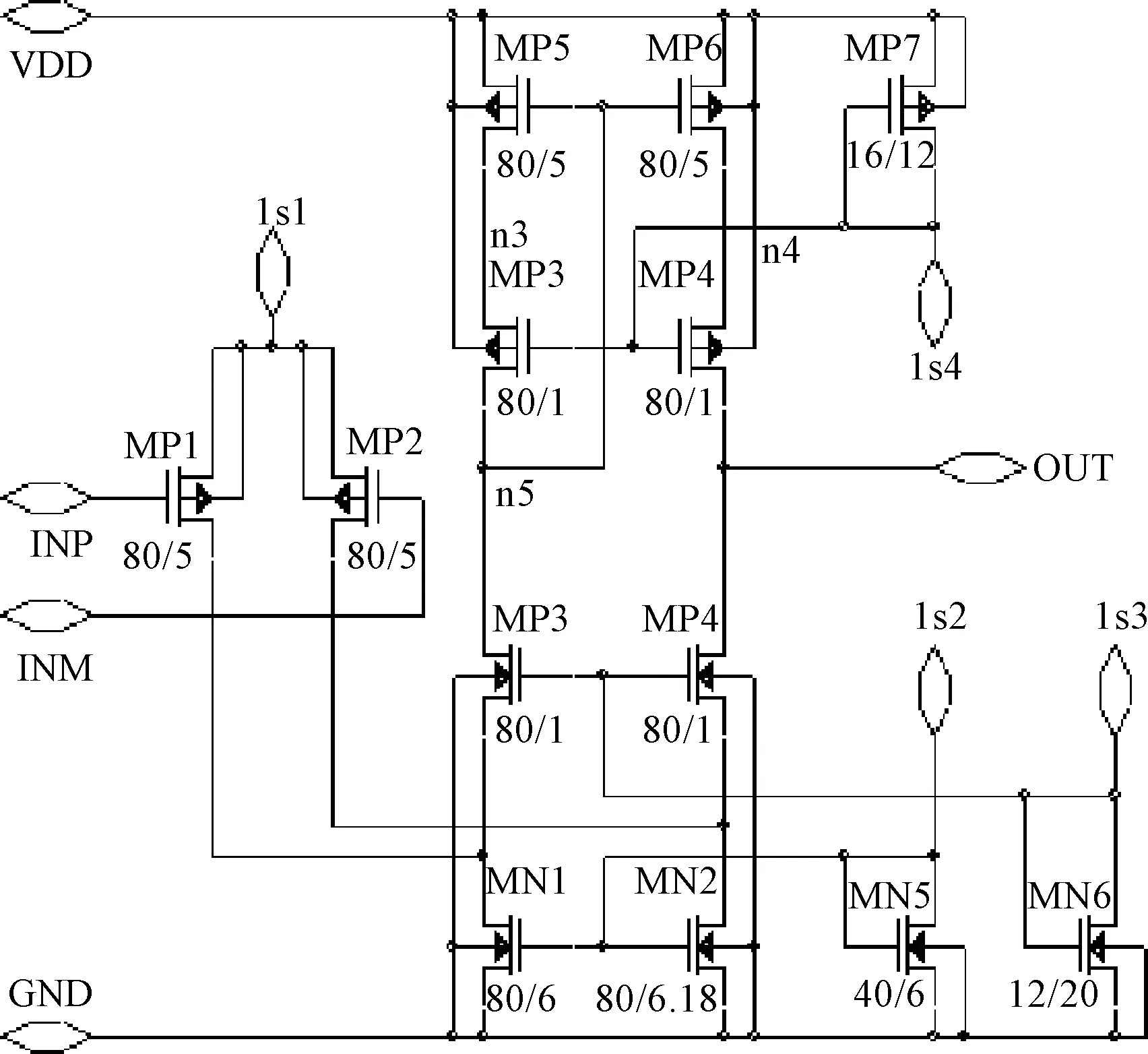

图7 反馈环路第一级运算放大器Fig.7 Op-Amp as the First Stage of Feedback Loop

图7为实际用于仿真的运算放大器的第一级。图8为运算放大器的整个电路,包括了输出级,偏置电路和补偿电路。整个负反馈环路中,仅运算放大器的第一级为放大级,故把主极点放在第一级的输出点,如图8中MN6的补偿电容。图9为双刀双掷开关电路。SW为开关选择,X1对应Y1, Y2; X2对应Y2, Z2。实际电路使用中,电流采样点FB一般选取较低,故X2仅使用单边NMOS作为开关。图10为总体集成电路,VDD/GND分别为电源/地线,设计工作电压为5V。LED1/LED2为两串LED的驱动输出。CLK为时分频率的时钟输入,设计为100kHz,占空比50%的方波。IREF为参考电流输入,输入范围为1μA~100μA,分别对应LED1/2的输出电流为1mA~100mA,放大比例为1000倍。

图8 单通道LED驱动电路Fig.8 Single Channel LED Driver

图9 双刀双掷开关Fig.9 DPDT Swtich

图10 顶层电路Fig.10 Top Level Schematic

2 仿真计算

仿真为基本LED驱动功能,驱动两串LED,每串串联有九个LED。

建立仿真电路图如图11所示。采取工艺为1μm 40V 高压模拟工艺,根据晶圆厂的工艺文件以及通常流片经验,假设在第2通道的运算放大器的第一级存在一对NMOS有3%的失配,如图12所示MN2比MN1的沟道长度大3%:电路的工作电压设定为5V,延时20μs,发光LED的工作电压设定为36V,延时30μs;每个驱动通道驱动的一串LED为九枚;电路工作频率为100kHz,CLK信号为占空比50%的100kHz方波,延迟50μs生效,即初始50μs里CLK信号固定为0,此时存在失配的运算放大器通道二对应D11~D19串LED;IREF信号为1~100μA的电流,输出LED电流设计值为IREF的一千倍,延时25μs。仿真结果如图13~图19所示。

图11 仿真测试电路Fig.11 Simulation Circuit Schematic

图12 失配运算放大器Fig.12 Op-Amp with mismatch

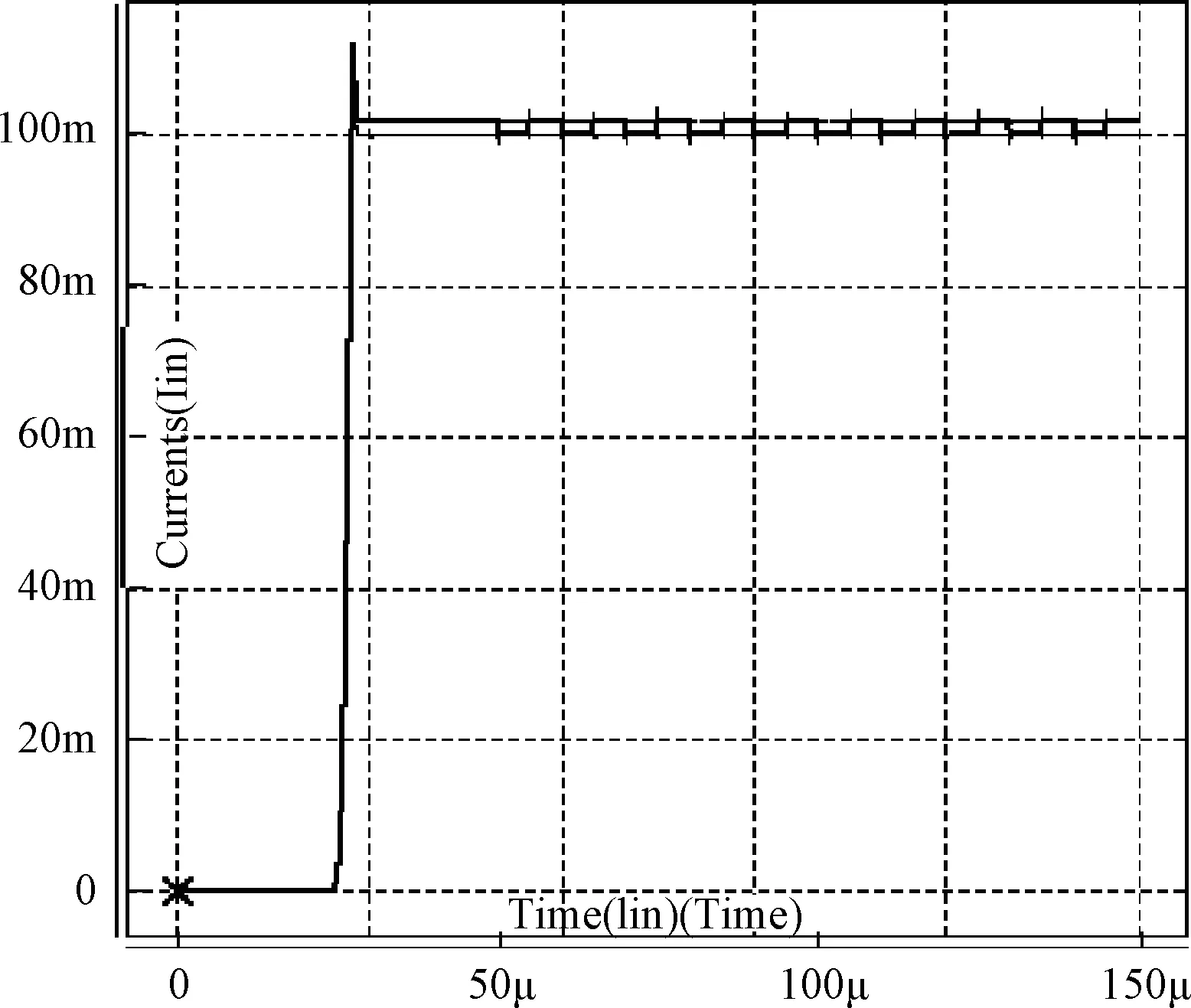

当IREF=100μA时结果如图13, 粗实线为通道1电流,细实线为通道2电流,横轴为时间,每格30μs,纵轴为电流值,每格20mA。

图13 IREF=100μA 仿真结果Fig.13 Simulation Results with IREF=100μA

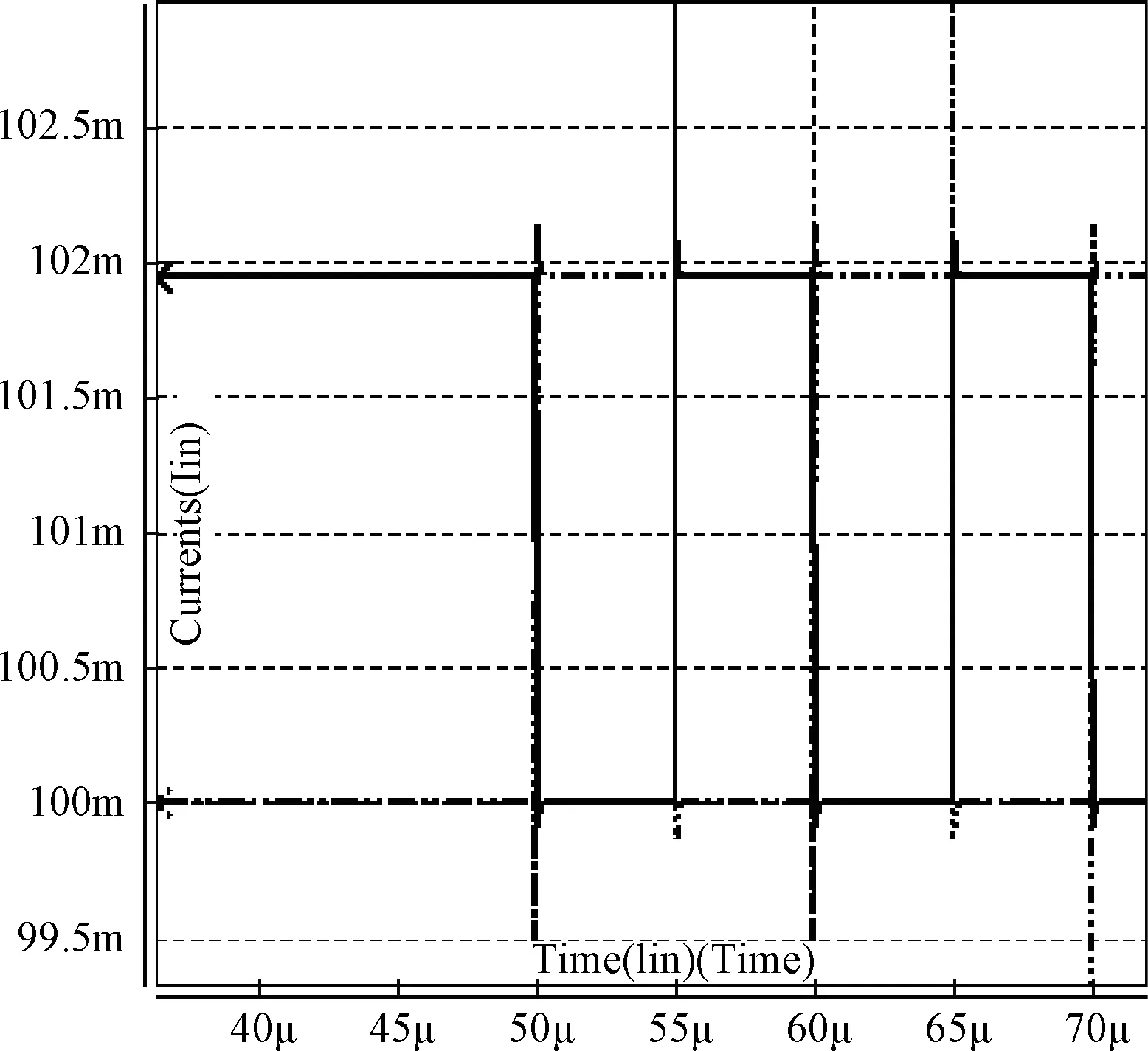

图14 IREF=100μA 仿真结果放大Fig.14 Zoom in of Simulation Results with IREF=100μA

图15 IREF=10μA 仿真结果Fig.15 Simulation Results with IREF=10μA

图14为图13在36~72μs的局部放大。实线为通道1电流,点划线为通道2电流,横轴为时间,纵轴为电流值,每格0.5mA。可见,在CLK工作之前,即50μs之前,通道 2 的电流为准确的100mA,而由于“工艺偏差”而“存在”失配的通道1 电流约为101.9mA,出现了1.9%的偏差。在时钟CLK工作之后,通道1和通道2交替使用内部的两个运算放大器,输出电流轮流在100mA和102.3mA之间切换,且占空比相同,因此,在宏观的时间长度内,通道1和通道的平均电流都是100.95mA,基本不存在明显偏差。

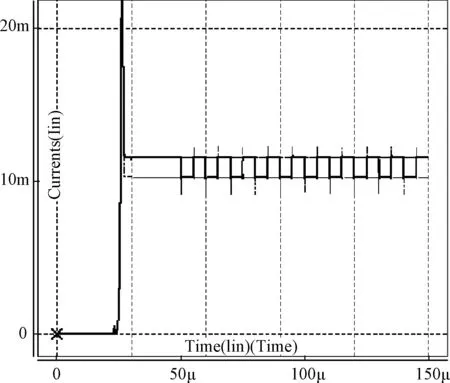

当IREF=10μA时结果如图15,粗实线为通道1电流,细实线为通道2电流,横轴为时间,每格30μs,纵轴为电流值,每格20mA。

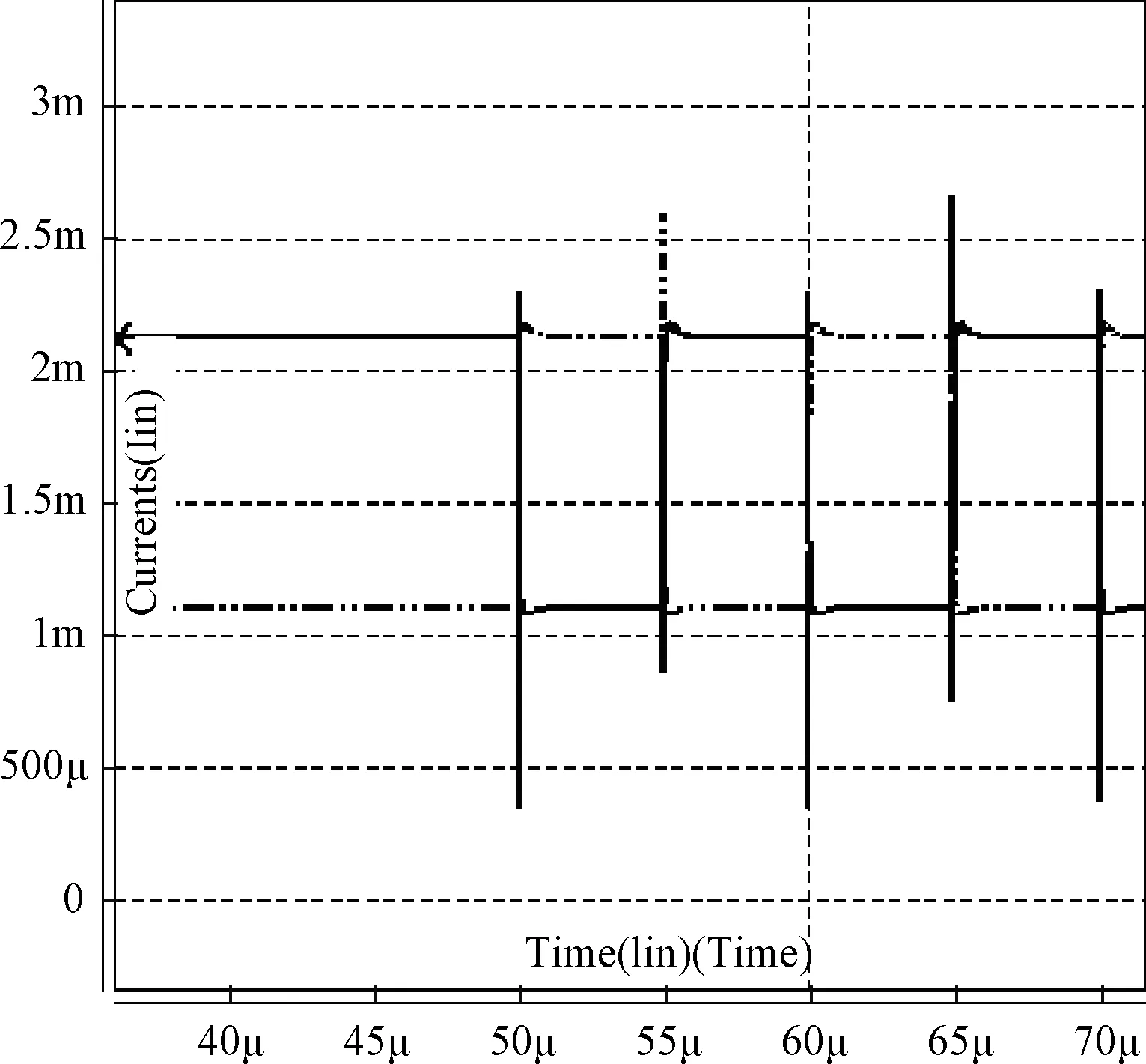

图16为图15在36~72μs的局部放大。可见,在CLK工作之前,即50μs之前,实线为通道1电流,点划线为通道2电流,横轴为时间,纵轴为电流值,每格0.5mA。可见,通道 2 的电流为的10.3mA,而由于“工艺偏差”而“存在”失配的通道1电流约为11.6mA,出现了13%的偏差。在时钟CLK工作之后,通道1和通道2交替使用内部的两个运算放大器,输出电流轮流在10.3mA和11.6mA之间切换,且占空比相同,因此,在宏观的时间长度内,通道1和通道2的平均电流都是10.95mA,基本不存在明显偏差。

图16 IREF=10μA 仿真结果放大Fig.16 Zoom in of Simulation Results with IREF=10μA

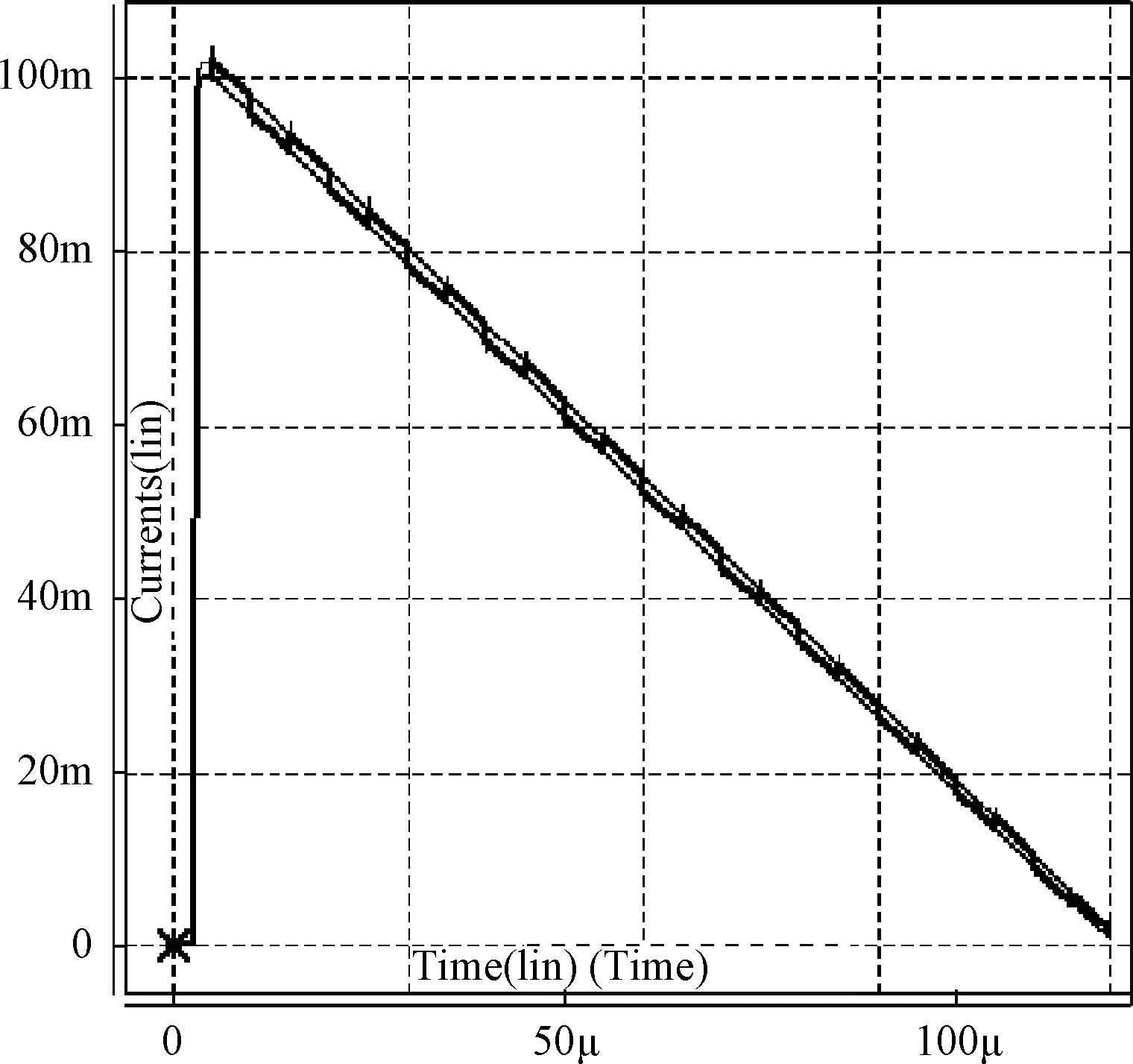

当IREF=1μA时结果如图17,粗实线为通道1电流,细实线为通道2电流,横轴为时间,每格30μs,纵轴为电流值,每格0.5mA。

图17 IREF=1μA 仿真结果Fig.17 Simulation Results with IREF=1μA

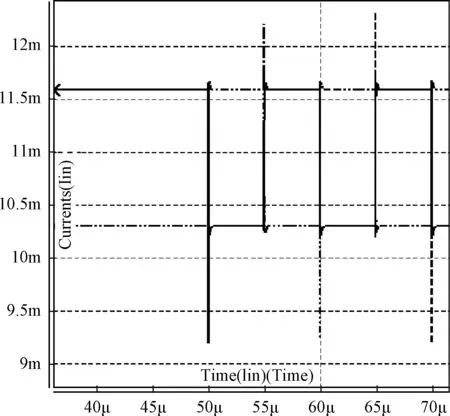

图18为图17在36~72μs的局部放大。可见,在CLK工作之前,即50μs之前,实线为通道1电流,点划线为通道2电流,横轴为时间,纵轴为电流值,每格0.5mA。可见,通道 2 的电流为的1.1mA,而由于“工艺偏差”而“存在”失配的通道1 电流约为2.1mA,出现了91%的偏差。在时钟CLK工作之后,通道1和通道2交替使用内部的两个运算放大器,输出电流轮流在1.1mA和2.1mA之间切换,且占空比相同,因此,在宏观的时间长度内,通道1和通道的平均电流都是1.6mA,基本不存在明显偏差。

图18 IREF=1μA 仿真结果放大Fig.18 Zoom in of Simulation Results with IREF=1μA

综上三种不同的负载仿真结果,在没有采用时分电路的传统驱动方式前,负载越轻,通道间的相对偏差越大,当输出负载为最大值的1%时,偏差可以达到一倍左右。在采用时分电路之后,虽然通道输出与预想值之间存在的绝对偏差没有减小,但是通道之间的相对偏差小到可以忽略不计。

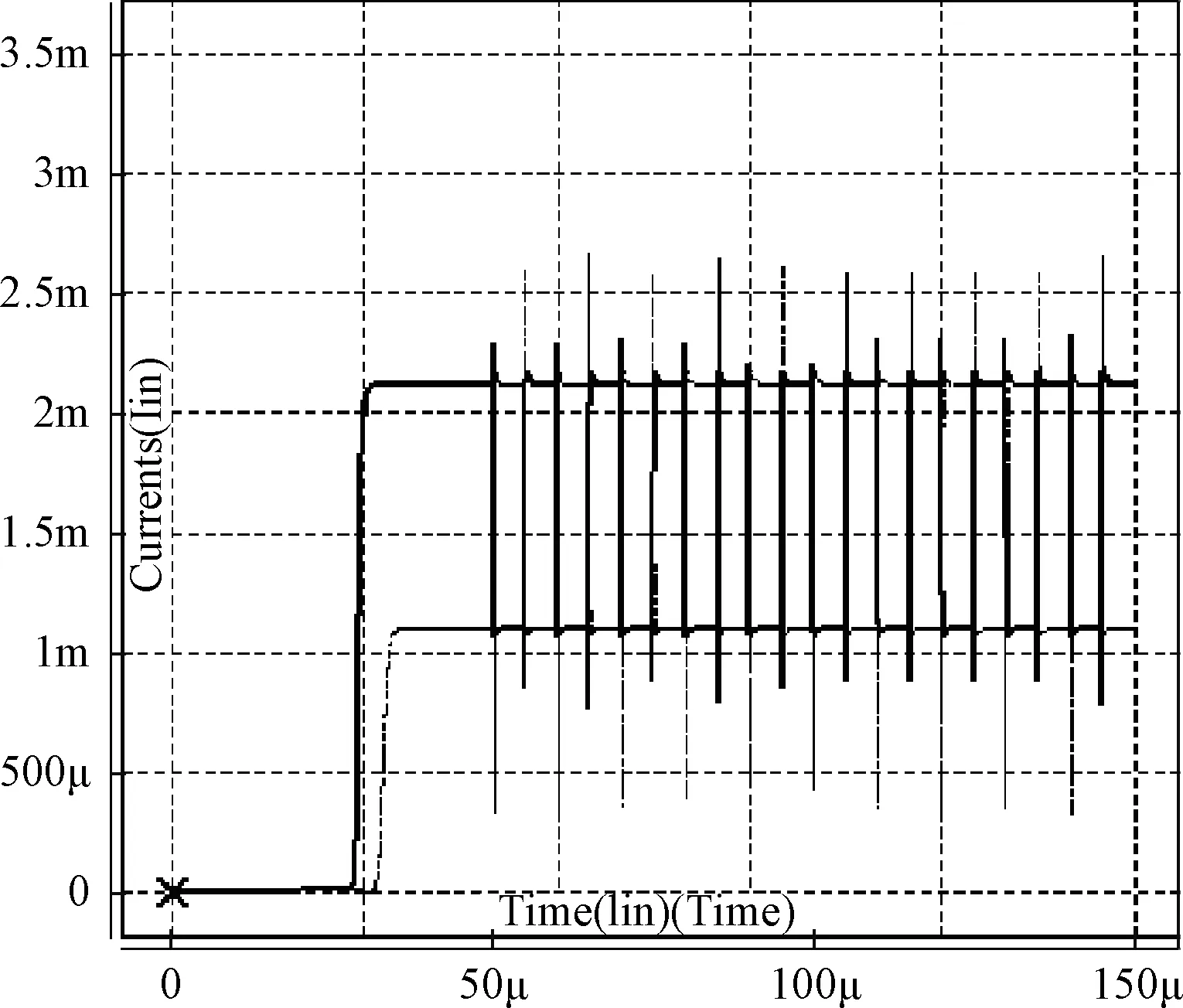

图19为变化的IREF仿真,从 5 μs到120 μs,IREF线性的从100mA降到0。粗实线为通道1电流,细线为通道2电流,横轴为时间,每格30μs,纵轴为电流值,每格20mA。从约5μs处起,通道1,2的电流分别为102mA和100mA,在约10μs处,两通道交换使用内部放大器,通道1,2电流变为95.6mA和97.5mA,在约15μs出,再次交换使用内部放大器,通道1,2电流变为93.3mA和91.3mA。在约110μs处,通道1,2电流为9.2mA和10.5mA,在约115μs处,再次交换使用内部放大器,通道1,2电流为6.04mA和4.88mA。对于从5μs到115μs整个过程,IREF从120μA低到5μA, 平均值为52.2μA,通道1电流平均值为53.33mA,通道2电流平均值为53.31mA,通道1的绝对偏差为2.16%,通道2的绝对偏差为2.13%,但通道1和通道2的相对偏差仅为0.019%。

图19 IREF逐渐降低仿真结果Fig.19 Simulation Results with IREF Drop

本仿真结果,在IREF线性变化的过程中,通道1和2的电流也是跟随着线性变化;且 1,2通道轮流使用两个内部放大器,通过时分电路使得彼此之间的相对偏差趋近于零。

3 工艺技术要求

对于本文的分时复用电路,是基于国内常见的模拟CMOS工艺,其选择要注意以下几点:

1)器件的耐压值不低于应用环境,例如本电路的两个内部驱动管MNdrv1和MNdrv2都是选择的高压NMOS,其漏端耐压高达40V。

2)电流采样反馈点电压低于工作电压减去两倍MOSFET阈值电压,例如本电路的反馈点电压设计最大为0.9V左右,远低于 5V电源电压减去两倍NMOS阈值电压。

3)模拟工艺存在相对可靠电阻器件。

4 总结

本文提出一种基于分时复用电路的背光LED驱动电路,经过理论分析和仿真计算验证了该电路的可行性和有效性。对于该电路的总结如下:

1)基于输入可调的运算放大器产生的驱动控制电路,可以线性可调的控制输出电流的大小。

2)采用折叠单极运算放大器和两级源跟随器的反馈环路,可以获得相当高的带宽,从而可以支持高达100kHz的快速切换。

3)采用时分电路的背光LED驱动电路,能明显有效的消除各个通道之间的相对偏差,从而实现大屏幕背光的亮度均匀性。

[1] 方佩敏. LED的发展概况[J]. 今日电子, 2006(8): 37-41.

[2] 吕强,刘金龙. 浅析一种LED调光方式[J].照明工程学报, 2010,21(增刊): 82-84.

[3] 平板电脑分辨率提高直下式LED成长增速{J]. 消费电子, 2012(1): 71.

[4] 李秀真. 超薄液晶电视用LED背光模组的设计[J]. 现代显示, 2010(12): 40-49.

[5] 洪峰,满瑞. 高亮度LED驱动芯片概述[J]. 数字通信, 2011,38(2): 71-74.

[6] 颜重光. 背光及照明用LED驱动IC技术市场分析[J]. 电子产品世界, 2008(10): 39-44.

[7] 程安宁,王晋,尚相荣. 白光LED的PWM驱动方式分析[J]. 电子设计工程, 2010,18(2): 109-111.

[8] 王新. 中大尺寸LCD背光应用的LED驱动方案[J]. 电子产品世界, 2007(1): 97-100.

[9] 贾金萍,张志东. LED背光源亮度均匀性的研究[J]. 现代显示, 2006(4): 19-22.

[10] Brian Law. 针对便携式应用的LED驱动解决方案[J]. 电子产品世界, 2008(3): 131-133.

[11] Huang-Jen Chiu, Shih-Jen Cheng. LED Backlight Driving System for Large-Scale LCD Panels[J]. IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 5, OCTOBER 2007: 2751-2760.

[12] Huang-Jen Chiu, Yu-Kang Lo. A High-Efficiency Dimmable LED Driver for Low-Power Lighting Applications[J]. IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, 2010,57(2): 735-743.

[13] 张普雷,史永胜,史耀华. 大功率背光源用LED驱动电路的研究现状与进展[J]. 液晶与显示, 2010,25(1): 68-74.

[14] 刘波,章小兵. 使用多色LED补色的背光源[J]. 液晶与显示, 2010,25(5): 699-701.

[15] Behzad Razavi. Design of Analog CMOS Integrated Circuit[M]. Singapore: McGraw-Hill Higher Educaion, 2001: 296-305.

[16] 刘敬伟,王刚,马丽. 大尺寸液晶电视用LED背光源的设计与制作[J]. 液晶与显示, 2006,21(5): 539-544.

[17] 乔中莲,杨东升,刘飞. 液晶电视用低功耗LED背光模组设计{J]. 液晶与显示, 2011,26(4): 455-459.

[18] Yuequan Hu, Milan M. Jovanovic. LED Driver With Self-Adaptive Drive Voltage[J]. IEEE TRANSACTIONS ON POWER ELECTRONICS,2008,23(6):3116-3125.