基于3.1 ~10.6 GHz CMOS 超宽带低噪声放大器设计

赵小荣, 范洪辉, 朱明放, 傅中君, 黄海军, 陈鉴富

(江苏理工学院 计算机工程学院,江苏 常州213001)

美国联邦通信委员会(Federal Communications Commission,FCC)于2002 年定义了室内使用的超宽带频段,即3.1 ~10.6 GHz,频带宽度达7.5 GHz[1]。近年来,采用3.1 ~10.6 GHz UWB 技术越来越流行,尤其是在无线通信领域。与现有的无线通信技术相比,UWB 技术具有功耗低,传输速度快、抗干扰性强、低成本、多径衰减鲁棒性和安全性高等优点[2-3],UWB 技术越来越被广泛应用于短距离高速数据传输和军事通信应用中。

作为接收机前端的一个重要组成部分,低噪声放大器的性能直接影响着整个接收机性能。判断设计的UWB LNA 性能好坏,主要是看是否具有足够正向增益,良好的增益平坦度,良好的反向隔离度,稳定度,低电源供电,低功耗,良好的线性度和理想的噪声系数(noise factor,NF)。这些特性要求从不同方面给UWB LNA 设计者提出了挑战[1]。

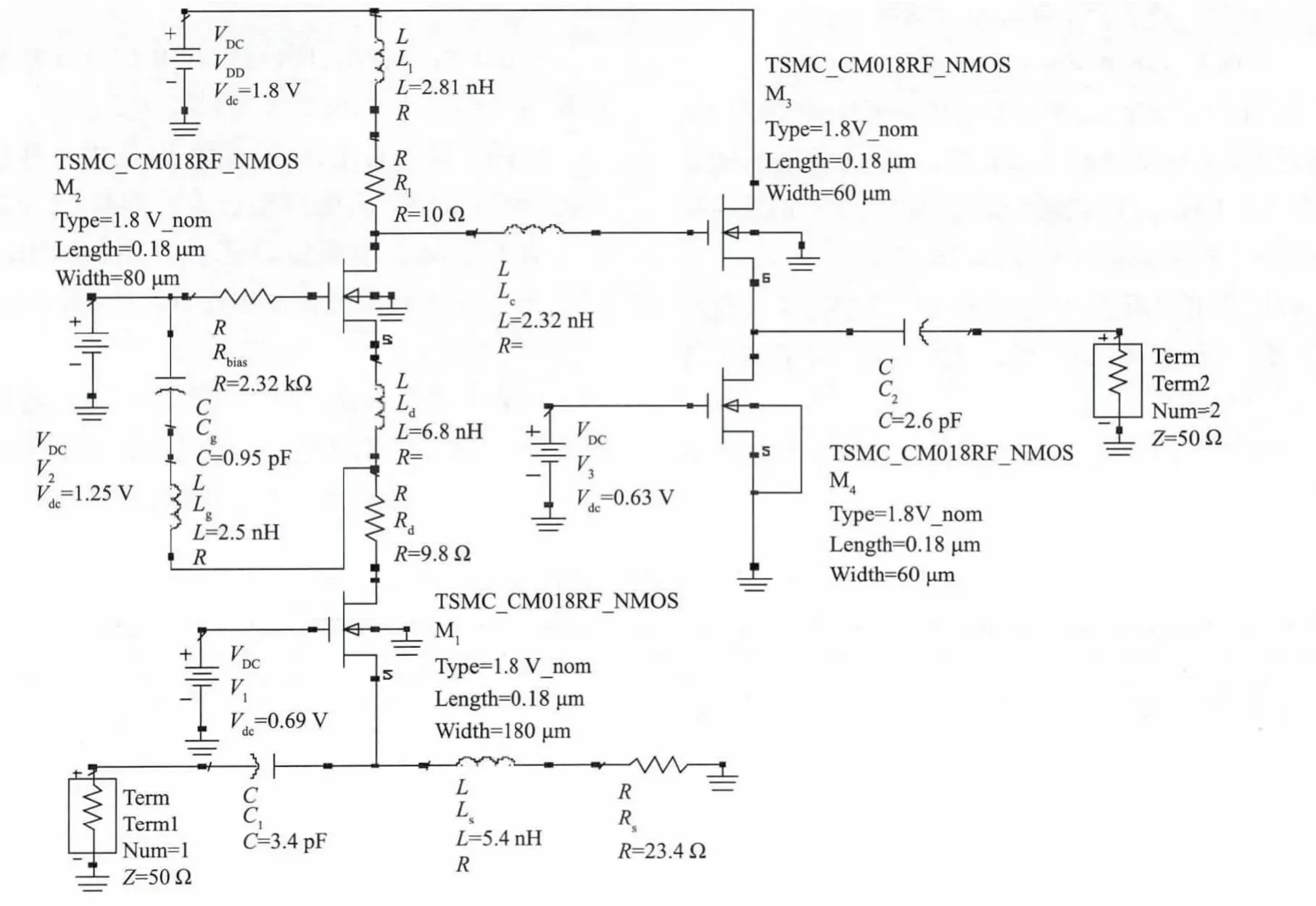

在UWB LNA 设计中,阻抗匹配和噪声匹配设计至关重要。至今,人们已提出了多种CMOS 技术和拓朴结构。如:传统的分布式放大器,负反馈技术,电流复用技术,跨导增强技术,带通滤波器技术等。因为共栅(Common-Gate,CG)结构能够更好地实现阻抗匹配,具有更好的线性度,更小的功耗和比共源结构更好的输入输出隔离度结构,因此CG 结构在UWB LNA 中的应用变得越来越流行。然而,CG结构同样存在电压增益不够和噪声大的缺点。为了解决这一问题,文中设计了一个新的输入匹配电路以降低电路噪声,采用两级放大器形式解决CG 结构电压增益不够的问题,其中电路的第二级采用了共源(Common-Source,CS)结构提高电路的增益。

文中的UWB LNA 输入端采用CG 型拓朴结构,通过电阻、电感和电容实现电路的输入匹配,利用电流复用技术降低整个电路的功率,第二级采用CS型拓朴结构提高电路的增益。本低噪声放大器运用TSMC 0.18 μm CMOS 工艺设计完成。

1 电路设计与分析

1.1 电路分析

接收机的灵敏度主要由LNA 的噪声系数和功率增益决定。LNA 的噪声系数显著地影响了整个接收机的噪声性能。对于多级放大器而言,其噪声系数可以用以下公式表示[4]:

其中:NF 为整个低噪声放大器的噪声系数;NFn为第n 级放大器的噪声系数;G1,G2…Gn-1分别为第1,2 ~n -1 级功率增益。由式(1)可知,多级放大电路的噪声性能主要取决于电路的第一级的噪声系数。所以,在进行电路匹配设计时,第一级的输入匹配设计至关重要。

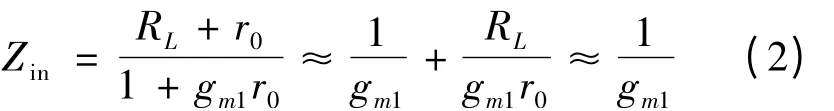

对于CG 结构的放大器而言,由于共栅放大器输入端的阻抗实部为晶体管的跨导倒数,该值在较大的频带范围内可以提供稳定的输入阻抗实部,所以CG 结构在超宽带中得到广泛应用。普通CG 型结构如图1(a)所示,在频率比较高时,晶体管源级进去的输入阻抗Zin可以表示为

式中:gm1为晶体管M1的跨导;r0为晶体管M1的电阻。

通过选择合适的晶体管宽长比和偏置电流设置gm的大小,CG 型结构放大器能够很好地实现与50 Ω 的输入阻抗匹配。CG 结构利用跨导可以实现很宽的输入匹配,但是为了满足良好的阻抗匹配,跨导只能设计为固定值(通常为20 ms)。随着频率的变化,跨导也会变化。CG 型结构低噪声放大器电压增益和噪声系数都会随gm的变化而变化。电压增益与gm成正比,噪声系数与gm成反比。为了减小gm变化对增益和噪声影响,提出了如图1(b)所示电路,同时利用Rs,Ls和Cgs实现输入端的匹配。

图1 共栅拓朴结构Fig.1 Structure of the CG LNA topologies

图2 是图1(b)的小信号等效电路图。

图2 图1(b)电路的小信号等效模型Fig.2 Equivalent small signal model of the circuit in Fig.1(b)

图2(a)可以通过电路的串并联转换变为图2(b),这时电路的输入阻抗可以表示为

其中,Cgs1为晶体管M1的栅源端的等效寄生电容。当Ls= Cgs1时,输入阻抗可以表示为

这样gm1就不再需要固定为20 ms 了,只要Rp值作出适当的调整,便可以降低由于gm1的变化对增益与噪声的影响。从而实现良好的输入匹配,降低第一级的噪声系数。电路可以通过改变Rs的值实现输入回波损耗与电路增益和噪声之间的权衡。

电路的稳定度是设计放大器必须考虑的指标,如果电路不稳定容易形成电路的自激振荡。稳定度是判断放大否稳定的指标,具体可用以下公式表示:当K >1 时,电路无条件稳定。

1.2 电路设计

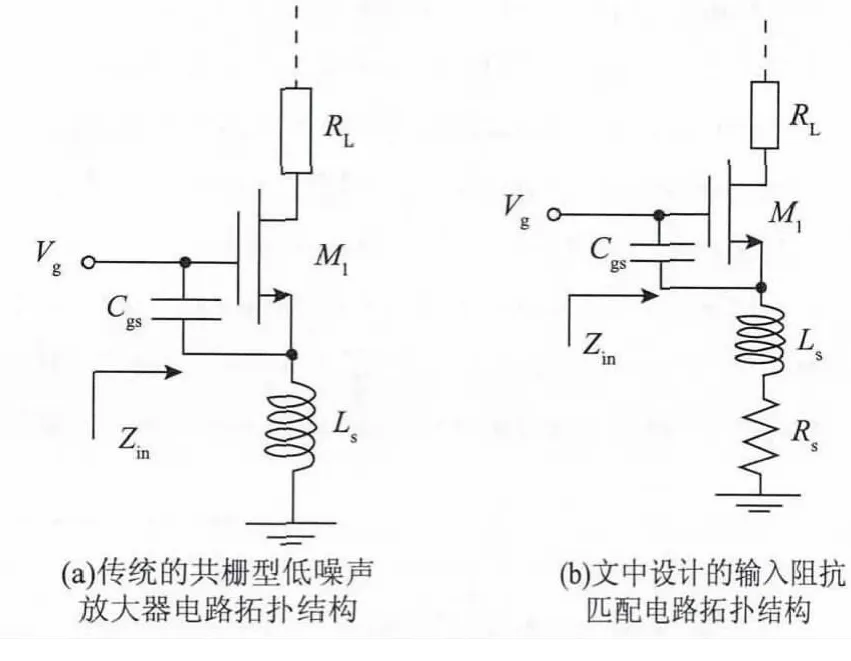

由于单级CG 结构放大器不能提供足够的增益,因此文中所设计的UWB CG-LNA 采用多级结构。UWB LNA 电路如图3 所示。第一级输入端晶体管M1采用CG 输入,通过对LS,RS以及晶体管W/L(可以通过改变W/L 的值实现改变晶体管的跨导)值的设置能很好实现了输入匹配;第二级晶体管M2采用共源(Common-Source,CS)结构实现了增益的提高。电感Ld和Lg、电容Cg和电阻Rd实现了CG 级与CS 级之间级间匹配。另外电容Cg作为理想的耦合电容可以降低级间噪声,通过加入RL,LL和LC可以提高第二级CS 电路的增益。当电感Ld、晶体管M1的寄生电容与晶体管的源极在3.1 GHz 时产生并联谐振,电感LC和晶体管M3的栅源电容Cgs3在10.6 GHz 产生谐振时,放大器可以在3.1 ~10.6 GHz 频带内保持理想的增益平坦度。晶体管M1和M2之间采用了电流复用技术,大幅度降低电路功耗。

图3 UWB LNA 电路Fig.3 Schematic of the proposed UWB LNA

2 仿真结果与分析

文中设计UWB LNA 采用TSMC 0.18μm RF CMOS 工艺完成,电路通过ADS2009 仿真,S21与S12的仿真曲线如图4 所示,S11与S22的仿真曲线如图5所示。

图4 S21 与S12 仿真曲线Fig.4 Simulation curves of S21 and S12

图5 S11 与S22 仿真曲线Fig.5 Simulation curves of S11 and S22

由图4 可以看出,在3.1 ~10.6 GHz 频带内,正向增益S21达到20.951 ~23.951 dB,增益平坦度良好,在3.1 GHz 时达到最大增益为23.951 dB;反向隔离度S12在带内低于-44.436 dB。

由图5 可以看出,电路在整个带宽内,输入返回损 耗 小 于 - 15.14 dB, 输 出 返 回 损 耗 低于-20.202 dB。

图6 为电路稳定度的仿真曲线,图7 为电路噪声的仿真曲线。

图6 电路稳定度仿真曲线Fig.6 Simulation curves of stable factor

图7 电路噪声仿真曲线Fig.7 Simulation curves of noise factor

由图6 可以看出,所设计UWB LNA 在整个带宽内稳定度都大于1,电路无条件稳定。

由图7 可以看出,通过优化设计,电路在整个频带内噪声性能良好,噪声系数为0.944 ~1.625 dB。

表1 给出文中所设计3.1 ~10.6 GHz UWB LNA 与近几年所发表论文中设计的UWB LNA 性能的比较。

由表1 可以看出,文中实现的LNA 增益比其他的LNA 更高,NF 比其他的LNA 更低,其他性能也可以和别的LNA 相比拟,但功率消耗有点高。

表1 3.1 ~10.6 GHz CMOS UWB LNA 的性能比较Tab.1 Comparison between the design used in this study and others reported based on 3.1 ~10.6 GHz in literature

3 结 语

文中所设计的3.1 ~10.6 GHz 的UWB LNA 由两级拓扑结构组成,在电路第一级采用了共栅型结构完成宽带输入匹配。为了改进共栅型放大器的噪声系数,提出了在常用共栅放大器源极加入串联电阻与电感,从而通过改变串联电阻值的大小改变放大器的输入回波损耗和噪声系数的值。利用电流复用技术降低了整个电路的消耗功率,通过共源共栅结构和良好的级间匹配电路设计改善了共栅结构带来的增益不足的缺点。实验结果表明,电路在1.8 V 供电下,整个电路消耗功率在15.6 mW 左右,在3.1 ~10.6 GHz 的频带内增益S21= 21.451 ±1.5 dB,噪声系数NF 为1.284 5 ±0.340 5 dB,输入回波损耗均低于- 15.14 dB,输出回波损耗低于-20.202 dB。这些性能可以和其他已发表的CMOS UWB LNA 相比拟,同时为UWB LNA 提供了一种新的选择。

[1]王春华,戴普兴,杨凯.3.1 ~10.6 GHz CMOS 超宽带低噪声放大器设计[J].电路与系统学报,2010,15(1):71-76.

WANG Chunhua,DAI Puxing,YANG Kai.3.1 ~10.6 GHz CMOS Ultra-wideband low noise amplifier[J].Journal of Circuits and Systems,2010,15(1):71-76.(in Chinese)

[2]何小威,李晋文,张民选.1.5 ~6 GHz 增益和噪声系数稳定的两级超宽带CMOS 低噪声放大器设计与性能模拟[J].电子学报,2010,38(7):1668-1672.

HE Xiaowei,LI Jinwen,ZHANG Minxuan.Design and performance simulation of a 1.5 ~6 GHz two-stage UWB CMOS LNA with extra flat gain and NF[J].Acta Electronica Sinica,2010,38(7):1668-1672.(in Chinese)

[3]KAO H L,Changa K C.Very low-power CMOS LNA for UWB wireless receivers using current-reused topology[J].IEEE Solid State Electronics,2008,52(1):86-90.

[4]丁春宝,张万荣,谢红云,等.3 ~6 GHz SiGe HBT Cascode 低噪声放大器的设计[J]. 北京工业大学学报,2012,38(8):1162-1166.

DING Chunbao,ZHANG Wanrong,XIE Hongyun,et al.Design of 3 ~6 GHz SiGe HBT cascode low noise amplifier[J].Journal of Beijing University of Technology,2012,38(8):1162-1166.(in Chinese)

[5]Shim J,YANG Taejun,Jeong J.Design of low power CMOS ultra wide band low noise amplifier using noise canceling technique[J].Microelectronics Journal,2013,44(9):821-826.

[6]WAN Qiuzhen,WANG Chunhua. Design of 3. 1 ~10. 6 GHz ultra-wideband CMOS low noise amplifier with current reuse technique[J].AEU-Int J Elect Commun,2011,65(11):1006-1011.

[7]张滨,杨银堂,李跃进.一种3.1 ~10.6 GHz 超宽带低噪声放大器设计[J].微波学报,2012,28(1):49-52.

ZHANG Bin,YANG Yintang,LI Yuejin. Design of a 3. 1 ~10. 6 GHz ultra wideband low noise amplifier[J]. Journal of Microwaves,2012,28(1):49-52.(in Chinese)

[8]Hosein Alavi-Rad,Soheyil Ziabakhsh,Mustapha C E Yagoub.A 1.2 V CMOS Common-Gate low noise amplifier for UWB wireless communication[J].Journal of Circuits,Systems,and Computers,2013,22(7):27-37.

- 服装学报的其它文章

- 非自治F-N 系统在带参数的空间中全局吸引子的存在性