基于PCI总线的四通道CAN通讯卡的设计

王海霞

(天津外国语大学 国际传媒学院,天津 300270)

PCI总线(peripheral component interconnect)俗称外部部件互联总线,是由美国Intel公司率先提出的一种先进的高性能局部总线,不依附于某个具体的处理器。比起ISA、EISA和MC等标准总线,更能满足人们对微机系统I/O带宽的要求。PCI总线的时钟频率为0~33 MHz,其最大数据传输速率可达到528 Mbps,PCI局部总线的引入,打破了数据传输的瓶颈,使数据的实时高速采集和传输成为可能[1]。CAN总线是一种全数字化、双向和多主的现场总线,具有通信速率高、容易实现、且性价比高等优点,应用广泛。

1 CAN通讯卡的设计原理

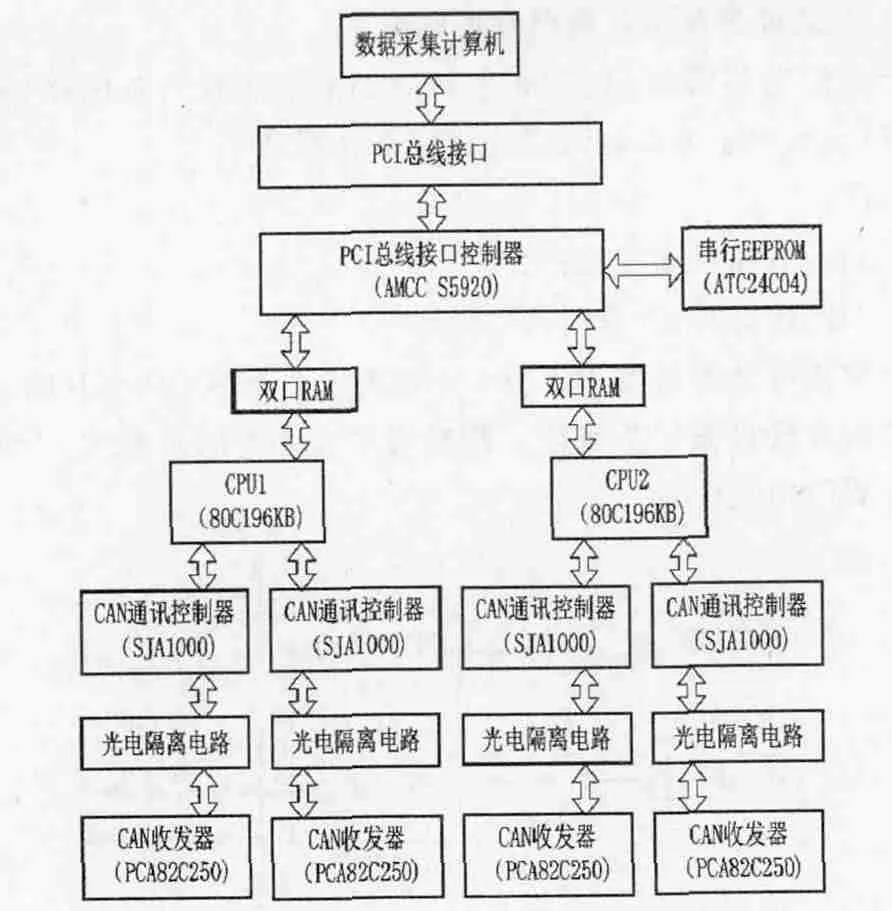

四通道CAN通讯卡介于核电现场I/O模块和主站之间,是一块基于PCI总线的高速数据采集卡。一块通讯卡上有4个CAN通道,每个CAN通道连接32个单通道I/O模块。每隔25ms采集I/O模块的数据一次,通过CAN通讯接口传送到微控制器80C196KB,经过处理后再通过8K*8的双口RAM经由PCI总线控制器上传给主机。主机对I/O模块的初始化、对时等操作由80C196KB通过CAN通讯下传到单通道I/O模块。其具体的逻辑框图如图1所示。

根据核电站试验数据采集系统的设计规范,该系统的数据采集总量为400个模拟量和112个开关量。每个采集模块采集一个点,因而共有512个采集模块,这些采集模块分布在两个机柜中。所有这些采集模块的数据都是通过CAN总线分别传送到数据采集柜中的两台数据采集计算机,进行量程转换和相关处理,送到数据处理计算机。每台数据采集计算机上有2块4通道智能CAN总线通讯卡,即8条CAN总线通道,分别将两个机柜的采集信号转到数据采集计算机上进行处理,因而每根CAN总线传送32个采集模块的数据。

鉴于四通道CAN通讯卡的数据采集功能,该卡的工作流程是:CPU每隔25 ms(最小巡检周期)扫描四条CAN总线上的128个采集模块的数据,经过处理后送给PCI总线,最后到达数据采集计算机。

由于CAN卡的数据采集量比较大,根据扫描周期,对CPU而言,每秒钟由CAN总线控制器产生的中断有32*4*1 000/25=5 120个,则每个中断之间的间隔为1 000 000/5120=195.3μs。这对于CPU提出了很高的要求。如采用一个80C196KB,由于其单指令周期为0.125μs,假设每个中断服务指令需300条汇编指令,平均每条汇编需两个单指令周期,即0.25μs,则每个中断服务程序需300*0.25=75μs,占用这个中断间隔的75/195.3=38.4%。这些数据表明即使处理速度满足要求,CPU的资源也是比较紧张的。若采用两个80C196KB,则每个CPU处理的中断为5 120/2=2 560,每个中断之间的间隔195.3*2=390.6μs,每个中断服务程序时间占用这个中断间隔的75/390.6=19.2%,这对每个CPU而言,就轻松多了。

图1 四通道CAN通讯卡逻辑框图Fig.1 The logic diagram of four channel CANcommunication card

根据上述分析,决定采用两个CPU(分别称为CPU和从CPU)。从CPU只负责采集两个CAN通道数据,通过双口RAM向主CPU发送采集的数据。主CPU不仅负责采集两个CAN通道数据,还负责和PCI总线接口,将从CPU采集的数据和自身采集的数据一起向PCI总线传输。同时,主CPU接收到PCI总线上的命令字和数据后,还需通过双口RAM将它们传送给从CPU,以确保主、从CPU进行数据采集的一致性和完整性。

2 芯片介绍

2.1 PCI总线控制器

PCI总线控制器采用AMCC公司的S5920,S5920是符合PCI2.2规范的从方式接口控制器,他只能工作于从方式(slave)。Add-On 侧有两种工作方式:邮箱方式(MAILBOX)和直通方式 (PASS-THRU)方式。PASS-THRU方式又分PASSIVE和ACTIVE方式。根据各种方式的侧重点不同,我们采用PASS-THRU的ACTIVE方式。它操作简单,对时序要求较少,比较适合大量数据的传输。四通道CAN通讯卡的资源申请采用非易失性 RAM (NVRAM)---------串行EEPROM AT24C04来实现。

2.2 CPU

采用Intel的16位微控制器80C196KB,它是Intel公司性能最强的CMOS芯片,其片内集成有8路A/D转换器,包括一个8通道多路模拟开关,采样保持电路和10位A/D转换器。与96系列微控制器相兼容,并增加了许多新功能。具有高速I/O子系统、中断源及中断向量显著增加(28个中断源,18个中断向量)[2],可动态配置8位或16位总线宽度。

2.3 双口RAM

接口卡含有板级CPU总线和主站ISA总线。两条总线通过8K*8的双口RAM交换数据。通过双口RAM,主站直接控制接口卡、并与其交换静态数据,主站和接口卡协调的依据是邮箱命令[3]。双口RAM的详细内存地址分配如表1所示。

表1 双口RAM数据区分配表Tab.1 Data area distribution table of dual port RAM

2.4 CAN通讯接口

CAN控制线采用Philips公司的SJA1000,它与PCA82C200管脚兼容。具有扩展的接收缓冲器,64字节的FIFO结构,支持CAN2.0B协议。24 MHz晶振频率下,传输速率高达1 Mbits/s。其内部结构如图2所示。物理传输层采用EIA RS485,故采用高速光电隔离器件HCPL0611,保证电气上无干扰,隔离电压达到500 V以上,提高整个系统的测量精度。收发器采用Philips公司的PCA82C250芯片,其可以提供对总线数据的差动发送能力和对通信总线数据的差动接收能力。

2.5 译码电路

译码电路采用ALTERA公司的EPM7128SCPLD。它具有高阻抗、电可擦等特点,可用门单元为2 500个,管脚间最大延迟5 ns,工作电压5 V,输入输出线数84,并且它集逻辑译码、总线接口等于一体,十分方便。图3为EPM7128S的功能逻辑框图,其与PCI总线的连接示意图如图4所示。

图2 SJA1000内部结构Fig.2 Internal structure of SJA1000

图3 EPM7128S的功能逻辑框图Fig.3 Functional logic diagram of EPM7128S

2.6 微处理器监控故障自复位电路

复位电路采用MAXIM公司的MAX823看门狗电路,如图5所示,以它为核心可以完成以下几项功

能:

1)上电和手动复位;

2)监视定时器(看门狗)复位。

单排两针跨接器JP3、JP4分别用于2个80C196KB的电源监控和硬件看门狗复位。跨接表示允许看门狗复位,否则禁止看门狗复位。

图5 看门狗电路Fig.5 Circuit of guard dog

3 CAN通讯卡的PCB设计

在设计PCB时,我们采用Mentor Graphics公司的PADS2005软件,它包括整个完整的PCB设计过程,涵盖了从原理图网表导入,规则驱动下的交互式布局布线,DRC/DFT/DFM检查与分析,直至最终Gerber生产文件、装配及物料清单输出等全方位的功能需求[4]。良好的PCB设计不仅可以增加PCB的视觉美感,更能提高系统的抗干扰能力。在数据采集卡的PCB制作中,要考虑插卡的高频性能、电源去耦与干扰的抑制、接地方式的选择等因素。

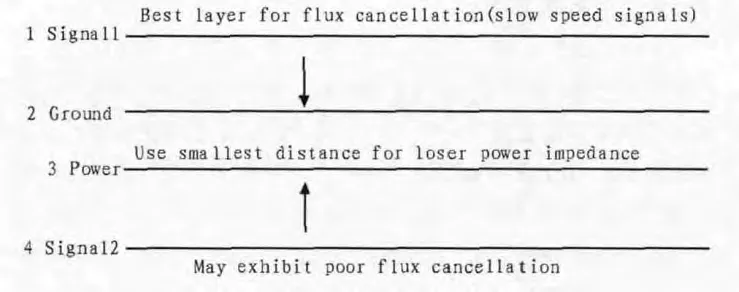

3.1 PCB层数的选择

在制作PCI板卡时,选择制作四层的PCB板,其堆叠方式如图6所示,这样因使用了Power及Ground平面层,EMI之特性有很大改善。

图6 四层板堆叠方式Fig.6 Stacked way of four layer board

3.2 去耦电容

由于一些高速信号,噪声频率比较高,我们采用0.1μF的电容作为去耦电容,并使之尽量靠近IC的电源地管脚,使其与电源和地之间形成的回路最短。对于从外部连接器进来的信号线使用的旁路电容,要靠近连接器放置,以减小外部连接线可能引入的干扰在板上传播。

3.3 电源设计

为了防止数字器件所带来的高频噪声对模拟器件造成影响,将模拟信号的地与数字信号的地的走线分开,然后在PCB上找一个适当的位置将两者单点连通。系统的模拟地和数字地的共地点一般选择ADC芯片上引脚所需电流最大的地方,以便使大电流对地回流路径最短,减少对模拟电路的电磁干扰,提高系统精度[5]。因为快速的数字振荡可能将转换噪声祸合到模拟电源中,所以模拟电源和数字电源应该分开供电。在数据采集卡的设计中,模拟电路直接由DC一DC隔离电源供电,数字电源直接由PCI插槽中的+5 V和+3.3 V供电[6-8]。

3.4 走线要求

PCI总线的32位部分的所有信号最大走线长度必须限定在1 500 mil以内,PCI时钟信号线的长度必须是2 500 mil(±100 mil),并且只能和插卡上的一个负载连接。该引线只能在PCB一面走线且在转角处用弧形,切忌用直角,锐角,可用“蛇”形走线来满足长度要求[6]。

另外,对于电源线和地线的线宽,通常是地线比电源线窄,即:信号线<电源线<地线,信号线宽通常为:0.2~0.3 mm,电源线为1.2~2.5 mm。地线尽量采用大面积覆铜的方式来增大地线面积减小接地阻抗,提高电路板的抗干扰能力。

3.5 时钟信号的保护

为了满足高速数字信号的要求,PCB布线要求满足尽量减少传输延迟、减少信号损耗等。数据采集板上PCI时钟信号和AD采样、锁存、FIFO的读和写这些频率较高的时钟信号,应在PCB布线时在两边设置地线加以保护。

4 结束语

使用基于PCI总线的高速数据采集卡是现代信号处理中实现实时数据进机存储的重要方法。本方法所设计实现的数据采集系统也可应用于通信振动工程、语音处理、工业自动控制以及生物医学工程领域。目前我国的数字化仪控系统还处于初级阶段,核电站数字化仪控系统的国产化是我国核电仪控事业发展的必由之路。该高速数据采集卡将应用在岭澳核电站BOPLOT KDO/KME项目中,完成现场I/O模块和控制站之间的数据传输,每隔25 ms采集一次数据,实现了高速度和低成本的优点。

[1]裴喜龙.基于PCI总线的高速数据采集卡系统设计与实现[J].微计算机信息,2006,22(7-1):129-131.PEI Xi-long.Design and implement of a high speed data acquisition card based on PCI Bus[J].Microcomputer Information,2006,22(7-1):129-131.

[2]黄瑶,余祖俊,赵爱菊.以80C196KB的一个数据采集分析仪[J].北方交通大学学报,1996,20(4):502-507.HUANG Yao,YU Zu-jun,ZHAO Ai-ju.A data acquisition analyzer based on 80C196KB[J].Journal of Northern Jiao tong University,1996,20(4):502-507.

[3]王海鹏.分布式控制系统PROFIBUS-DP总线主卡的设计[D].天津,南开大学,2004.

[4]王纪睿.印刷线路板焊盘和金手指自动光学检测研究[D].武汉,华中科技大学,2012.

[5]孙波.基于PCI总线的高速数据采集卡的设计[D].成都,电子科技大学,2007.

[6]闫雷兵,田丰庆.基于PCI总线的数据采集卡设计[J].河南科技学院学报,2010,38(1):74-77.YAN Lei-bing,TIAN Qing-feng.Design of a data acquisition card based on PCI Bus[J].Journal of Henan Institute of Science and Technology,2010,38(1):74-77.

[7]温彤,施伟锋,张威,等.基于现场总线的微型电网监视装置设计[J].陕西电力,2013(10):52-56.WENG Tong,SHI Wei-feng,ZHANG Wei,et al.Micro-grid monitoring device based on field bus[J].Shaanxi Electric Power,2013(10):52-56.

[8]李志坚,莫建麟.一种改进的基于概念格的数据挖掘算法[J].重庆师范大学学报:自然科学版,2014(4):92-95.LI Zhi-jian,MO Jian-lin.An improved concept lattice-based data mining algorithm [J].Journal of Chongqing Normal University:Natural Science,2014(4):92-95