GaN器件的LLC谐振变换器的优化设计

马 焕,王康平,杨 旭,甘永梅

(西安交通大学电气工程学院,西安710049)

GaN器件的LLC谐振变换器的优化设计

马 焕,王康平,杨 旭,甘永梅

(西安交通大学电气工程学院,西安710049)

首先介绍了LLC谐振变换器的工作原理,详细分析了基于增强型氮化镓(eGaN)场效应晶体管的LLC谐振变换器的开关过程。分析结果表明,通过调节死区时间可以避免GaN晶体管的反向导通,从而减小损耗;通过减小高频功率回路电感可以减小功率回路的振荡。再对死区时间和功率回路布线分别进行了优化,由于GaN晶体管栅源电压安全裕量很小,为确保器件安全,对驱动回路布线进行优化;最后设计了1台输入电压为48 V、输出电压为12 V、输出功率为100 W、开关频率为1 MHz的LLC实验样机,并进行了实验验证。实验结果表明,高频功率回路电感从5.6 nH降为0.4 nH时,下管关断时的漏源电压超调由15%下降到6.7%,另外驱动功率回路采用单层布线带屏蔽层的布线方式后,开关管的驱动电压几乎没有振荡。

LLC;氮化镓器件;死区时间;寄生电感;布线

引言

高效率、高功率密度是DC/DC电源一直追求的目标。提高开关频率可以有效减小无源器件的尺寸,从而提高功率密度[1]。然而提高开关频率会增加开关损耗,降低效率。LLC谐振变换器的出现有效地改善了这一问题,LLC可以实现原边开关管的零电压开通ZVS(zero voltage switch)以及副边二极管的零电流关断ZCS(zero current switch),减小了开关损耗。另外,LLC电路可以将漏感集成在变压器中,很大程度上减小了电源的体积和尺寸,实现高功率密度[2-6]。

本文选用增强型氮化镓eGaN(enhancementmode Gallium Nitride)场效应晶体管作为LLC的开关管,eGaN FET是近几年出现并逐步商业化的热门新材料器件[7]。相比于硅MOSFET,GaN晶体管有开关速度快、尺寸小、无反向恢复等优点,用GaN晶体管替换硅MOSFET可以大幅度提升开关频率,同时保持了良好的效率指标,具有很好的发展趋势[8-9]。将其应用到POL(point of load)、DC/DC等低压、小功率的电源装置中,可以极大地提高这些领域电源装置在功率密度、效率等方面的性能[10]。

然而GaN晶体管也存在一些应用难点。首先,GaN晶体管反向导通时的导通压降比硅MOSFET大,相比于硅MOSFET会产生更大的损耗[8,11-12];其次,由于功率回路中不可避免地存在寄生电感,当电流迅速变化时,在开关器件两端会产生很高的尖峰过电压,造成电路误动作、EMI超标,甚至器件击穿损坏。另外,GaN晶体管栅极能承受的极限电压只有6 V,而栅极电压在4.5~5.5 V时才能使器件的通态沟道电阻降到满意的范围,可见其噪声容限仅有1 V左右。GaN晶体管在这方面产生的影响比硅MOSFET明显,因此更应减小其高频功率回路电感及驱动回路电感,改善功率回路和驱动回路的振荡问题[13]。因此,结合GaN晶体管的这些特点,对LLC电路进行优化是很有必要的。

本文首先分析了LLC的工作原理,详细分析了LLC的开关过程,然后对死区时间、功率回路布线和驱动回路布线分别进行了优化,最后搭建了48 V/12 V、100 W、1 MHz的LLC硬件电路,进行了实验验证。

1 LLC的基本原理

LLC的主电路拓扑见图1,变压器初级侧由2个开关管构成半桥结构,次级侧为全波整流,变压器带中心抽头。

图1 LLC谐振变换器Fig.1 LLC resonant converter

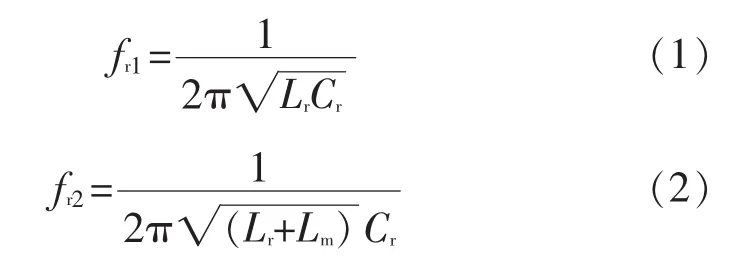

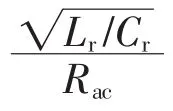

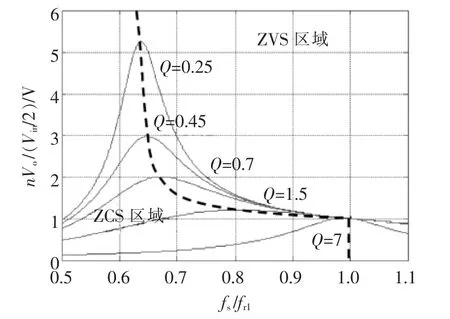

LLC共有3个谐振元件:谐振电感Lr、励磁电感Lm和谐振电容Cr,存在2个谐振频率fr1和fr2,其表达式分别为

图2 LLC谐振变换器的直流增益特性Fig.2 DC gain characteristic of LLC resonant converter

本文电路额定工作点设计在 fs=fr1处,此时GaN晶体管可在全负载范围内实现 ZVS,同时又可保证变压器副边二极管的ZCS,减小了开关损耗。

2 基于GaN晶体管的LLC开关过程的分析

GaN晶体管与硅MOSFET的开关特性相似,只是在反向导通时有些区别。当硅MOSFET在关断期间承受的反压达到体二极管导通的压降时,其体二极管导通。GaN晶体管有一个自身的特点:其栅源电压Vgs或栅漏电压Vgd高于阈值电压Vth时,GaN晶体管均可导通。当GaN晶体管漏源极开始承受反向电压,栅源电压Vgs为0(未加驱动)时,栅漏电压Vgd与源漏电压Vsd相等。当漏源电压Vsd上升到Vth时,GaN晶体管反向导通。当反向电流为0 A时反向导通压降为1.4 V,反向电流为20 A时导通压降为2.2 V,其反向导通压降较硅MOSFET大很多。

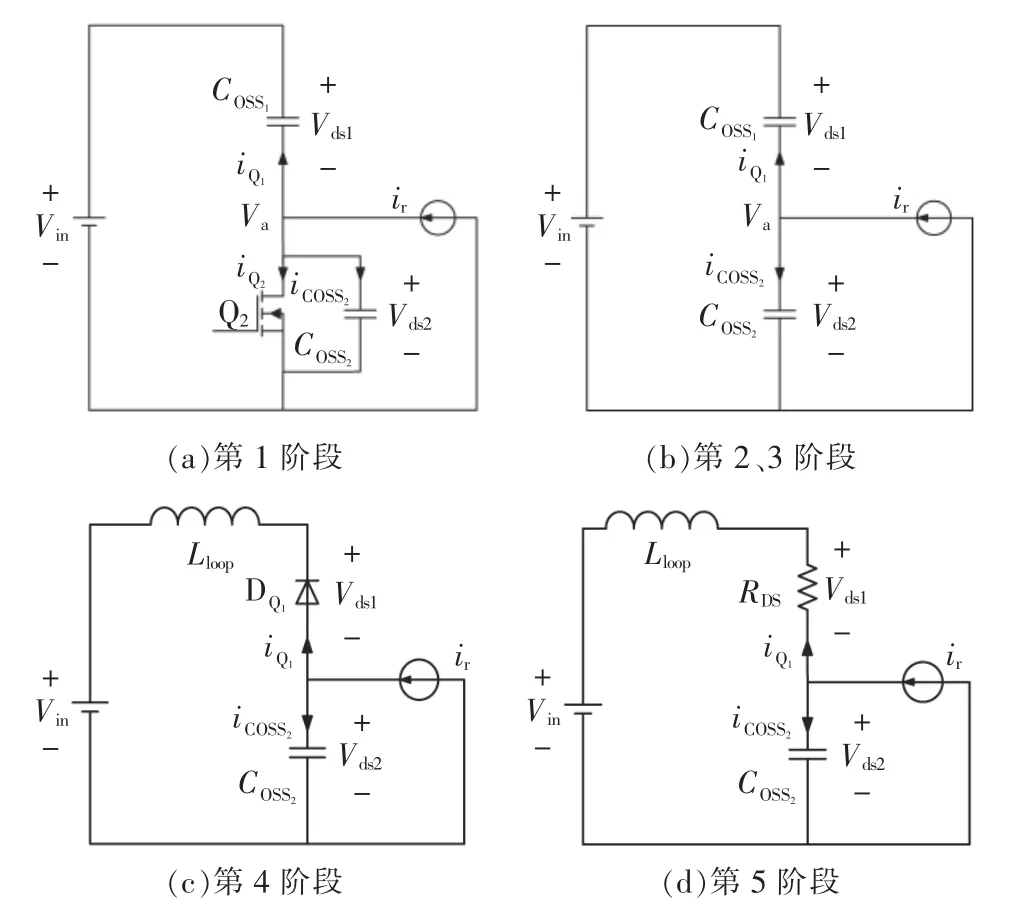

LLC电路可以实现ZVS,在器件开通时没有损耗和振荡,开通损耗可以忽略不计,本文重点分析开关管的关断过程。由于上管和下管的关断过程是一样的,本文以下管为例详细分析其关断过程,其等效简化电路见图3。因流过谐振电感的电流在开关瞬态变化很小,所以可等效为恒定电流源ir。其中分别为2个GaN晶体管的输出电容,Lloop为高频功率回路电感,其包括器件的封装电感、PCB布线电感、母线电容的等效串联电感。

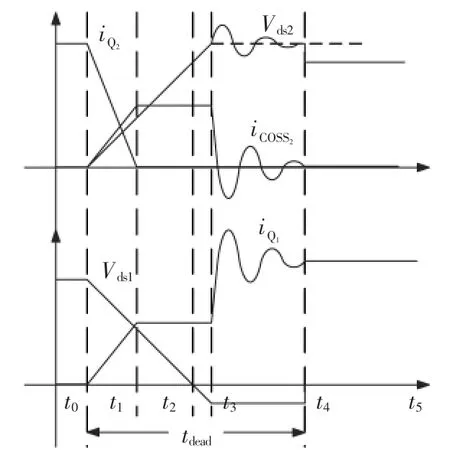

LLC的开关过程波形如图4所示,LLC下管关断过程可以分为5个阶段:

第1阶段(t0~t1):t0时刻,Q2的沟道电流iQ2在驱动电压Vgs2的作用下开始下降,同时中点电位Va(即Q2的漏源电压Vds2)开始上升,则流过的电流分别为

此阶段直到沟道电流iQ2下降到0时结束,等效简化电路见图5(a)。

第2阶段(t1~t2):这段时间内沟道电流iQ2已下降到0,谐振电流ir只流过和,Vds1继续下降,Vds2继续上升,此阶段直到Vds1下降到0结束,等效简化电路图见图5(b)。

第3阶段(t2~t3):谐振电流ir继续对充放电,Vds1反向增加。当Vds1反向增加到阈值电压Vth时,Q1反向导通。

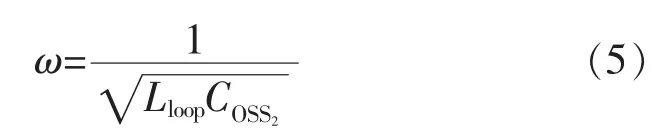

第4阶段(t3~t4):t3时刻Q1反向导通,其等效简化电路见图5(c),高频功率回路电感Lloop与COSS2构成二阶振荡电路,电流和电压Vds2出现振荡,则振荡频率为

第5阶段(t4~t5):t3时刻给Q1加驱动电压,Q1的沟道电阻RDS减小,Vds1由反向导通压降VD减小到RDSIr,而Vds2下降到Vin+RDSIr。等效简化电路见图5(d)。

图3 等效简化电路Fig.3 Equivalent simplified circuit

图4 开关过程的波形Fig.4 Waveforms of switching process

图5 不同阶段的等效电路Fig.5 Equivalent circuits for different stages

3 LLC的优化设计

3.1 死区时间的优化

从以上开关过程的分析中可以看出,开关管Q1的漏源电压在下降到0之后继续反向增加,直到给Q1加驱动电压后才重新降为0。GaN晶体管因反向导通压降较硅MOSFET大,这段时间内损耗较大,因此需对死区时间进行优化。优化死区时间一般的做法会在开关管的漏源电压降为0以后给开关管施加驱动电压,以防直通。本文中调节死区时间强调的是在开关管的漏源电压降为零时使开关管的沟道导通,从开关过程的详细分析中看出,不会存在直通现象,并且可以避免Q1的反向导通。

3.2 功率回路电感的优化

从以上开关过程的分析中可以看出,高频功率回路电感与Q2的输出电容构成二阶振荡电路,Q2漏源电压出现寄生振荡和过电压。Lloop越大,造成功率回路的寄生振荡越严重。对上下管开关过程中寄生振荡的影响类似。因此采用具有较低高频功率回路电感的功率回路布局与布线方式是很有必要的。

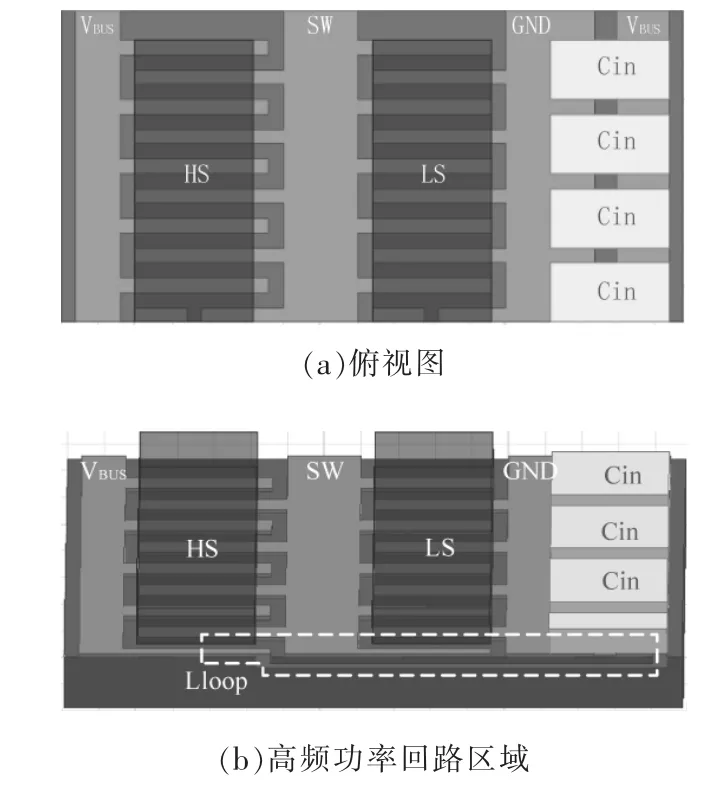

本文所使用的功率回路布局与布线方式如图6[13]所示,2个GaN晶体管以及输入电容均位于PCB的同一面,4个输入电容并联放置在2个开关管的一侧,其高频功率回路电感Lloop=0.4 nH。

图6 功率回路布局与布线Fig.6 Layout of power loop

3.3 驱动回路电感的优化

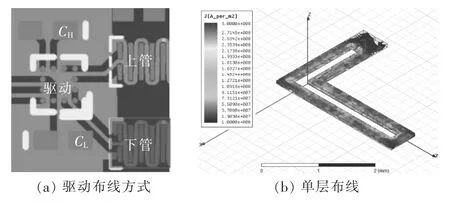

GaN晶体管栅极能承受的极限电压只有6 V,而栅极电压在4.5~5.5 V之间时才能使器件的通态沟道电阻降到满意的范围,其噪声容限仅有1 V左右。因此需减小驱动回路电感,从而降低驱动回路的电压振荡,防止器件击穿,提高器件的可靠性。本文比较了以下2种不同的驱动回路布线方式:(1)单层布线方式:尽可能地减小回路的导线长度以及其所包围的面积;(2)单层布线带屏蔽层方式:在一个回路的正下方放置一个完整的良导体平面,利用屏蔽层的去磁作用减小回路的等效电感。屏蔽层越靠近回路去磁效果越好。

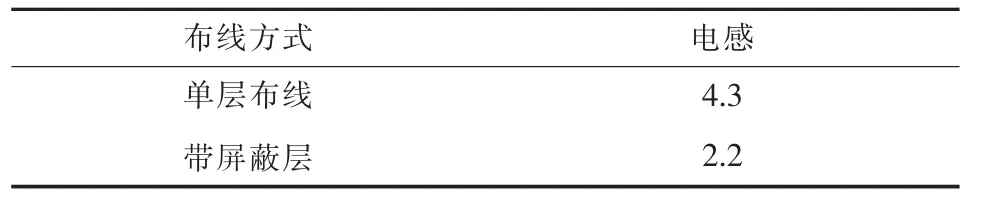

本文通过电磁仿真软件Maxwell对各布线方式进行了比较,不同驱动布线方式下的电流密度分布见图7,各驱动布线方式下的等效电感值如表1所示。由表可知,单层布线带屏蔽层方式较单层布线方可以明显降低驱动回路电感。因此本文驱动回路布线采用单层布线带屏蔽层方式。

图7 不同驱动布线方式下的电流密度分布Fig.7 Current density distributions with different driving loops

表1 不同驱动布线方式下的电感仿真结果Tab.1 Simulation inductances with different driving loops nH

4 实验验证

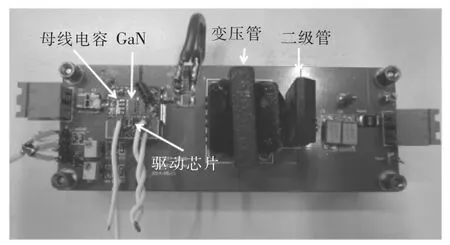

本文搭建了1个48 V/12 V、100 W、1 MHz的LLC硬件电路,GaN晶体管型号选用EPC2001,驱动芯片型号为LM5113,二极管型号为MBR4060PT。驱动芯片和GaN晶体管之间未加驱动电阻。图8为实验所搭建的实验样机,在此硬件平台上分别对死区时间与功率回路电感优化进行了验证。

图8 LLC实验样机Fig.8 Experimental prototype of LLC resonant converter

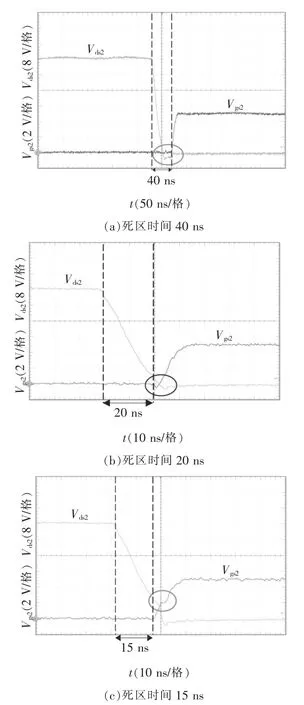

本文通过调节死区时间,使得器件的漏源电压Vds在下降到0时器件的沟道导通。死区时间为40 ns、20 ns和15 ns时的实验波形如图9所示,其中Vds2、Vgs2分别为下管的漏源电压和驱动电压。由图可以看出,图9(a)中下管存在反向导通,将产生额外的反向导通损耗;图9(c)中驱动电压出现密勒平台,说明开关管未完全实现ZVS;图9(b)中在Vds2为0时使得Q2沟道导通,既保证了Q2的完全ZVS开通,又最大限度地避免了GaN的反向导通,是最优化的情况。

图9 不同死区时间的实验波形Fig.9 Experimental waveforms with different dead time

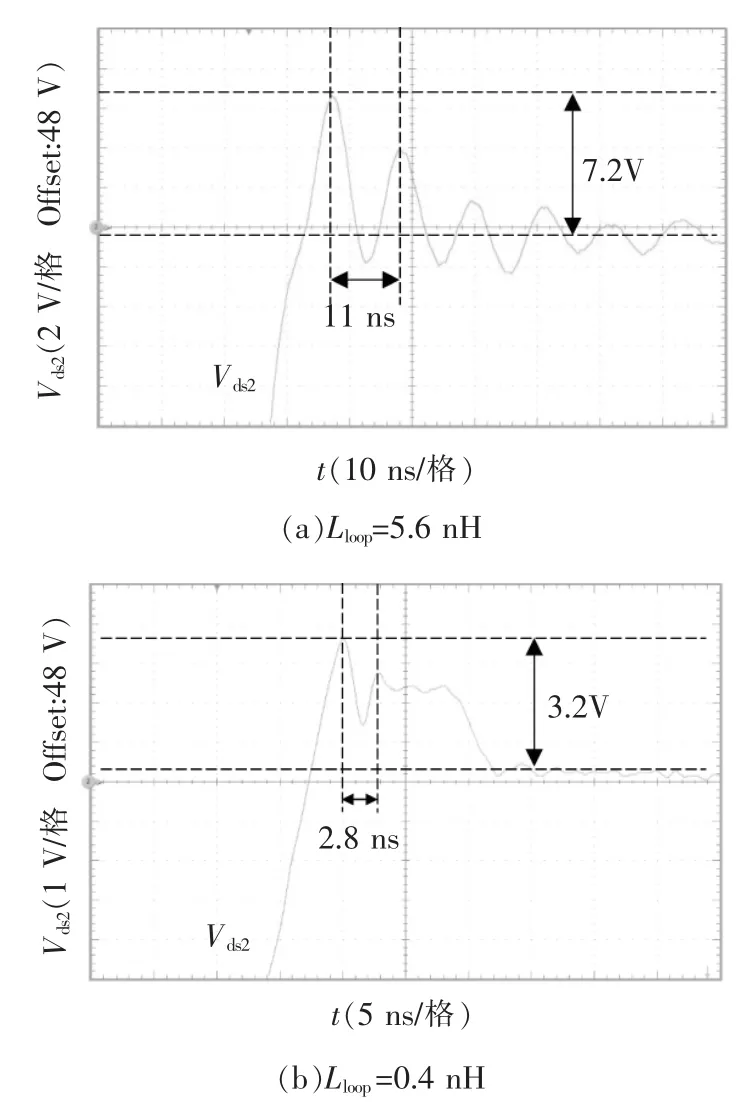

图10为高频功率回路电感为5.6 nH和0.4 nH的功率回路电压波形。从图中可以看出,当高频功率回路电感由5.6 nH降为0.4 nH时,下管关断时的漏源级过电压由7.2 V降为3.2 V,超调由15%下降到6.7%。说明通过优化布局和布线可以减小高频功率回路电感,从而可以减小过电压和振荡。

图11为下管的驱动电压波形,从图11中可以看出下管的驱动电压几乎没有振荡。说明本文所采用的驱动回路布线方式可以有效地减小驱动回路电感,从而减小器件栅源间过电压,提高器件的可靠性。

图10 不同高频功率回路电感的Vds2波形Fig.10 Waveforms of Vds2with different high power loop inductances

图11 Vgs2波形Fig.11 Waveform of Vgs2

5 结语

本文结合GaN晶体管的特点详细分析了LLC谐振变换器的开关过程,对LLC电路的死区时间和功率回路布线以及驱动回路布线进行了优化。最后搭建了48 V/12 V,100 W,1 MHz的LLC实验样机。通过调节死区时间,在器件的漏源电压下降到0时使器件的沟道导通,避免器件的反向导通,可以最大限度地降低反向导通损耗;同时通过实验验证了本文所采用的功率回路布局与布线方式具有较小的高频功率回路电感,功率回路电压振荡得到了明显的改善;同样通过实验验证了单层布线带屏蔽层的驱动回路布线方式可以有效地降低驱动回路电感,从而使器件的栅源电压几乎无振荡,确保了器件的安全。

[1]Lu B,Liu W,Liang Y,et al.Optimal design methodology for LLC resonant converter:proceedings of the Applied Power Electronics Conference and Exposition,APEC 2006 Twenty-first Annual IEEE,2006[C].IEEE.

[2]赵敏杰,戴瑶,张怀武.LLC谐振变换器的参数设计[J].磁性材料及器件,2011,42(2):53-57.Zhao Minjie,Dai Yao,Zhang Huaiwu.Design of the parameters in LLC resonant converter[J].Magnetic Materials and Devices,2011,42(2):53-57(in Chinese).

[3]马皓,祁丰.一种改进的LLC变换器谐振网络参数设计方法[J].中国电机工程学报,2008,28(33):6-11.Ma Hao,Qi Feng.An improved design method for resonant tank parameters of LLC resonant converter[J].Proceedings of the CSEE,2008,28(33):6-11(in Chinese).

[4]胡海兵,王万宝,孙文进,等.LLC谐振变换器效率优化设计[J].中国电机工程学报,2013,33(18):48-56.Hu Haibing,Wang Wanbao,Sun Wenjin,et al.Optimal efficiency design of LLC resonant converters[J].Proceedings of the CSEE,2013,33(18):48-56(in Chinese).

[5]欧阳茜,吴国良,钱照明.LLC谐振全桥 DC/DC变流器的优化设计[J].电力电子技术,2008,41(1):15-16.Ou yangqian,Wu Guoliang,Qian Zhaoming.Optimal design considerations of the LLC resonant full-bridge DC/DC converter[J].Power Electronics,2008,41(1):15-16(in Chinese).

[6]Yang B,Lee FC,Zhang A,et al.LLC resonant converter for front end DC/DC conversion:proceedings of the Applied Power Electronics Conference and Exposition,APEC 2002 Seventeenth Annual IEEE,2002[C].IEEE.

[7]GaN Transistors for Efficient Power Conversion-Chapter 1.pdf[M].http://epc-co.com/epc/DesignSupport/WhitePapers.aspx.

[8]Reusch D,Gilham D,Su Y,et al.Gallium Nitride based 3D integrated non-isolated point of load module[C]//Proceedings of the Applied Power Electronics Conference and Exposition(APEC),2012 Twenty-Seventh Annual IEEE.2012:38-45.

[9]Shenai K,Shah K,Huili X.Performance evaluation of silicon and gallium nitride power FETs for DC/DC power converter applications[C]//Proceedings of the Aerospace and Electronics Conference(NAECON).Proceedings of the IEEE 2010 National.2010:317-321.

[10]Matsuura K,Yanagi H,Tomioka S,et al.Power-density development of a 5MHz-switching DC-DC converter[C]// Proceedings of the Applied Power Electronics Conference and Exposition(APEC).Twenty-seventh Annual IEEE,2012:2326-2332.

[11]Zhang Weimin,Long Yu,Zhang Zheyu,et al.Evaluation and comparison of silicon and gallium nitride power transistors in LLC resonant converter[C]//Proceedings of the Energy Conversion Congress and Exposition(ECCE).2012 IEEE,2012:1362-1366.

[12]Wang Kangping,Yang Xu,Zeng Xiangjun,et al.Analytical loss model of low voltage enhancement mode GaN HEMTs[C]//Proceedings of the Energy Conversion Congress and Exposition(ECCE).2014 IEEE,2014:100-105.

[13]Reusch D,Strydom J.Understanding the effect of PCB layout on circuit performance in a high frequency gallium nitride based point of load converter[C]//Proceedings of the Applied Power Electronics Conference and Exposition(APEC).2013 Twenty-Eighth Annual IEEE,2013:649-655.

Optimal Design of GaN-based LLC Resonant Converter

MA Huan,WANG Kangping,YANG Xu,GAN Yongmei

(School of Electrical Engineering,Xi’an Jiaotong University,Xi’an 710049,China)

Firstly,the operating principle of LLC resonant converter was discussed and the switching transition of enhancement-mode Gallium Nitride(eGaN)based LLC resonant converter was analyzed in detail.The results show that the reverse conduction of eGaN transistors can be avoided by adjusting the dead time and the oscillation of power loop can be decreased by reducing the high frequency power loop inductance.Then the dead time and power loop layout were optimized and the driving loop layout was carefully optimized to ensure safety of GaN transistors because the safety margin of the eGaN transistors’gate-source voltage is very small.Finally,a 1 MHz,100 W,48 V/12 V LLC experimental prototype was built to verify the design.The experimental results show that the overshoot of transistors’drain-source voltage was reduced from 15%to 6.7%when the high frequency power loop inductance was reduced from 5.6 nH to 0.4 nH.In addition,the transistors’gate-source voltage shows almost no oscillation when the single layer with a shielding layer layout was applied in the driving loop.

LLC;GaN transistor;dead time;parasitic inductance;layout

马焕

马焕(1990-),女,硕士研究生,研究方向:开关电源,E-mail:mahuan1224@st u.xjtu.edu.cn;

王康平(1989-),男,博士研究生,研究方向:电力电子集成技术,E-mail:wang kangping@stu.xjtu.edu.cn;

杨旭(1972-)通信作者,男,教授,博士生导师,研究方向:电力电子集成技术、开关电源技术、自动控制技术,E-mail:yangxu@mail.xjtu.edu.cn;

甘永梅,女,副教授,博士生导师,研究方向:现场总线技术,E-mail:ymgan@mail.xjtu.edu.cn。

10.13234/j.issn.2095-2805.2015.1.21

:TM 46

:A

2014-07-25

台达环境与教育基金会资助项目

Project Supported by Delta Environment and Education Foundation