基于DSP+FPGA+AD的多通路模拟信号采集方案的研究

王志伟 张 炜

(平高集团有限公司,河南 平顶山 467001)

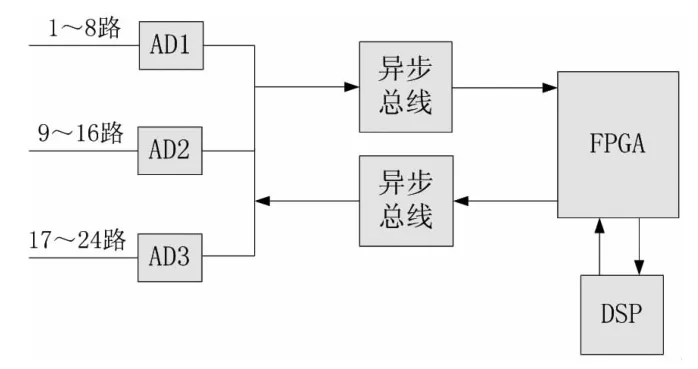

1 硬件方案框图(图1)

图1

2 模数转换

模数转换就是将模拟量转换为数字量的过程。理论分析指出,只有适当的采样频率才能真实地反映原始信号波形。经验数据表明,至少使用4倍于信号最高频率的采样频率才能保证不会丢失信号的任何信息。

AD7606 模数转换芯片是AI 公司推出的一款高性能模数转换芯片。它的主要特征是,8 通道双极性模拟量输入,最大输入范围±10V,轨对轨采样保持,16 位并联或串联多种输出方式,最高200k SPS 的采样速率。完全符合一般用途的模拟信号采样要求。使用3 片AD 可以同时完成24 路的模拟信号采集。

3 异步总线

异步通信总线提供可以在FPGA 和AD 之间提供一个隔离作用,同时完成AD 的输出电平和FPGA 的I/O 电平对接。

SN74LVC16245 是由TI 公司设计的一款被专门用来做异步总线通信的芯片。可以通过设置器件的(OE)、(DIR)可很容易实现总线的关闭、数据的双向传输,并且数据的双向传输功能基本上不需要额外的时序要求即可实现。

4 DSP+FPGA 结构

DSP(Digital Singnal Processor)是一种具备完整指令系统的微处理器。片内集成了控制单元、运算单元、各种寄存器和通信单元等,同时还可以外扩各种存储器,具有强大的运算能力和高运算速度。TMS320F28335 是TI 公司的一款低端多功能DPS 芯片,内嵌32 位高性能CPU、DMA 存储器、增强型控制外设、32 位时钟定时器、串行端口外设和内部模数转换器等丰富外设模块。其运算速度高达150MHz,单指令时钟周期6.67ns。

FPGA(Field Programmable Gate Array)是作为专用集成电路(ASIC)领域中的半定制电路出现的,既解决了定制电路的不足,又克服了原有可编程成器件门电路有限的缺点。XC3S1200E 是Xilinx 一款基于90nm 技术,Virtex 架构的高性价比FPGA,内嵌硬核乘法器和数字时钟管理模块。具有120 万个逻辑门数量,单元逻辑门成本达到相当低的水平。非常适合于逻辑和时序运算。

相比较而言,DSP 的指令系统适合运行高速算法,而FPGA 由于其全部逻辑由硬件电路完成,更适合于进行高速的逻辑运算及严格的时序约束,其内部并行结构也使其在高速的数据采集方面相对于DSP和单片机而言由巨大的优势,但其劣势在于难以实现一些比较复杂的算法。因此,单独采用FPGA 或者DSP 都不是数据采集的最佳方案。

DSP+FPGA 结构可以使DSP 的高速数据处理能力和FPGA 的高速、复杂的组合逻辑和时序逻辑能力得到最充分的发挥。随着大规模集成电路技术的发展,DSP+FPGA 结构更显现出巨大的优越性。

5 软件方案

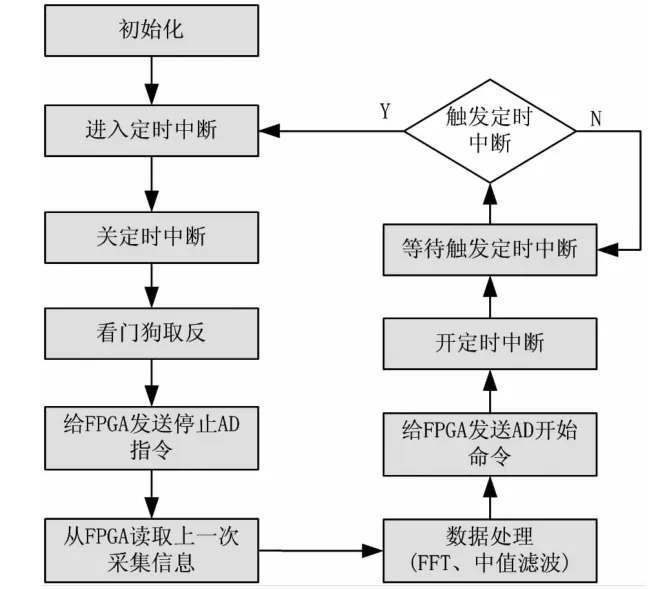

5.1 DSP 部分

DSP 作为系统的核心控制器,负责给FPGA 发送数据转换启动指令,读取FPGA 内的转换结果,处理读取的结果。上述功能可以使用一个定时中断来完成。框图如图2。

图2

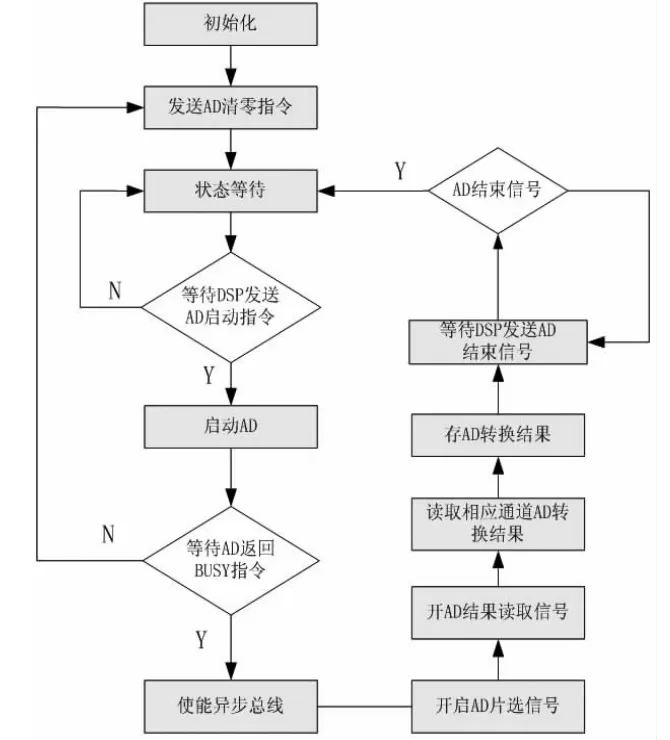

5.2 FPGA 部分

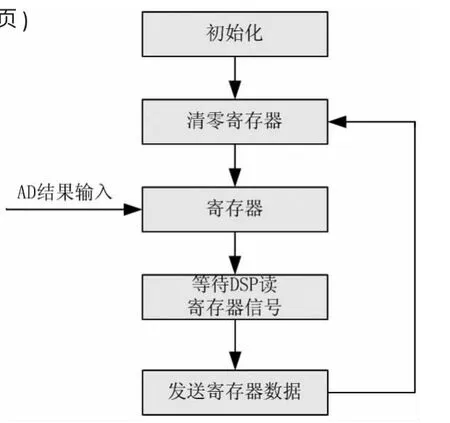

FPGA 作为系统的执行部件,一方面负责接受DSP 发出的数据转换启动指令,启动AD 数据转换,等待AD 转换完成,读取AD 转换结果;另一方面接受DSP 发出的数据的读取指令,上传AD 转换结果,清零内部寄存器。软件部分需要两个功能模块来实现,框图如图3、图4。

图3 AD 转换控制功能框图

图4 FPGA 数据上传至DSP 功能框图

6 结束语

随着FPGA 和DSP 的发展,DSP+FPGA 系统越来越得到广泛的运行。本文主要探讨了利用DSP+FPGA 进行高度模拟信号采集的应用,说明了平台的硬件搭接和软件方案。此平台结合了DSP 和FPGA 各自的优点进行搭建,符合两者最优配置,功能最大化原则。同时作者根据所述的硬件和软件方案完成了硬件设计,分别在CCS3.3 和ISE10.1 的环境下完成了软件的代码编写和调试。调试结果表明,所述方案可以实现10k SPS 的数据采集要求,采集结果完全满足作者设计要求。

[1]汉泽西.孙燕妮.DSP+FPGA 技术[J].电子技术,2007.02.

[2]潘松.EDA 技术使用教程[M].北京:科学技术出版社.

[3]彭启棕.管庆.DSP 集成开发环境-CCS 以及DSP/BIOS 的原理与应用[M].电子工业出版社,2004.

[4]杜慧敏.基于Verilog 的FPGA 设计基础[M].西安电子科技大学出版社,2006.