基于PCIe的高速图像注入式仿真系统

樊 博,王延杰,孙宏海

(1.中国科学院 长春光学精密机械与物理研究所,吉林 长春130033;2.中国科学院大学,北京100049)

0 引 言

一些高速实时图像处理的图像数据为一些特殊场景的高速图像数据,例如导弹飞行爆炸图像、飞机起飞着陆图像、航天器发射运行图像等,这些图像处理系统开发过程中往往需要有真实场景验证阶段。且不说这些场景可不可以随意创造,单是每次试验的成本就已经足够惊人。为了解决这个问题,常用仿真的方式模拟这些场景。但是这些模拟的场景与真实的场景还是会有很大的差别。在改进过程中提出了两种仿真方式可以一定程度克服上述不足,一种为半实物仿真,另一种为数字图像直接注入式仿真[1]。其中,半实物仿真的灵活性不高,而且花费较大;而数字图像直接注入式仿真可以克服上述缺点。现阶段的数字图像注入式仿真平台大多数采用USB或者PCI总线传输图像数据[2],这些系统的传输带宽有限,很难适应高分辨率高帧频数字图像仿真需求。

随着处理器技术的不断发展,互连领域中,高速差分总线技术代替并行总线技术是大势所趋。PCIe(PCI express)于2001年正式发布,是Intel公司开发的第三代IO总线标准。PCIe总线是串行总线技术,可以在很高的频率上传输数据,所以在保证数据完整性的同时有很高的带宽。其中PCIe Gen1 标准x1通道单向传输速率为2.5Gb/s,PCIe Gen2标准x1通道为5Gb/s,最新的PCIe Gen3 在相同的条件下传输速率为8Gb/s。

鉴于此,本文设计了基于PCIe的高速图像注入式仿真系统,利用Xilinx高性能可编程逻辑器件Virtex-6FPGA(field programmable gate array)实现PCIe接口、DDR3控制器、DMA 引擎、Cameralink和DVI等接口控制逻辑。同时编写PCIe DMA传输的驱动和上位机程序,实现真实场景高速图像实时输出功能,并且输出的图像数据时钟和分辨率可以在上位机中随时调整,可以适应不同系统的仿真需求。

1 PCIe协议结构

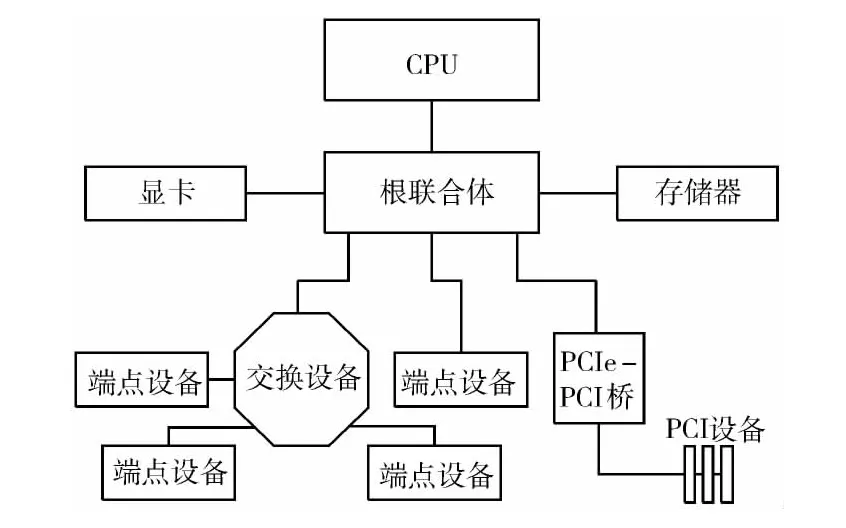

PICe设备可以分为两种,一种为根联合体(root complex,RC),另一种为端点设备(endpoint,EP)。如图1 所示,RC包括PCIe总线端口、存储器控制器等一系列与外部设备有关的接口。在PCIe总线规范中,EP 也就是基于PCIe总线的设备。本文设计的PCIe系统为EP,计算机系统为RC,二者通过PCIe接口连接到一起,并且通过计算机将真实场景视频传送到板卡并经过板卡的Cameralink和DVI接口将图像输出,作为其它需要高速图像的处理系统的数据源。

图1 PCIe系统拓扑结构

PCIe总线规范定义了数据报文发送接收过程中需要通过的3个层次,分别为:事物层、数据链路层和物理层。实际数据传输的过程为,数据报文在设备的核心层产生,经过传输层打包为传输层包(transaction layer packet,TLP),再经过数据链路层打包为数据链路层包(data link layer packet,DLLP),最后经过物理层打包为物理层包(physical layer packet,PLP),最终发送出去。接收端的过程为发送端的逆过程。

PCIe协议层次结构如图2所示。

2 系统设计

实现PCIe接口主要有两种方式,一种为桥接芯片,将PCIe总线转接到本地总线,这种方式PCIe的传输速度不会特别高,主要受到本地总线传输速度的限制和总线转换的带宽损失;另一种为FPGA 实现,主流FPGA 厂商都将PCIe功能集成到其FPGA 产品中,可以快速开发基于PCIe的各种应用。FPGA 厂商Xilinx推出的高、中、低档FPGA都集成有PCIe硬核IP。本文采用第二种方式实现PCIe接口,选择Xilinx Virtex-6系列FPGA 作为主芯片,这样可以充分利用PCIe的高带宽来传输高速图像,同时可以方便地实现图像输入输出接口与PCIe接口的功能对接。

图2 PCIe协议层次结构

PCIe总线接口提供了一个高速传输的通道,传输数据还需要有符合PCIe协议的传输逻辑模块。对于简单的数据传输PCIe IP Core在生成的同时会有一个参考的PIO(programmable input-output)设计[3],但是该设计传输的数据仅是单个数据包传输,对于连续大量的高速图像数据显得无能为力。因此,本文在FPGA 端设计一个DMA 传输引擎,该引擎符合PCIe协议规范,并可以满足高速图像传输需求,同时在PC端开发对应的驱动程序和上位机应用。

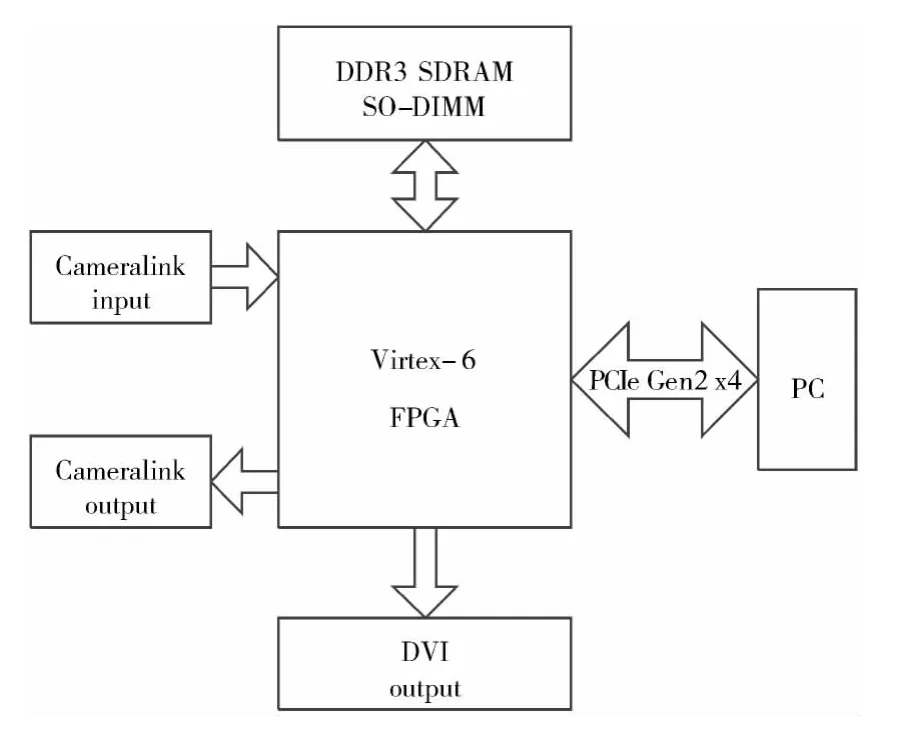

本文设计的系统组成如图3所示,主要有两大部分组成,即硬件部分和软件部分。其中硬件部分包括PCIe接口、Cameralink 输入和输出接口、DVI输出接口、DDR3 SODIMM 接口以及这些接口的FPGA 控制逻辑;软件部分包括PCIe接口驱动、DMA 驱动和上位机程序。

图3 系统框架

2.1 硬件设计

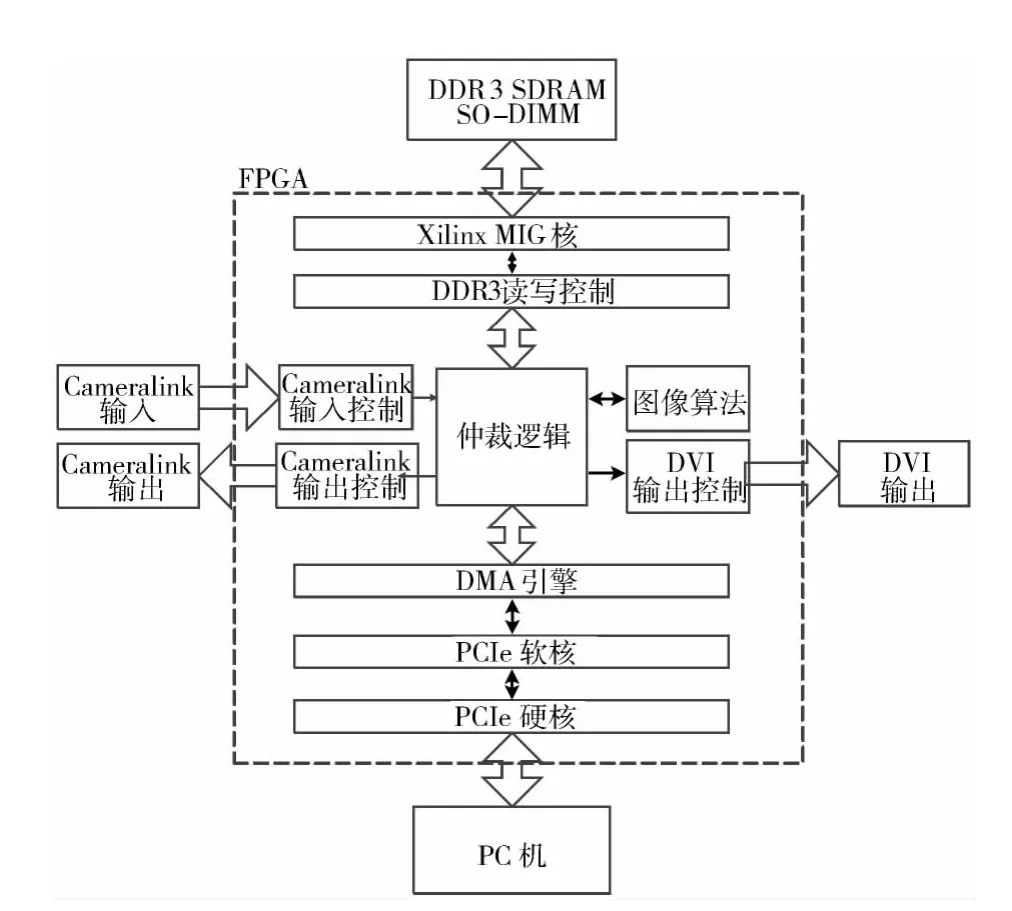

FPGA 逻辑模块设计是本文硬件设计的核心,包括Cameralink输入输出模块、DVI输出模块、DDR3读写控制模块、PCIe模块、图像算法模块和全局仲裁控制模块。仲裁控制逻辑模块起到控制中心的作用,用以协调整个硬件系统的工作。

由于这些模块单一FPGA 中实现,因此这些模块之间的数据传输就十分方便,这也能充分提高系统传输带宽。下面主要介绍DDR3 读写控制模块、PCIe DMA 模块和全局控制模块。

FPGA 模块结构如图4所示。

图4 FPGA 模块结构

2.1.1 DDR3读写控制模块

对存储设备的控制和访问是一个系统数据稳定和高速的首要任务。本文采用Xilinx MIG (memory interface generator)IP Core来实现对所设计的DDR3SDRAM 的控制。该IP Core传输稳定且带宽利用率较高,为本系统提供稳定、高速、大容量的图像缓存空间。

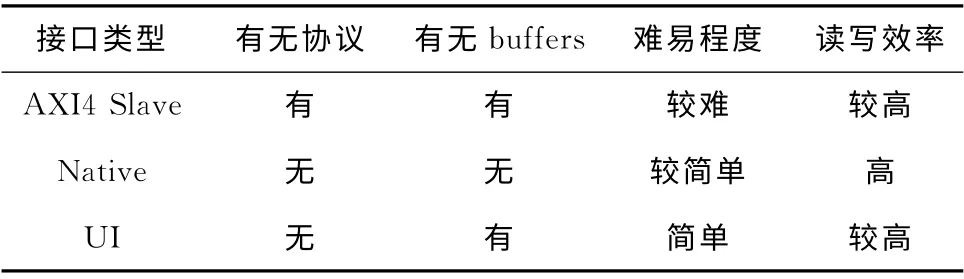

读写控制模块直接控制的是MIG,而MIG 对读写操作有严格的时序要求。MIG 提供3种与用户逻辑的接口,分别为AXI4Slave接口,Native接口和UI接口[4]。3种接口的特点对比见表1。AXI4(高级可扩展接口4)是ARM 推出的第四代AMBA 接口规范,使用者需对这个规范有一定了解,比较复杂,使用难度较大;Native接口没有包含buffers,所以数据传输快,但是数据可能会乱序,需要用户自己组织数据,增加了难度;UI接口是Native接口的简化,增加了buffers以使数据和读写请求同步,不用自己组织数据,相对容易操作。因此,本文选择通过UI接口连接DDR3读写控制模块和MIG 控制器。

表1 MIG 的3种接口对比

DDR3读写速率和位宽与各个接口模块的速率和位宽不同,这就需要二者之间有一个数据缓存设备。FPGA 设计中常用的缓存设备包括FIFO 和双端口RAM,本文采用FPGA 内部Block RAM 综合而成的双端口RAM 作为缓存设备。而对这些缓存RAM 读写时采用高位地址 “乒乓”的策略,这样可以保证数据不会被非法覆盖或者丢失。

2.1.2 PCIe DMA 模块

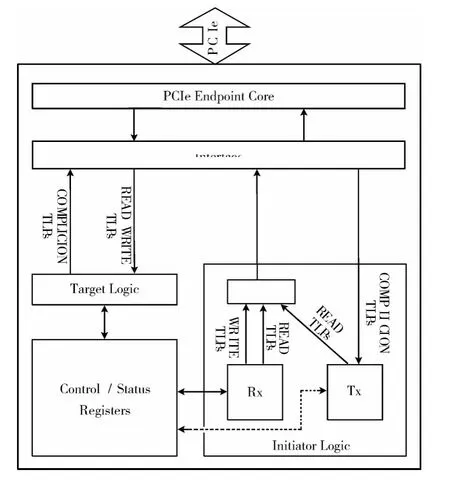

如上所述,为了传送大块图像数据,本文设计了如图5所示的DMA 传输结构[5,6],并将其与PCIe硬核IP Core相连接,组成高速图像传输的引擎。

图5 DMA 结构框架

在DMA 模块中Target Logic模块用于捕捉PC 设备发出的单次MWr(存储器写操作)和MRd(存储器读操作)。如果是MWr TLP,那么根据收到的写入地址和内容来改变Control/Status Registers中相应的寄存器值;如果是MRd TLP,那么模块将首先读取Control/Status Registers中相关寄存器,然后根据MRd 的地址返回相应的Cpld TLP;Control/Status Registers模块包含了DMA 控制器的所有寄存器,这些寄存器都映射到BAR(基址寄存器)空间中[4-6]。PC通过对BAR 空间的读写实现对相关寄存器的读写,以此控制DMA的操作;Initiator Logic用于产生MWr 和MRd包,以及解析PC 传回的Cpld包,是完成DMA 读写操作的主要部分[7]。

2.1.3 全局控制模块

全局控制模块是整个系统能够正常工作的 “指挥中心”,负责各个模块访问DDR3的仲裁以及数据流走向的选择,充分保证了本系统高速图像数据的稳定传输。

当某一设备发起对DDR3的读/写请求时,控制模块首先判断此时DDR3 是否正在进行读/写操作,如果DDR3忙,则此请求被挂起。当另一设备占用DDR3 读/写结束时,该命令会被响应。这样可以保证多个设备访问DDR3的稳定性。假设所有设备同时发起访问DDR3的请求,这时DDR3首先应该响应哪个设备呢?这就需要一个优先级来规定DDR3首先响应哪个请求。图像数据来源于Cameralink输入或者PCIe输入,因此本文将这两个设备的请求分别设置为优先级最高和次高,这样可以充分保证数据在开始端不会出错。

图像数据流走向的选择主要是通过将DDR3存储区划分为分别对应Cameralink输入和PCIe输入的两块来实现的。在PCIe DMA 中定义一个数据流向选择寄存器,通过判断此寄存器的值来决定输出设备选择哪个输入源的图像数据输出。而数据流向选择寄存器的值可以在上位机中更改,这样就实现了上位机控制图像数据的流向。

2.2 软件设计

PCIe与PCI最大的不同在于物理传输上采用更加先进的串行数据传输,是点对点的总线技术,多设备互连需要使用交换器。但是PCIe总线是在PCI总线的基础上发展起来的,继承了许多PCI总线的概念和标准。尤其在驱动和软件方面,PCIe协议规定其向下兼容[8]。PCIe的BAR 空间的定义与PCI的定义没有本质区别,只是PCIe扩展了BAR空间的定义。因此可以参照PCI设备驱动的开发方法来开发PCIe设备的驱动。

2.2.1 开发工具选择

Microsoft公司开发的DDK(device development kit)驱动开发工具,代码较简单,结构较清晰,效率较高,但是开发难度较大,现已停止更新,被同一公司的WDK(windows development kit)所取代。

DriverStudio是CompuWare公司开发的驱动开发工具,将编写驱动程序所需要的内核访问函数和硬件访问函数封装成类,所以是面向对象的开发方式[9]。使用该工具开发驱动难度较小,驱动效率较高。但是该软件已停止更新。

还有一种是Jungo公司出品的WinDriver,它将驱动的开发做了最大程度的简化,为开发人员提供了丰富全面的接口函数。利用这些函数,开发人员不必掌握操作系统的知识就可以在短时间内开发出不同总线的驱动程序。它还有一个重要特点就是跨平台性,在Windows XP 下开发的驱动程序不需要任何修改就可以应用于WindowsCE 和Linux等系统中,具有非常好的可移植性。

所以本文选择WinDriver作为驱动程序的开发工具,既可以保证一定的传输速度,又可以保证驱动程序对不同操作系统平台的兼容性。

2.2.2 驱动程序开发

WinDriver中的Driver Wizard工具可以快速检测到插入PC机的PCIe设备,并且可以对PCIe即插即用设备的I/O,存储和中断进行检测。当检测设备的各种资源没有问题时,可以生成该设备的驱动程序代码。这些程序代码包括操作硬件内核级API函数、用这些API函数操作硬件的样本程序以及各种工程文件。

到此,驱动程序的框架就生成了。但是一些具体的功能如DMA 操作还需要用编译工具打开生成的样本程序,并作具体修改。

本文DMA 驱动程序设计时充分考虑了系统的具体需求,采用增加PCIe单个数据包有效载荷和减少单次DMA数据包个数的技巧来增大传输效率,改善DMA 传输高速图像数据的效果。另外,为高速图像传输专门定义一些寄存器,如帧起始标志寄存器和帧传输结束寄存器等,这些寄存器为高速图像传输带来很大便利性,也是本文针对高速图像传输应用场合的改进DMA 引擎设计,在实际应用中具有很好的效果。

2.2.3 上位机开发

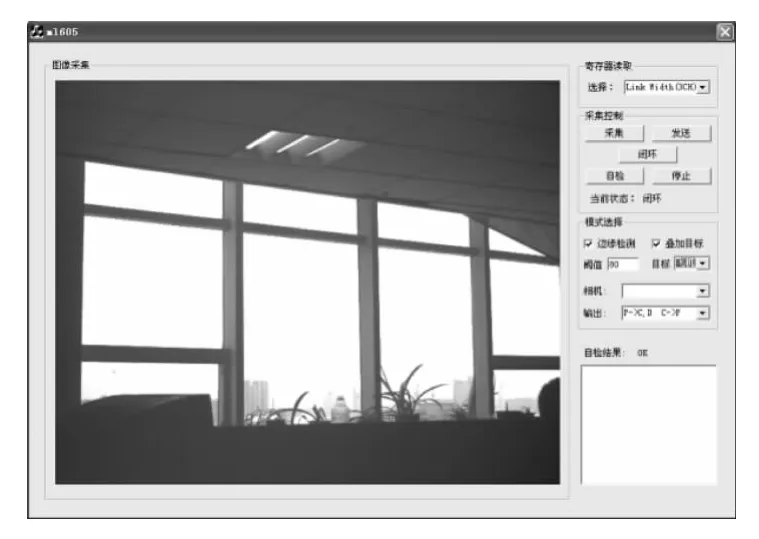

本文设计的上位机程序采用VC++6.0和MFC 编写,目的为验证PCIe硬件设计和驱动程序的可靠性,以及注入式仿真平台各项功能的正确性,并验证了本文设计的DMA引擎传输高速图像的正确性,同时测试了PCIe传输高速图像的速率。其中,DMA 传输的操作流程如图6所示,上位机截图如图7所示。上位机可以控制图像输出的分辨率和帧频,并且可以在真实场景图像中叠加一些信息。

3 实验及讨论

3.1 实 验

本文所设计的基于PCIe的高速图像注入式仿真系统与PC机通过PCIe延长线相连,通过PC机的上位机程序控制真实场景图像处理和输出[10]。

3.1.1 实验效果

如图8所示为本文设计的高速图像注入式仿真系统的实验结果,图中左侧屏幕显示的是Cameralink 输出图像,中间屏幕显示的是上位机存储的图像,右侧屏幕显示的是DVI输出的图像。其中上位机存储的图像可以为Cameralink输入的图像,也可以为存储在本地硬盘的真实场景视频图像。而Cameralink和DVI输出的图像为上位机传输到FPGA 中的图像。如上所述,这些图像数据在FPGA 硬件板上都是存储于DDR3SDRAM 中的。

3.1.2 性能测试

图6 DMA 操作流程

图7 上位机截图

图8 实验结果

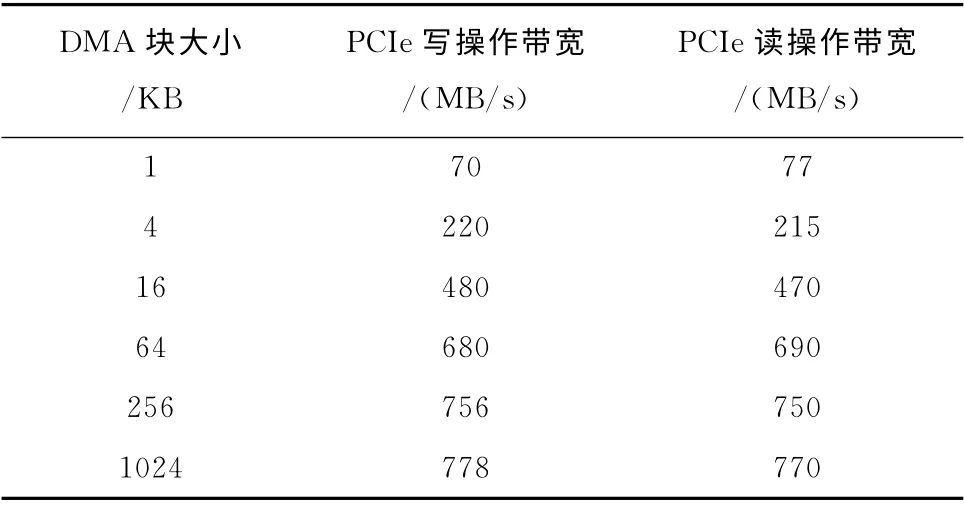

在上述实验条件下,对本文设计的PCIe接口的传输带宽进行了测试。读写操作的带宽测试结果见表2,这里的写操作是指PCIe板卡传输图像到上位机,读操作是指PCIe板卡读取上位机图像。

表2 带宽测试结果

3.2 讨 论

本文实验条件中计算机的处理器主频和内存容量会对本文系统的传输速度有一点影响,在实际使用时,系统的传输速度可能会因计算机配置的不同有所区别。而且PCIe采用延长线的方式会在一定程度上降低PCIe传输速度,所以本文测试传输速度在没有PCIe延长线的情况下会有所提升。本文实验主要测试系统的稳定性,相机参数为1280x1024分辨率,60 帧/s,未达到系统设计时的需求,但是测试速度时采用多次读取相同帧的方式提高数据速率来测试PCIe的传输速率。所以本文实验和性能测试都是真实可靠的。

4 结束语

本文设计的基于PCIe的高速图像注入式仿真系统利用了PCIe的高速传输特性将硬件与计算机软件结合,硬件可以控制各个接口的图像数据传输,软件可以将真实的场景图像传输给硬件,并且控制硬件输出图像的分辨率和帧频。同时PCIe的高速传输特点降低了图像传输的延时,保证仿真图像的实时性;FPGA 控制的DDR3 可以缓存大量的图像数据,保证仿真图像输出的稳定性。另外该系统的硬件设计是基于单片Virtex-6FPGA 实现的,所以该系统具有数据真实、实时性好、适应性广、集成度高、功耗低等特点,在高清晰度高速图像注入式仿真领域有重要应用价值。

[1]LI Xiangchun,DU Xiaochun,LIU Yang,et al.Real-time image acquisition and semi physical simulation system design[J].Computer Simulation,2012,29 (11):38-41 (in Chinese).[李向春,杜晓春,刘扬,等.高动态实时图像采集与半实物仿真系统设计 [J].计算机仿真,2012,29 (11):38-41.]

[2]HUANG Yongshun.A infrared-sensor simulator based on USB2.0[J].Infrared Technology,2009,31(2):77-80(in Chinese).[黄永顺.基于USB2.0数字图像注入式红外探测器仿真器设计[J].红外技术,2009,31(2):77-80.]

[3]Xilinx,Inc.Virtex-6FPGA integrated block for PCI express user guide,UG517(v5.1)[EB/OL].[2010-09-21].http://www.xilinx.com.

[4]Xilinx,Inc.Virtex-6 FPGA memory interface solutions user guide,UG406(v1.10)[DB/OL].[2012-01-18].http://www.xilinx.com.

[5]LI Muguo,HUANG Ying,LIU Yuzhi.Design of DMA transmission with PCIe bus interface based on FPGA [J].Computer Measurement & Control,2013,21 (1):233-235 (in Chinese).[李木国,黄影,刘于之.基于FPGA 的PCIe总线接口的DMA 传输设计 [J].计算机测量与控制,2013,21 (1):233-235.]

[6]WANG Jinghua,HU Shanqing,LONG Teng.The implementation of DMA reading and writing module on FPGA based on PCI express protocol[J].Microcomputer Information,2010,26 (10-2):7-9 (in Chinese).[汪精华,胡善清,龙腾.基于FPGA 实现的PCIE 协议的DMA 读写模块 [J].微计算机信息,2010,26 (10-2):7-9.]

[7]Xilinx,Inc.Bus master performance demonstration reference design for the Xilinx endpoint PCI express solutions[EB/OL].[2011-09-29].http://www.xilinx.com.

[8]LIANG Guolong,HE Xin,WEI Zhonghui,et al.Driver development of PCIE data acquisition card [J].Computer Engineering and Applications,2009,45 (31):63-65(in Chinese).[梁国龙,何昕,魏仲慧,等.PCIE数据采集系统的驱动程序开发 [J].计算机工程与应用,2009,45 (31):63-65.]

[9]YING Sancong,WANG Mingyin,ZHANG Xing.Key technologies of high-performance PCI driver [J].Computer Engineering and Design,2012,33 (6):2208-2212 (in Chinese).[应三丛,汪明寅,张行.高性能PCI驱动程序的关键技术[J].计算机工程与设计,2012,33 (6):2208-2212.]

[10]WANG Ke,MA Li,SHU Weiqun,et al.Real-time simulation platform for airborne image processing engine[J].Journal of System Simulation,2011,23 (9):1832-1836 (in Chinese).[王科,马丽,殳伟群.机载图像处理引擎实时仿真平台 [J].系统仿真学报,2011,23 (9):1832-1836.]