基于AES-TAC/iHASH 的片外存储器安全防护

蔡路亭,徐金甫,张立朝

(解放军信息工程大学,河南 郑州450004)

0 引 言

嵌入式系统的高效性及其存储数据的机密性、完整性缺一不可。目前,对片外存储器的安全防护研究有Execute-Only Memory(XOM)[1]、PE-ICE/TEC-tree[2,3]、AESTAC[4]等技术。以上方案对数据的安全性提供一定保障的同时,也都存在不同的缺陷。比如TEC-tree的性能过低,XOM 和AES-TAC无法保障系统的完整性。AES-TAC 安全防护方案中为保障数据加密的效率,引入了AESOTP[5]。AES-OTP将AES分组加密后的数据充当序列加密运算的密钥流对明文进行加密处理。该方案将时间戳参数(TS)、访问寻址参数(address)和填充参数(pad)组合成128比特AES输入参数,AES计算获得一组加密密钥。

AES-TAC具有很好的安全防护性能,并且执行效率极高,但是不提供完整性安全防护功能。如果存储器中的数据被篡改或被重置,系统将无法解密出正确的数据。假如系统无法识别错误数据,也无法提出警报,并强行使用错误数据,将导致不可预知的后果。因此必须增加完整性安全防护功能,识别上述攻击,使系统一旦发现存在上述攻击,则及时停止运行。Romain Vaslin对AES-TAC 方案进行了改进[6],增加了循环冗余校验码(CRC)校验机制,对每组数据进行CRC计算,生成一组校验码,并保存在片内专用存储器中。其优点在于CRC 并行化计算效率极高,不足的是CRC基于线性编码理论,只对数据进行奇偶校验,自身不带密钥,校验能力有限。

本文提出一种基于AES-TAC 的扩展安全防护方案(AES-TAC/iHASH),在原有功能基础上增加了完整性校验功能,能高效识别出篡改后的数据,解决了嵌入式系统的高效性和安全性问题。

1 增量哈希算法

嵌入式系统的安全防护功能不仅要确保系统能抵抗各种攻击(重放攻击、碰撞攻击、重置攻击、欺骗攻击等),同时还必须保障系统的运行性能。因此完整性校验算法必须同时具备安全性和高效性。完整性校验通常使用标准哈希算法(如MD5、SHA-1、SHA-2等),但是其运算流程较复杂,效率太低。针对标准哈希算法的上述问题,在此引入增量哈希算法[7]。

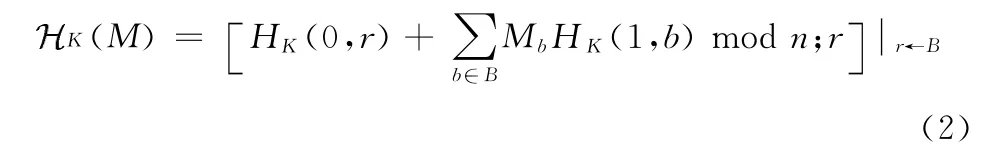

多元集合增量哈希算法iHASH(incremental multiset hash functions),是基于伪随机哈希算法群的扩展算法,能对哈希值构成的多元集合进一步执行摘要提取,即二次哈希运算。增量哈希算法具有集合的抗碰撞性、高效性和极高的安全性(带有密钥)。增量哈希算法的基本定义如下所示

其中随机选取r←B,r 已知且固定不变。元素b∈B 在M中出现的次数记为Mb,即元素b在M 中的重数。HK:{0,1}m+1→是从伪随机哈希函数群中随机选择的哈希算法。

因为定义中K(M)的哈希值Hk(1,b)总和作为运算中间变量,不可能被攻击者获得,因此可以将多项式HK(0,r)从公式中移除。可将式(2)进一步简化,如式(3)所示

此时经过化简的增量哈希算法非常适宜工程实现。但是伪随机哈希算法Hk仍然对增量哈希算法的实现及应用带来了很强的限制性,实现Hk需要消耗大量的面积,损失系统的高效性。

通过上述分析可以发现,增量哈希算法能对哈希数集合执行进一步摘要提取计算,从集合中提取出标签值。运算的安全性非常强,且效率很高。但是哈希数集合的生成较为复杂,需要对该算法做进一步的优化。

2 AES-TAC/iHASH 安全防护方案

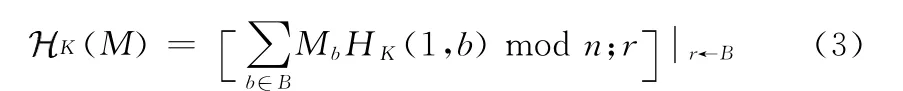

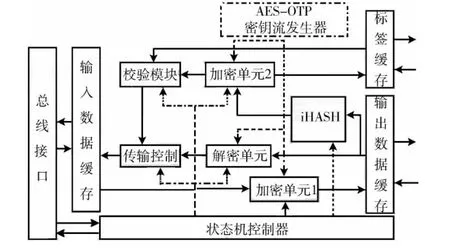

根据第1节的分析,在此提出一种将AES-TAC 安全防护技术和增量哈希算法相结合的方案[8-11],如图1所示。其中图1(a)为系统写流程,图1(b)为系统读流程。

图1 AES-TAC/iHASH 安全防护方案

本方案在原有AES-TAC 防护流程中增加了完整性校验步骤。AES-TAC方案中,CPU 生成读(写)指令后,安全模块根据访问地址从时间戳中读取时间参数TS。结合读(写)访问地址及填充数据,生成128比特AES输入参数并进行分组加密运算。再将加密后的数据充当密钥流与总线读写数据进行异或,实现数据的加密存储。本方案把加密后的数据送入增量哈希算法硬件模块中,生成完整性校验标签值。系统写操作流程如图1(a)所示,系统使用加密数据生成相应的标签值,并存入片外存储器。系统读操作流程如图1(b)所示,系统根据读取的加密数据,重新生成标签,并与片外存储器中保存的标签相比较。如果两个标签值相等则校验通过,将数据送入总线;如果不相等则校验失败。

下文将针对算法扩展部分的可行性及安全性做出说明。分析式(1)可知,算法实例化的限制条件为:

强无碰撞性:不存在(x,y)满足H(y)=H(x)且y≠x,不同类型的增量哈希算法分别具有标准集合抗碰撞性和多元集合抗碰撞性。

单向不可逆性:对于任意的h,无法找到x 满足H(x)=h,使攻击者获知非安全存储区域内数据后不能逆推出原始数据。

弱无碰撞性:无法伪造标签(无法伪造第二原像)。

结合AES-OTP加密算法,考虑是否可以使用加密后的数据替代增量哈希算法中要求的哈希值,以充分利用现有密码运算资源,更加高效地实现完整性校验算法。针对上述限制条件的可行性分析如下:

AES分组密码算法有混乱原则和扩散原则,保证了不同的输入加密后获得的密文相关性极弱,所构成的密文集合满足随机数的特性。序列密码运算流程为:E:ci=di⊕mi,其中mi为明文,di为密钥流,异或获得密文ci。只要di满足随机性特性,则密文ci就满足随机性特性。因此异或加密的数据集合符合增量哈希算法中集合的定义。满足限制条件(1)。

在AES算法密钥及时间戳安全存储的前提下,攻击者无法获得完整的AES输入值及密钥,因此无法获得密钥流(AES输出)。根据序列密码算法原则,密钥流安全的前提下,加密过程安全。攻击者无法通过大量密文攻击出密码参数,更无法功过密文h伪造出明文x。满足限制条件(2)。

因为增量哈希算法基于AES-OTP 加密后的数据,哈希值再经AES-OTP 加密后存储在片外,因此攻击者必须同时获得AES-OTP密码参数和iHASH 初始化向量才能伪造增量哈希算法值。而所有密码运算单元及参数都保存在片内安全存储区域中,因此攻击者无法伪造标签。满足限制条件(3)。

综上所述,将AES-TAC加密流程和iHASH 算法相结合(简称AES-TAC/iHASH),满足增量哈希算法的限制条件。结合后的算法不仅保留了原有的加密功能,而且能安全高效地实现完整性校验功能。

3 硬件设计与实现

为了实现第2节提出的安全防护方案,硬件结构应包括数据输入缓存、数据输出缓存、标签缓存、加(解)密单元、iHASH 引擎、校验模块、传输控制单元和状态机控制器。方案的硬件结构如图2所示。

图2 AES-TAC/iHASH 硬件结构

时间戳专用存储器采用片内RAM 实现,根密钥AESkey和填充数据Pad保存在片内EFlash中,系统启动时对AES-core初始化。AES-core及iHASH 用硬件模块实现,并编写专用控制器实现控制。

为尽量减少片内安全存储资源的消耗,将生成的标签经加密后存储在片外非安全存储区域。两个数据缓存分别存储非密数据和加密后的数据。

3.1 iHASH 引擎设计

式(3)中,使用模n加的形式进行运算,n可以根据需要取值。任意模n加运算的硬件电路实现较为复杂。假设n=2m,则可以通过高位舍去的方式实现,相对较简单。但是进位仍然可能构成影响效率的关键路径。

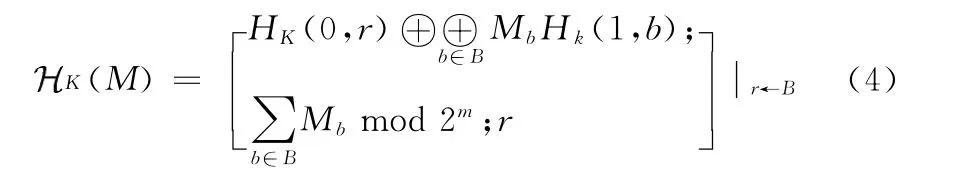

式(3)的多项式之间基于模n加运算。取n=2,则条件中的多元集合M 重数小于2,意味着M 为标准集合,也即推导出其具有标准集合抗碰撞性的哈希算法Mset-XORHash。而且显然逐位模2加既是异或操作,“XOR ⊕”。算法的定义也作相应变化,如式(4)所示

经简化后为

哈希算法Hk(1,b)计算而得的哈希值点乘重数,再与其它多项式异或。在执行异或操作前加入初始化向量,增加算法的安全性。

iHASH 引擎的硬件结构如图3 所示。iHASH 引擎包括输入单元、输出寄存器、密钥管理单元、置换网络、路由算法单元及控制状态机等。输入输出数据位宽可根据需求进行扩展。用户可事先对密钥管理单元进行配置,每次运算前密钥管理单元对引擎进行初始化。路由算法单元可根据用户配置自动生成置换网络参数,配置后的置换网络将完成运算中的移位、置换操作。状态机控制器完成整体控制工作。

图3 iHASH 引擎硬件结构

iHASH 引擎执行哈希运算前首先通过密钥进行初始化,再将需要参与哈希运算的数据(n比特位宽)输入运算单元展开运算。通过路由算法配置的置换网络完成移位置换。运算完成后的校验码通过数据输出寄存器输出。

3.2 读写操作流程

通过先校验再读写的原则,可以防范重放攻击等多种针对片外存储器的攻击。如果所需数据(或需要写入的数据组)在缓存中,可以取消校验的步骤,直接进行读写。

AES-TAC/iHASH 读写操作流程如图4所示。读操作中,从片外读取的数据先经过完整性校验再送入数据总线。写操作中,如果操作地址对应的数据不在缓存中,先从片外将数据读出,并进行完整性校验,通过后替换数据,重新生成标签,再写入存储器中。哈希运算的数据集合元素个数可以根据需要设定。

图4 AES-TAC/iHASH 读写流程

读操作流程如图4(a)所示。首先把从片外存储器寻址读取的数据送入加密缓存中,密文输入iHASH 模块,最终获得新的标签值T’,同时将解密后的数据送入非密缓存。标签值T’经加密后生成CT’,标签值CT’和CT 相比较判定是否通过完整性校验。

写操作流程如图4(b)所示。如果数据事先缓存在数据缓存中,则将数据送入非密缓存中,再将替换后的数据经密钥流加密输入加密缓存。加密数据随后同时送入片外存储器及iHASH 模块,最后生成标签T’,加密成CT’,存储到片外。

4 性能分析与评估

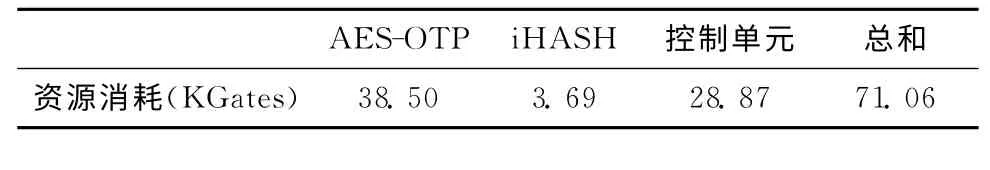

使用综合工具在0.13μm 工艺条件下,对各硬件单元单独进行综合,面积参数见表1。本方案在系统面积上的消耗主要集中在AES 算法模块和控制单元。除了新增硬件模块,方案还占用了部分片内安全存储资源和部分片外非安全存储资源,分别用以存储时间戳和加密后的标签。

表1 AES-TAC/iHASH 面积评估

通过逻辑综合可知,关键路径存在于AES模块内,安全模块的最大运行频率为576MHz。

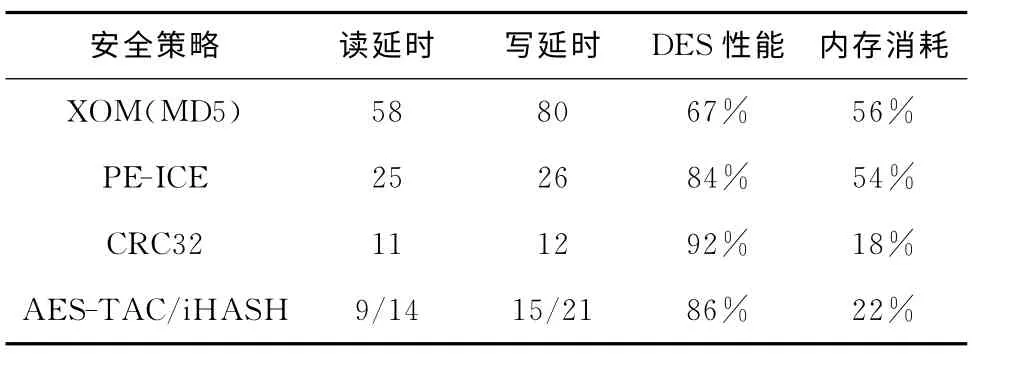

表2为AES-TAC/iHASH 安全防护方案内部参数取不同值时的性能评估。n表示每组iHASH 运算的数据集合元素个数,m 表示处理的数据位宽。参数n和m 取不同值时,内存的消耗及处理的性能各不相同。读(写)延时中,AESTAC/iHASH 中的两个数值分别表示数据缓存与不缓存时的延时周期数。“系统性能”项表示加载相应安全策略的系统性能与未加载安全策略的系统性能的比值。 “内存消耗”项表示相应安全策略占用系统内存的百分比。

表2 AES-TAC/iHASH 性能评估

分析表2可知,AES-TAC/iHASH 的性能及资源消耗较为理想。内存消耗只与集合基数n相关。n越小,相同数据总量下将生成更多的标签,则标签存储的内存消耗越大,满足关系式P=1/(n+1)*100%。存储访问的性能与n、m的取值相关。集合基数越小,则标签生成及校验的时间消耗越少,效率越高。数据位宽越大,校验相同数据量所需的校验步骤越少 (每次校验的数据量增大),效率越高。结合上述评估参数,为尽量平衡内存消耗及性能需求,参数的最优取值为n=4、m=32。

当AES-TAC/iHASH 安全防护方案参数配置为n=4、m=32时,和其它典型安全策略的执行性能相对比,综合分析结果见表3。“DES性能”项表示运行DES软算法时,加载安全策略的系统性能与未加载安全策略的系统性能的比值。从表3可知,AES-TAC/iHASH 的硬件资源消耗非常少,执行性能较高。

表3 性能对比评估

5 结束语

为了保障嵌入式系统的安全性,本文通过将AES-TAC硬件安全防护方案和增量哈希算法相结合,提出了AESTAC/iHASH 片外存储器安全防护方案。该方案充分利用密码运算资源,安全高效地实现了片外存储器的安全防护,极大地增强了芯片的安全性,使系统免受重放攻击、重置攻击和欺骗攻击的威胁,保障芯片的安全运行,实现了嵌入式系统安全性和高效性的并存。

[1]Doomun M R,Soyjaudah K.Analytical comparison of cryptographic techniques for resource-constrained wireless security[J].International Journal of Network Security,2009,9 (1):82-94.

[2]Elbaz R,Torres L,Sassatelli G,et al.A parallelized way to provide data encryption and integrity checking on a processormemory bus[C]//Proceedings of the 43rd Annual Conference on Design Automation,2006:506-509.

[3]Elbaz R,Champagne D,Lee R B,et al.Tec-tree:A low cost and parallelizable tree for efficient defense against memory replay attacks [C]//Workshop on Cryptographic Hardware and Embedded Systems,2007:289-302.

[4]Liu Zhenglin,Zhu Qingchun,LI Dongfang,et al.Off-chip memory encryption and integrity protection based on AES-GCM in embedded systems [J].Design & Test,IEEE,2013,30(5):54-62.

[5]Lee Sung-Jae,Jae Seong Lee,Lee Mun-Kyu,et al.Low-power design of hardware one-time password generators for card-type OTPs [C]//ETRI Journal,2011,33 (4):611-620.

[6]Romain Vaslin.Hardware core for off-chip memory security management in embedded systems [D].France:European University of Brittany,2008.

[7]Hu Yin,Ghaith Hammouri,Berk Sunar.A fast real-time memory authentication protocol[C]//ACM New York,NY,USA:Proceedings of the 3rd ACM Workshop on Scalable Trusted Computing,2008:31-40.

[8]Elbaz R,Torres L,Sassatelli G,et al.Block-level added redundancy explicit authentication for parallelized encryption and integrity checking of processor-memory transactions [G].LNCS 6340:Trans on Comput Sci X,2010:231-260.

[9]Elbaz R,Champagne D,Gebotys C,et al.hardware mechanisms for memory authentication:A survey of existing techniques and engines [G].LNCS 5430:Trans on Comput Sci IV,2009:1-22.

[10]Romain Vaslin.Hardware core for off-chip memory security management in embedded systems [D].France:University of South Brittany,2008.

[11]Crenne J,Vaslin R,Gogniat G,et al.Configurable memory security in embedded systems[J].ACM Transactions on Embedded Computing Systems,2011,12 (3):71.