基于FPGA的高速高精位置获取与传输系统

霍立刚,周云飞,刘广斗

(华中科技大学机械科学与工程学院,湖北武汉430074)

0 引言

在一些实时性要求很高的运动控制系统中,控制任务极其复杂,同时要求高速度,高精度。例如光刻机的步进扫描运动控制,需控制多达15轴的运动,要求在高加速度(1.5g)、高速 (1.2m/s)运行条件下达到纳米级的运动精度控制。要实现这样的要求,高速高精度的位置反馈是必须的[1]。EnDat2.2同步双向数字接口可以为数字驱动系统提供极高精度的位置信息,高速光纤通信提供编码器到位置伺服计算处理器的通信通道,实现位置值的高速可靠的传输。光纤作为传输介质,传输速率高、传输容量大、衰减小,传输距离长、抗干扰能力强、耐高温、抗腐蚀、工作可靠、成本低廉,对现场复杂的实时性要求很高的控制系统可谓是完美的解决方案[1-4]。

现场可编程逻辑门阵列FPGA具有容量大,编程灵活,并行处理能力强的特点,在各种通信协议的实现方面得到广泛应用。本文中最关键的内核,光纤通信内核与En-Dat2.2内核都是在FPGA上编程实现的,因此协议具有灵活可配置的特点[5]。

1 系统整体实现方案

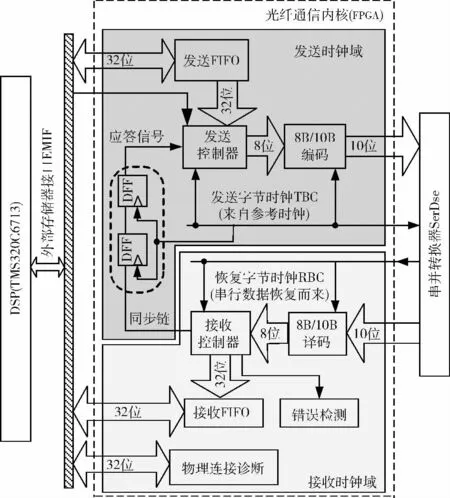

位置获取与传输系统的整体结构如图1所示,主要分为以下几个部分:

(1)串并转换器:串并转换 (Serializer/Des erializer)简称SerDes,是高速串行通信中最关键的部件。在本文中我们选取德州仪器TI的TLK1221来完成串并转换的功能。TLK1221是千兆以太网收发器,用于高速全双工的点对点数据传输,支持0.6Gbps-1.3Gbps的数据速率,基带传输特征阻抗为50Ω,这一点要在制板的时候得到保证。在发送端,经过8B/10B编码的并行10位数据在发送参考时钟TBC的上升沿被锁存,然后将数据以参考时钟的10倍频将串行化并通过PECL兼容的电平差分信号进行传输;在接收端,将隐藏在串行数据流中的时钟信号提取出来。该时钟信号是从发送端的时钟信号经过相位内插调整相位关系而来,与10位的恢复并行数据的字节边界对齐,因此被形象的称为恢复字节时钟RBC[6]。

图1 位置获取与传输系统总体结构

(2)激光收发器:选取安捷伦公司的HFBR53A3完成电信号与光信号的转换。HFBR53A3是一款多模光纤接口的光纤收发器,兼容ANSIX3.297-1996标准的光纤通道物理接口,支持300m长的62.5/125um MMF光缆和500m长的50/125um MMF光缆,本文中采用的是前者,长度为3米。

(3)光纤通信内核:该通信内核在 Altera公司的EP3C16F484C8型号的FPGA上实现,是系统传输模块中最核心的部分。内核完成最上层控制单元DSP与传输模块之间的通信连接,控制着通信数据包格式、发送接收机制、链路物理诊断、及通信错误情况处理等最核心的功能。

(4)位置获取模块:EnDat协议内核也是在FPGA上实现,完成从位置编码器高速可靠地获取位置值的功能。根据EnDat接口规范,采用RS485通信接口,RS485平衡发送和差分接收,具有很强的抑制共模干扰的能力。为匹配线路特征阻抗 (characteristic impedance),在数据和时钟的差分线路端部,各需加一个120Ω的电阻,同时各线路应加一个330pF的电容,以滤除高频干扰。由于采用串行数据传输方式,故只需要4条信号线,接口十分简单可靠。

2 光纤通信内核的FPGA实现

图2 光纤通信内核

光纤通信内核包含通信的物理层和传输协议控制层两个层面,基于FPGA和SerDes的传输模块,完成数据包的传输控制,并行串行转换,编解码、时钟信号的恢复提取、字节的相位对齐等一系列核心的功能。如图2所示,通信内核包含发送与接收控制、编解码、串并转换、错误处理、及数据缓冲等模块。发送控制器由最上层控制单元DSP通过外部存储器接口EMIF进行控制,如被触发,立即将保存在发送FIFO中的数据,按照内核协议规定好的数据包格式进行打包,然后再经过8B/10B编码,最后在发送参考时钟TBC上节拍下,将并行的数据经过SerDes串行的输出到光纤通道。接收控制器则不受最上层控制单元DSP的直接控制,其接收逻辑由状态机实现,通过检测几个特殊字符来判断不同的接收逻辑,内核用到的特殊编码字符将在后面详细介绍。接收控制器在恢复时钟RBC的节拍下将串行的数据流反串行化之后正确地对齐10位数据的边界,然后经过8B/10B译码,最后将校验正确的数据保存到接收缓冲区中,同时产生应答信号,发送应答字符给对方,表示本次接收已成功完成。数据保存到接收缓冲区之后,会硬件产生数据接收中断,以告知最上层控制单元DSP数据接收完毕,可以读取处理。在图2中,用不同颜色标识的两个区域,分别代表发送时钟域和接收时钟域,这两个时钟域由不同的时钟基准,因此是不相关的,信号在两个时钟域直接传递就涉及跨时钟域信号传递的问题。

应答信号由接收时钟域产生,要传递到发送时钟域。为了最大限度地减少由于亚稳态造成的设计失败,我们采用了两级同步寄存器链,同步寄存器链允许额外的时间来让亚稳态信号到达一个确定的状态,使得设计更加安全。

3 数据包格式及高速数据编解码

高速光纤通信属于串行通信方式,数据通过差分线路发送和接收。未经编码的数据会产生直流偏移,这将影响在接收端的信号质量,使得时钟和数据的提取变得异常困难。本文所述系统采用IBM提出的标准8B/10B编码方式。在图2中,发送控制器送出的8位并行数据在送往串并转换器SerDes之前必须经过8B/10B编码,然后将编码后的10位并行数据串行化发送。8B/10B编码支持8位数据的256种编码组合,除此之外还有一些编码组合用以特殊的功能,故被称之为特殊字符。采用8B/10B编码的目的是提高信号在光纤信道上的传输特性。该编码方式保证了串行数据流有足够的跳变密度,从而有利于接收端的时钟恢复;最大运行长度 (Run Length)即连续的0或者1的个数为5,可以有效的抑制串行数据流的频谱范围和码间干扰 (inter-symbol interference,ISI);由于0和1的数量相同,故达到了直流平衡,提供足够的驱动能力。8B/10B编码详细编码方式见参考文献[3],在此不再赘述,只列出本文中位置获取与传输系统用到的特殊字符,其余特殊字符暂作保留,待扩展使用[7]。系统涉及到的特殊字符见表1。

表1 系统涉及到的特殊字符

数据包的传输格式与编码方式及这些特殊字符有着密切的关系。串并转换器TLK1221采用IEEE 802.3千兆以太网预定义的10位K28.5字符作为字对齐的解决方案。在接收端,时刻监测该字符,当K28.5字符落在期望的字边界,说明10位的字边界正确对齐,不需要重新校正对齐;当K28.5字符横跨在期望字边界上时,需要重新校正对齐字边界。在收到K28.5字符后,通过重新调整恢复时钟与字边界的相位关系,当前的数据被缩短或延长,数据出现损坏,但K28.5字符之后的数据又重新对齐了字边界[8]。

数据包传输格式如图6所示,由数据包开始标识符SOF、数据包结束标识符EOF、32位的帧头、32位的有效数据、字对齐字符K28.5及各自的校验字符组成。其中32位的有效数据可以通过帧头的最高8位数据长度由DSP从1到255自由配置。对每个32位的有效数而言,传输总是以最低8位开始,最高8位结束。校验字符由4个8位数据相加得到,溢出位自动忽略,因此校验字符长度也是8位。

然而,在每个32位的有效数据之后都要插入一个字节的校验字符,这也就意味着校验消耗了1/5的通信链路带宽。同时,为了对齐正确的字边界,在每个校验字符后面又插入了字对齐字符K28.5,连同校验字符一样,消耗了有效的通信链路带宽。但对于高速高可靠性的控制系统而已,这样的协议开销是值得的,也是必须的[9]。

4 EnDat协议内核的FPGA实现

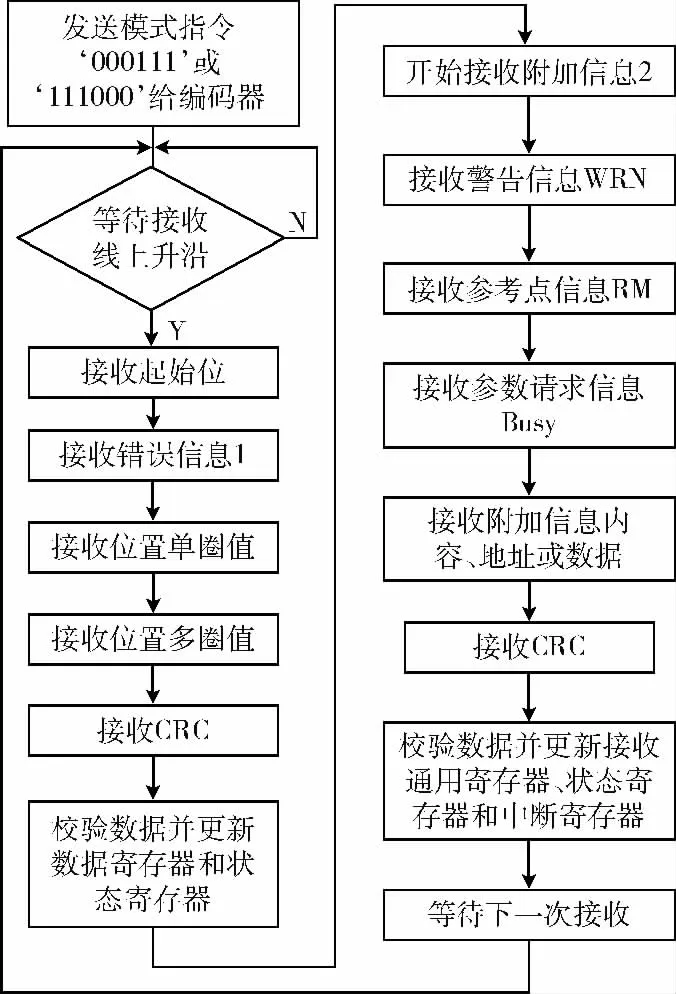

EnDat协议内核为数字驱动系统的反馈环提供快速高可靠性地位置值传输,为了使系统更加可靠,同时提供错误检测和诊断的功能。图3所示为EnDat协议内核的结构图,由时序控制模块、发送模块、接收模块、时钟生成模块、相关寄存器及其与光纤通信内核的逻辑接口模块组成。

在内核结构图的左侧,是内核与同步串行双向接口的物理层接口信号,包括发送信号线、接收信号线、时钟信号线及其各自的使能信号。在右侧,则是与光纤通信内核连接的并行接口,包括了各种控制信号,8位的地址总线,32位的数据总线。其中地址总线为8位宽度,对应于传输数据包格式中有效数据的个数被限定在255以内。

发送寄存器、模式指令寄存器和配置寄存器保存着待发送的数据。一旦触发,这些数据被转为串行数据流在时序控制模块的控制下由发送模块串行发送给编码器,同时时钟生成模块生成所需个数的时钟脉冲。接收模块在时序控制下将串行的数据流进行串并转换,并将并行的数据,依据不同的含义,分配在3个寄存器中,同时更新状态寄存器和中断寄存器,并产生中断或触发信号给光纤通信内核。

根据 EnDat协议规范,采用5位的循环冗余检验(CRC)码来完成串行通信的数据校验功能。将接收到的CRC码与之前接收到的串行数据流在本地生成的CRC码进行比较,即可检验通信的正确与否。CRC校验可以检测出数据传输中的所有单一错误,是正确快速地获取位置值的保证[10]。CRC校验结果保存在如图3所示的状态寄存器中。

图3 EnDat协议内核

5 系统位置获取与传输机制

系统传输流程及位置获取流程如图4、图5所示。本文位置获取与传输系统中,最上层控制单元为DSP,所有的数据传输进程都受其控制。数据传输按数据流的方向分为上行数据进程和下发数据进程。下发数据进程即DSP向EnDat内核下发各种配置数据的过程;上行数据进程即DSP向位置获取模块发送请求位置数据的过程,在此详细论述上行数据进程,下行数据进程与之类似,在此不再赘述。DSP下发请求位置数据命令,光纤通信内核A收到触发,发送请求数据字符K28.2即TTC特殊字符。经过高速光纤通道,接收端光纤内核B收到该特殊字符,立即启动EnDat内核向位置编码器的位置请求过程,完成后开始向模块A按照图6所示的数据包格式发送位置数据及相关状态信息,模块A接收完毕数据,产生中断,触发DSP读取数据开始处理过程。

6 样机测试

位置获取时序系统测试结果如图7所示,为简便起见,模式指令选取无附加信息的位置值请求指令。从时序图上可以清楚的看到位置值按照EnDat规定的时序传输,长时间稳定无误。

数据包的传输时序如图8所示,该图由Altera公司的在线逻辑分析仪测试而来,从中可以明确地看到数据在状态机的控制下按照图6的格式进行传输,测试结果表明,数据传输正确,且长时间测试无误码产生,传输稳定可靠。

7 结束语

图5 位置获取流程

对位置获取与传输系统的实现方案进行了介绍,给出了若干关键技术的实现方案,详细描述了光纤通信内核以及EnDat通信协议内核的原理结构及其FPGA的实现方法。1.25Gbps的样机测试结果表明系统工作稳定,可以实现对编码器位置值准确高速地获取与传输,满足强实时性控制系统对位置反馈环高速高精度的要求,对于超精密运动控 制系统具有重要作用。

图6 传输数据包格式

图7 位置获取时序

图8 光纤传输数据包时序

[1]CHENG Xin,ZHOU Yunfei,HU Yongbing,et al.Synchronous measurement and control mechanism based on high-speed fiber channel link [J].China Mechanical Engineering,2011,22(19):2325-2330(in Chinese).[程鑫,周云飞,胡永兵,等.基于高速光纤链路的同步测控机制 [J].中国机械工程,2011,22(19):2325-2330.]

[2]SU Shaojing,GUO Xiye,ZHANG Shimeng,et al.Data acquisition system of ultra-high speed optical communication [J].Journal of Data Acquisition & Processing,2007,22(3):374-377(in Chinese).[苏绍璟,郭熙业,张世猛,等.超高速光纤通信数据采集系统 [J].数据采集与处理,2007,22(3):374-377.]

[3]MIN Xiaoping,LU Da,HONG Hongrong.Implementation of highspeed optical communication system based on field programmable gates array(FPGA) [J].Journal of Xiamen University(Natural Science),2007,46(4):491-495(in Chinese).[闵小平,陆达,洪鸿榕.基于现场可编程门阵列的高速光纤通信的实现[J].厦门大学学报 (自然科学版),2007,46(4):491-495.]

[4]ZHOU Ping,WANG Meng.Design of a data collection system with high-speed transfer function [J].Fire Control Radar Technology,2009,38(2):53-59(in Chinese).[周萍,王萌.具有高速传输功能的数据采集板的设计[J].火控雷达技术,2009,38(2):53-59.]

[5]XIA Yuwen.Verilog digital system design tutorial[M].Beijing:Press of Beihang University,2008(in Chinese).[夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.]

[6]Roosevelt G,Roper W,Romanko T.Optimizing high speed serial communication using Honeywell Rad Hard SerDes[C]//NASA/ESA Conference on Adaptive Hardware and Systems,2011:215-219.

[7]CHEN Zhangjin,ZHONG Guohai,BIZhuo.A high speed 8B/10B encoder/decoder design based on low cost FPGA[J].Microcomputer Information,2012,28(10):361-367(in Chinese).[陈章进,钟国海,毕卓.一种基于低成本FPGA的高速8B/10B编解码器设计 [J].微计算机信息,2012,28(10):361-367.]

[8]Haller I,Baruch Z F.High-speed clock recovery for low-cost FPGAs[C]//Design,Automation & Test in Europe Confe-rence & Exhibition,2010:610-613.

[9]LUO Fuyuan,ZHOU Yunfei,Yin Juan.Design and implementation of HSSL communication in distributed motion control system [J].Computer Engineering and Applications,2007,43(2):205-208(in Chinese).[罗福源,周云飞,尹涓.分布式运动控制系统HSSL通信设计与实现 [J].计算机工程与应用,2007,43(2):205-208.]

[10]ZHANG Shugang,ZHANG Suinan,HUANG Shitan.CRC parallel computation implementation on FPGA [J].Computer Techno-logy and Development,2007,17(2):56-62(in Chinese).[张树刚,张遂南,黄士坦.CRC校验码并行计算的FPGA实现[J].计算机技术与发展,2007,17(2):56-62.]