DUC的FPGA实现及在EDGE-QAM中的应用

王 涛,李 俊

(1.国家新闻出版广电总局广播科学研究院,北京100866;2.成都德芯数字科技有限公司,四川成都610045)

EDGE QAM即为边缘QAM调制器,输入IP封装的TS流,输出为QAM调制信号。该设备集成了多通道的IP接收及路由、复用、加扰(可选)、QAM调制及上变频功能。是一种低成本、高集成度的数字电视前端设备,广泛的应用于数字电视播出、VOD互动点播系统中。

近年来,随着现场可编程门阵列(FPGA)器件在逻辑规模和处理速度方面性能的快速提高,可以利用FPGA来实现高速大规模的数字运算及信号处理[1]。数字上变频DUC(Digital Up Conversion)就是其中的一种典型应用,可以用于EDGE-QAM调制器的设计中,替代传统的模拟上变频器,从而实现基带调制信号到直接数字射频信号的输出。大规模的FPGA可以很容易地实现多通道的QAM调制编码及DUC,再结合高速DAC实现数字到模拟信号的转换,可以实现低成本、多通道的QAM调制。

本文介绍了一种利用高速FPGA进行DUC处理,并实现32通道EDGE-QAM调制的应用,并给出实测结果。该设计实现了32通道的方根余弦滚降成型滤波,DUC数字上变频处理,并通过DAC转换为模拟信号输出。最终数字信号采样率达到2 048 MSample/s,输出频率范围为36~860 MHz,输出信号带宽为768 MHz,每个载波输出频率可单独在768 MHz范围内任意可调整。

1 DUC的总体结构及各模块介绍

DUC主要由数据采样率提升,数字混频等模块组成。其中采样率提升模块包括对数据进行插值及低通滤波,提高输入信号的采样率。在高的采样率下,配合数字混频模块,采用数学运算的方法,直接将信号混频到射频频率并输出。由于混频采用的是数字运算的方法实现,因此可以避免传统模拟上变频器因为模拟器件IQ不匹配的误差,具有非常高的性能,再配合高速的DAC器件,可以直接输出射频的调制信号。

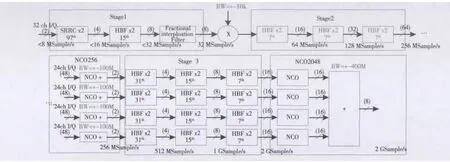

本设计的DUC模块结构如图1所示,主要由3级内插及滤波模块及3级NCO混频模块组成。内插模块实现数字信号采样率的提升,以达到最终的2 048 MSample/s采样率。混频模块实现数字信号频谱搬移,实现32通道每个通道输出频率的独立调整,具有很大的调节范围和很小的调节步进。

设计所采用的主系统时钟为256 MHz,在数据的采样率低于256 MSample/s时,采用分时复用的方法进行串行计算以节省资源。在stage3及以后的处理,数据的采样率大于256 MSample/s时,采用并行计算输出进行串行拼接以达到较高的处理速度。

stage1模块是DUC与QAM调制的FEC部分的接口,将映射之后的符号进行方根余弦滚将滤波、2倍插值、以及分数倍插值将采样率插到固定的32 MSample/s,以便于后续的DUC处理。由于QAM调制要求符号率可变,调节范围为1~7 MSample/s,因此每通道符号时钟为8 MHz,最后一级需要进行分数倍插值,以插到固定的采样频率,以便进行后续的滤波及混频操作。

图1 DUC模块系统构架

stage2为3级2倍内插操作,由于每级都是2倍内插,因此滤波器采用半带滤波,由于滤波器有一半系数为零,能够减少一半的乘法操作,比较节省FPGA内部的乘法器和加法器资源。同时也有比较好的频率相应。经过3级升采样滤波后基带信号采样率可以提升到256 MSample/s。

之后是NCO256模块,在256 MSample/s的采样频率下,将32通道的基带信号分配到4个NCO子模块内,每个通道数据只能分配到其中的一个NCO子模块,分配之后每个子模块进行基带信号的混频及混合,每一路的输出信号带宽可以达到192 MHz,在一个NCO子模块内最多可以合成24个8MHz的QAM信号或者32个6MHz的QAM信号。

stage3为3级2倍内插操作,由于采样频率高于256 MSample/s,因此采用并行操作才能实现高的采样率。滤波器同样采用半带滤波,经过3级升采样滤波后基带信号采样率可以提升到2 048 MSample/s。

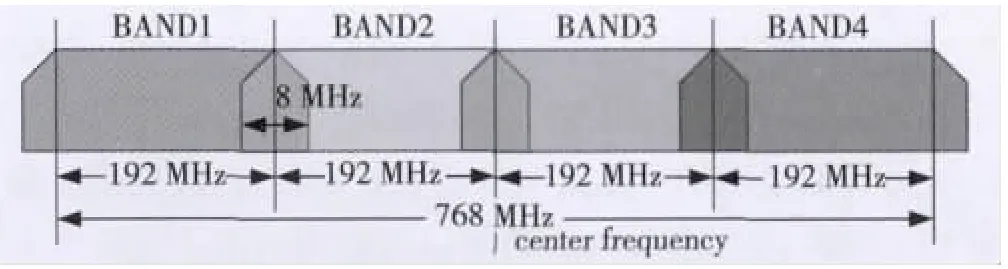

最后是NCO2048模块,将4路信号进行混频及合成。每路信号的中心频率间隔192 MHz,再进行合成,可以将射频频谱进行拼接,得到总带宽为768 MHz的基带信号。经过这样的处理,最终实现输出32个QAM通道射频输出频率单独可调,并且总输出带宽可达768 MHz。如图2所示。

图2 DUC输出频率分布图

2 DUC核心模块设计

2.1 DUC中滤波器的设计

要实现基带成型,根据DVB-C调制标准[2],需要采用方根余弦滚降(SRRC)滤波器,滚降系数为0.15。通过MATLAB进行滤波器设计,要实现60 dB的阻带衰减,需要用96阶的FIR滤波,滤波器的频响特性如图3所示。

图3 方根余弦滚降(SRRC)滤波器幅频响应(截图)

设计的SRRC滤波器滚降系数为0.15,通带纹波小于0.01 dB,阻带抑制可达到75 dB。滤波器采用FPGA的专用乘法器实现,FPGA采用Altera的Arria5器件,可以实现超过300 MHz的乘累加操作,完全可以满足设计要求。由于主系统时钟为256 MHz,而DVB-C的符号率不超过7 MHz,考虑到SRRC滤波内插补零的点可以不参与运算,因此一个滤波器可实现32路数据即16个IQ调制通道的滤波。因此整个32通道QAM调制通道只需要2个SRRC滤波器即可实现。

同理,2倍内插滤波器也采用MATLAB设计。stage1里紧跟SRRC之后第一级2倍内插采用23阶系数即可实现。由于是2倍整数内插,采用半带设计,滤波器系数有一半为零,可以减少一半的运算量。由于中心抽头系数为0.5,可以采用移位实现而不用耗费乘法器。再去掉为零的系数及考虑系数对称,实际只用计算6个乘法即可实现滤波器的运算,可以大大减小FPGA的乘法器消耗。滤波器设计通带范围为0.3,系数量化到16 bit,可以实现80 dB的阻带衰减。该滤波器的频响特性如图4所示。

图4 2倍内插滤波器幅频响应

2.2 DUC中NCO的设计

该设计中的混频由3级NCO模块实现,分别工作在32 MSample/s,256 MSample/s和2 048 MSample/s采样频率上。三级NCO组合,可以实现每个载波输出频率单独可调,调节步进为1 kHz,输出频率范围为36~860 MHz。

NCO32混频器为stage1与stage2之间的混频器,可调节频率步进为1 kHz,范围为±0.5 MHz。NCO256混频器为stage2与stage3之间的混频器,可调节频率步进为0.5 MHz,范围为 ±128 MHz。NCO2048 混频器,为 stage3之后的混频器,可调节频率步进为4 MHz,范围为±1 024 MHz。以上3级混频可实现±1 024 MHz,步进1 kHz的混频,可将任一基带载波混频到任一范围内的射频频率,完全能满足设计需求。

在数字系统中,广泛的采用NCO产生正交的本地震荡信号,即正、余弦信号。随后与输入信号相乘来实现混频操作。而NCO的设计通常采用坐标旋转数字计算(CORDIC)算法来实现或者查找表(LUT)来实现[3]。CORDIC算法采用迭代运算计算出需要的cos,sin值,它能达到的精度受迭代次数影响。要提高计算精度,需要增加CORDIC算法的迭代次数,这会导致逻辑资源的增加及逻辑延时的增加。而基于LUT的方法则比较简单直接,将cos,sin值存在ROM中,只需要一个相位累加器进行累加得到相位地址,并根据相位地址从ROM中查找得到所需要的cos,sin值即可。该方法适合相位分辨率略低一些的应用,否则ROM的容量就会非常大。ROM可以采用FPGA内部嵌入的RAM块实现,可以达到非常高的速度。而ARRIA5的FPGA中有大量的RAM资源可以使用,因此本设计主要采用的是LUT查找表实现。具有结构简单、运算速度高、切换时间小、便于并行运算的优点。

因此综合考虑,NCO32工作频率在32 MSample/s,要实现1 KHz的频率步进,需要16 bit的相位精度才能满足要求。如果cos,sin值采用16 bit位宽,需要216×16×2=2 Mbit的 RAM,消耗 RAM块资源太多。因此采用CORDIC算法实现,迭代16次可以满足设计的精度要求。

NCO256工作频率在256 MSample/s,要实现0.5 MHz的频率步进,只需要9 bit的相位精度即可满足要求,采用查找表方法实现也只占用很少的FPGA的RAM块资源,因此本设计中采用查找表的方法实现,相位累加器采用9 bit,步进 1 bit代表 0.5 MHz。NCO2048 工作频率在2 048 MSample/s,要实现4MHz的频率步进,同样只需要9 bit的相位精度即可满足要求,因此也采用查找表方法实现。同时由于主系统时钟为256 MHz,因此需要同时采用8个NCO单元进行并行运算,每次计算8个顺序相位值的数据。在FPGA输出时,由专用的硬件serdes电路[4]将并行数据转为正常的采样率为2 048MSample/s的串行数据输出。

3 FPGA实现及验证

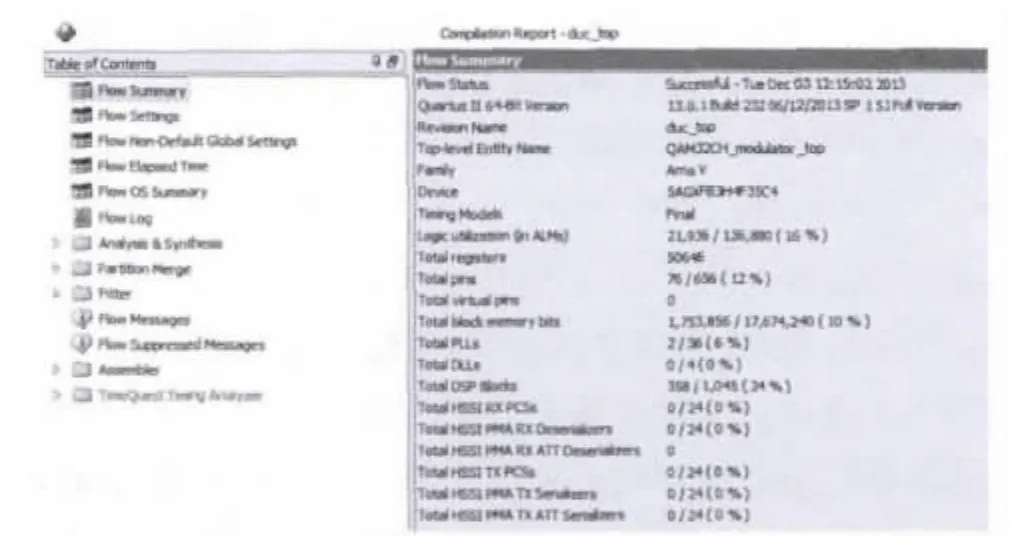

基于本设计的EDGE QAM调制器是基于Quartus II 13.0 进行编译的[5],最终在 Altera 公司 Arria V 系列5AGXFB3H4型号FPGA上实现EDGE-QAM的设计。实现了32通道的复用加扰及QAM编码调制。FPGA编译后DUC部分的资源占用如图5所示。

图5 DUC模块编译资源占用报告(截图)

如图5所示,经过合理设计,DUC模块只占用极少部分的FPGA资源,共使用21 936个ALM,占该FPGA总资源的16%;358个DSP Blocks,占总资源的34%。

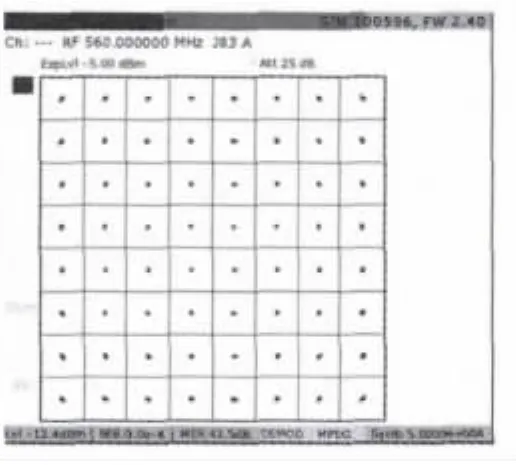

DUC部分工作在256 MHz时钟频率,可以实现总输出带宽为768 MHz,每个QAM调制通道频率步进为1 kHz,每个调制通道输出频率在768 MHz范围任意可调节。DAC选择ADI公司的 AD9739。该 ADC为14 bit,2.4 GSPS的高速DAC,有2个LVDS输入通道,每个输入通道最高速率为1.2 GSample/s,最高可输出960 MHz的射频信号。DUC数据输出通过FPGA的serdes输出给DAC,进行数模转换后直接输出射频信号。采用本设计的EDGE QAM调制器射频输出采用Agilent N9020A频谱仪和R&SETL信号分析仪测试,实际射频输出频谱及星座图如图6和图7所示,完全能达到设计的射频输出带宽,具有很高的射频输出带肩比和MER值。

图6 EDGEQAM射频输出频谱(截图)

图7 EDGEQAM射频输出星座图(截图)

4 小结

目前,采用该DUC设计的多通道EDGE QAM调制器已经应用于成都德芯数字科技有限公司的产品DX3232中,性能指标得到客户认可。本文给出了该EDGE QAM调制器中DUC模块的设计及实现方法。该方案广泛适用于各种EDGE QAM/IP QAM调制器中,以及其他多通道的调制器中,以实现数字上变频,代替模拟上变频器,可以实现高性能、高带宽的变频调制。

[1]EDA先锋工作室.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2011.

[2] EN 300 429,Digital video broadcasting(DVB);framing structure,channel coding and modulation for cable systems[S].1997.

[3]高亚君.基于FPGA的数字信号处理[M].北京:电子工业出版社,2012.

[4]EDA先锋工作室.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2011.

[5] Quartus IIHandbook Version 10.0[EB/OL].[2013-11-05].http://download.csdn.net/download/horizon317/2810494.