基于FPGA的多路数据采集与传输系统设计

李 华,刘宝盈,刘 萌,谢 谦

(商洛学院,陕西商洛,726000)

0 前言

在实际工程应用中,数据采集是最重要的设计环节之一。传统的设计形式存在一次只采集一路数据且传输距离较短、容易丢包等缺陷,已经远远不能满足实际应用的需要。另一方面,从设计的角度考虑,因为同时采集并传输多路数据要兼顾准确性和速度等众多因素,所以必须采用新的设计思路与方法来实现。本文以Xilinx公司的FPGA为主控芯片,结合TI公司的多路、高速ADC以及Philips公司的CAN协议芯片—SJA1000实现了对8路模拟数据的实时采集与传输。文章在理论分析的同时还给出了相关设计的ModelSim时序仿真波形,并对系统的实际采集与传输效果进行了分析与评价。

1 系统组成及工作原理

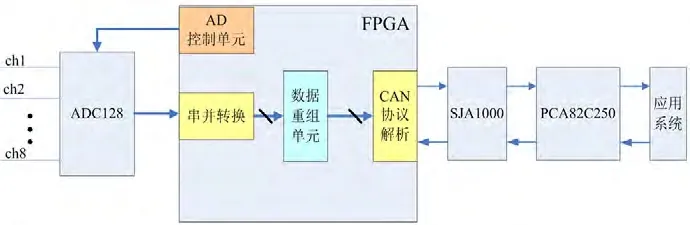

本文所设计的8数据采集与传输系统以FPGA为核心,首先用于产生ADC128正常工作所需要的时序,当ADC128正常工作并输出一位数字信号时,将一位信号送入FPGA进行串并转换,同时进行数据重组,用于改变数据格式以适应SJA1000的传输需要,然后将数据通过SJA1000协议芯片输出,经PCA82C250后传给应用系统。整个系统充分发挥了FPGA并行运算的优势,有效提高了数据采集和传输的速度和精度。

图1 系统原理框图

图1 所示为本文系统的原理框图,系统的具体工作过程为:将需要采集的8路模拟信号连接到ADC128的输入端(IN0-IN7),为了使ADC能够工作在50kSPS采集模式下,FPGA提供给ADC128的时钟频率为0.8MHz,这时ADC就开始以0.8MHz的数据速率输出一位数字信号。为了应用方便,系统首先将一位数字信号经过串并转换,变成12位的数字信号。但是一般传输系统的数据形式是8位,因此为了节约带宽,通过数据重组单元将12位信号重组成8位数字信号。因为ADC128以50kSPS的速率采集数据时,它每秒输出的数据量为50k*12b=0.6Mb,相应的带宽为0.6Mbps,而CAN的最大传输速率为1Mbps,满足带宽要求;和一般的通信总线相比,CAN总线具有更好的数据通信可靠性、实时性和灵活性,因此应用领域越来越广泛,鉴于以上考虑,本文利用CAN总线传输采集到的数据。

2 系统详细设计

2.1 ADC128设计

ADC128是美国TI公司的一款单5V供电的12位高速、低功耗、8通道同步采样模数转换器。ADC128的控制主要由SCLK、DOUT、DIN和CS完成,其中,SCLK 是AD时钟,控制着转换过程和读出过程,它的频率直接影响着转换速率,本文设计使用的是0.8MHz,保证了50kSPS的转换速率;DOUT是数字信号输出端口,位宽为1,在SCLK的下降沿输出结果;DIN是控制信号,主要用于设置ADC的寄存器用于转换信号的选择,位宽为1 ,在SCLK的上升沿使能;CS是芯片使能信号,位宽为1,只有当CS为低电平时,ADC的AD转换过程才能继续。

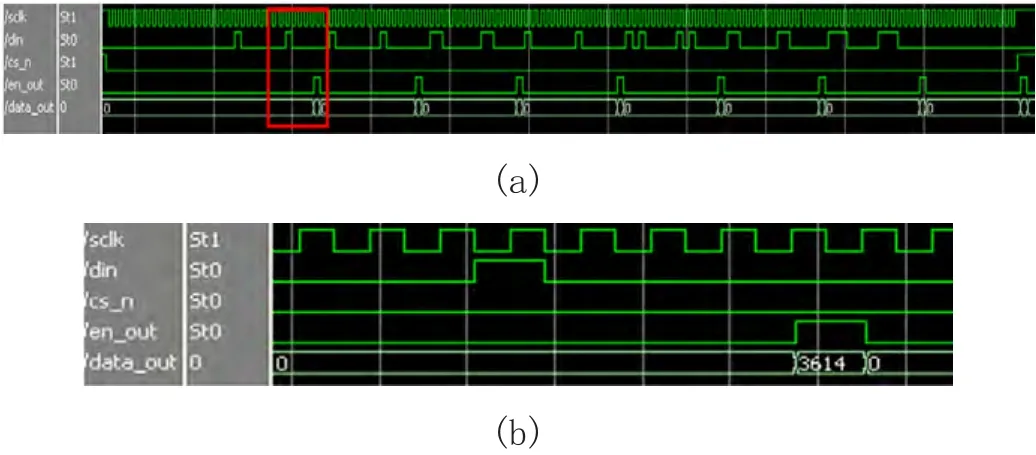

图2所示为ADC128采集8路数据,经过串并转换得到12位并行数据的时序仿真波形。在CS为低时,Din用于对输入模拟通道进行选择,本设计从0-7依次累加,完成8路数据的采集。ADC128在设计时需要注意的是,它是延时输出器件,即第0个过程选择的数据,在第1个过程数据才输出,所以,一次数据周期总共的转换过程为9个,即第7个数据选择完成后,还要加一个读出周期,这样才能将输入的8路数据完整的采集出来。

图2 ADC128采集8路数据仿真波形

2.2 数据整形

由于ADC128每次输出的数据是12bit,而CAN总线的数据帧格式是8bit,因此,为了传输方便且不浪费带宽,我们将ADC128输出且经过串并转换过的数据进行了处理,其思路是数据拼接,例如取第一个数据的高8位输出给CAN,再将第一个数据的低4位和第二个数据的高4位组合输给CAN,把第二个数余下的8位作为CAN的第三个数据,如此处理之后,就实现了ADC128和CAN总线之间数据格式的匹配,不会造成数据的丢失,同时充分利用了CAN总线的带宽,不会造成浪费。

但是,数据拼接后,在数据传输过程中给数据的识别带来了一定的影响,因为CAN协议一次只能传输8个字节的数据,而ADC一次输出的数据转化成8位数据需要12字节,因此,整个采集传输过程就变为了一个数据流,即:无法区分什么地方是数据开始,什么地方是数据结束。为了解决这个问题,我们采取了添加数据标识的方法,即每包数据的开始用0x55标识,而一帧数据结束则用0xAA标识,这样,数据解析单元就可以根据这两个标识码,将其中间的数据提取,并按照拼接规则解析即可。

2.3 CAN总线设计

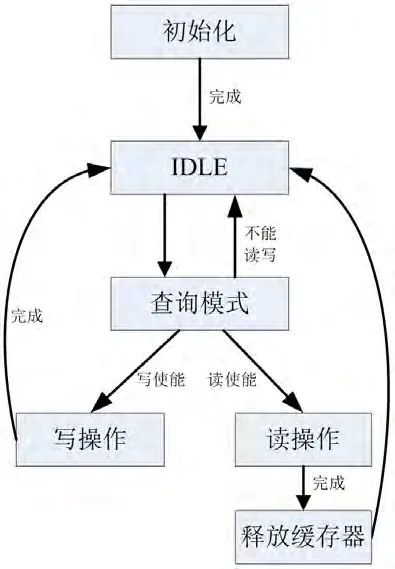

CAN总线的操作主要是通过对CAN总线控制器—SJA1000进行操作来完成, SJA1000的操作主要分为三个步骤:初始化、数据发送和数据接收,如图3所示。

图3 SJA1000控制流图

2.3.1 初始化过程

在SJA1000上电后,首先进行硬件复位,即给reset管脚一个低电平,并且要持续100ms的时间,再将该信号抬高,完成硬件的初始化。然后进行软件复位,即进行寄存器的初始化以完成特定的功能,由于本设计使用的是BasicCAN模式,因此主要是对以下寄存器进行赋初值:控制寄存器、命令寄存器、状态寄存器、中断寄存器、验收代码寄存器、验收屏蔽寄存器、总线定时0、总线定时1、输出控制寄存器和时钟分频器。其中,验收代码寄存器和验收屏蔽寄存器主要用于标识码的确认;总线定时0、总线定时1用于总线传输速度的设定,最大总线长度越长,传输速度越低;输出控制寄存器用于设置总线输出驱动方式。

软件的初始化本质上是对SJA1000的特定寄存器进行写操作,但是前提是要在复位模式下进行,即写之前先要设置模式寄存器的RM为1使SJA1000进入复位模式。SJA1000的初始化过程的时序仿真如图4所示。在ALE的下降沿将寄存器打入,在WR的上升沿将数据写入,完成对SJA1000的初始化。

图4 SJA1000初始化过程

2.3.2 发送数据

SJA1000的数据发送和初始化类似,也是将要发送的数据写入SJA1000。但是SJA1000在发送数前,一般先检查状态寄存器的3个状态位:

1)接收状态位(SR.4):如果目前SJA1000正在接收信息,则不能发送,至少等到本次接收完毕才能申请发送;

2)发送状态位(SR.3):检查SJA1000是否正在发送信息,如果正在发送,则需要等一次发送完成才能启动新的发送任务;

3)发送缓存区(SR.2):只有该缓冲区处于释放状态时才能发送信息。

当以上3个寄存器满足写要求时,开始SJA1000的写操作。因为BasicCAN一包数据由10个字节组成,因此,一包数据的发送要连续对10-19共10个寄存器进行连续10次的数据写入,其中,前两个字节为描述符,分别定义了识别码、数据类型和数据长度。因为,我们在验收代码寄存器设置了相应的代码约定,因此,描述符的第一个字节要和设置的代码完全一致才能发送成功,同时,验收代码位和信息识别码的高8位相等且与验收屏蔽位的相应位相或应该为1,因此,验收屏蔽寄存器设置成0xFF的形式。1位的远程发送请求PTR,为1时表示无数据,为0时根据数据长度确定后面的数据,数据长度DLC,有8、4、2、1四个选项,数据的长度位设置的是要发送数据的长度。接下来的8个字节用于存放数据。这样,一个完整的CAN数据帧就完成了,使能发送寄存器CMR.0完成数据帧的发送。相应的时序仿真波形如图5所示:

图5 SJA1000写数据时序仿真波形

2.3.3 接收数据

相比发送过程,接收过程要相对复杂一些,有些文献使用了查询方式进行,即接收缓存器RXFIFO中有数据时,接收缓冲标志位RBS为1,这时就可以进行读操作,但是,这种方式要不停的查询该位以判断何时进行读操作,因此,实际操作过于麻烦。本文设计将SJA1000的/INT管脚作为外部触发条件,即当系统捕获到/INT的下降沿时,表明有中断,再查询是不是数据中断,是表明接收缓存器RXFIFO有数据存在,开始读取数据。这样的设计避免了不停的查询,因此,简化了设计。其中,SJA1000的查询操作是将需要查询的寄存器送入地址A7-A0,然后读取数据D7-D0,根据D7-D0的值判断下一步的动作,当然此处仅需发送一包数据即可,如果要查询多个寄存器,就一次发送多个数据包。

发送缓存器的地址是10-19,而接收缓存器的识别码、远程发送请求位和数据长度码同发送缓冲器的相同只不过地址是20-29。读一般也要连续进行10次,前面2包是描述符,包括11位的识别码,1位的远程发送请求PTR和数据长度DLC信息。由于本文系统约定了数据长度是8字节,因此,后面8字节全是有效数据。读完一包数据,需要释放缓冲区,返回空闲状态,即使能寄存器CMR.2,为下一包数据的接收做准备。

3 试验结果与分析

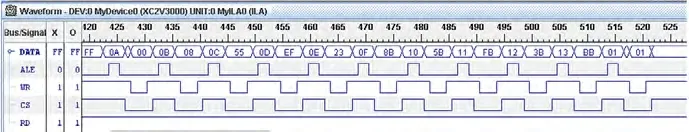

本文系统使用了模块化设计思想和自顶向下的设计思路,利用VerilogHDL语言、在Xilinx公司的ISE10.1软件环境下实现,硬件平台选用的是xilinx公司的XC2V3000。为了验证本文系统的数据采集效果,我们从两方面进行说明。一方面,3.1和3.3节的时序仿真波形从理论上证明了设计的正确性;另一方面,本文系统设计完成后,进行了芯片烧写,并对实际数据进行了采集,为了直观,我们使用的是Xilinx自带的Chipscope进行观测,结果如图6所示,表示的是将ADC128采集的一包数据发给SJA1000的情况,数据以0x55开始,后面紧接采集到的数据,进一步证明了设计的可行性和正确性。

图6 发送采集数据过程截图

4 结束语

本文设计仅采用一片FPGA完成了对8路模拟数据的采集、数据格式的转换和数据的CAN总线传输,使传统复杂的系统得到简化,同时采用了流水线设计的思想,充分发挥了FPGA的并行设计优势,使整个过程做到了实时处理,相比传统的基于单片机的设计,更加灵活,并且移植更加方便,从而大大提高了效率。目前,该系统已经成功应用到某工业现场。另外,虽然本文设计用于采集8路模拟信号,但是,我们对整个系统分析可知,只要修改一下采集对象和路数,该系统就可以应用到其它数据采集系统中,具有较好的通用性。

[1]仲建锋,胡庆生,孙远.基于FPGA的多路高速串并转换器设计[J].电子器件,2008, 31(2):657~660.

[2]张贵清,朱磊,颜露新,等.基于FPGA的多路同步实时数据采集方案设计与实现[J].测控技术 ,2005,24(12):26~29.

[3]储成君,任勇峰,刘东海,等.基于FPGA的多通道信号采集电路设计[J].科学技术与工程,2013,13(19):5692~5695。

[4]陈彦,张宏伟,林宏宇.基于FPGA的CMOS图像传感器LUPA-4000时序设计[J].航天器返回与遥感 ,2012,33(5):62~67.