基于TMS320DM6437的OSD技术设计及应用举例

曾 凯,郑力新,张 枫

(华侨大学 信息科学与工程学院,福建 厦门 361021)

在工业生产和生活领域中,嵌入式数字视频监控系统得到广泛应用。而在屏显示OSD(On Screen Display)技术可帮助工作人员方便检测工业生产过程状态变化。目前,工业领域实现OSD技术的方法可以利用专业用OSD芯片,如FUJITSU公司的 MB90092芯片,其电路设计简单,但需专门设计软件和硬件;也可以利用附带OSD功能的芯片,如SigmaDesigns公司的EM8511芯片,其不需要专门的硬件设计,使用方便,只是这类芯片目前功能还不够强大,难以工作在信息处理量大和实时性要求高的平台。TMS320DM6437及其系列芯片是当前视频处理系统主流处理器之一,本文阐述了以软件编程方式实现该芯片OSD技术,简单实用,效果优良,很好地拓展了TMS320DM6437的显示模块功能。

1 OSD架构平台

1.1 棒材计数硬件平台

本文以棒材计数平台上实现OSD技术为例,在实现OSD模块信息和视频信息叠加时,要处理的数据量大,为了满足实时性的要求,需要选择一款集成度高,运算速度快的芯片。TMS320DM6437是TI公司推出的定点Davinci DSP处理器,工作主频可达700 MHz,处理性能最高达到5 600 MIPS,含有丰富的外设资源,芯片本身具有OSD功能,这样就不需要增加额外的硬件设计,可以通过灵活的软件编程来实现视频和嵌入的图片叠加,为用户提供简便的观测信息。

棒材计数平台主要由DSP图像处理模块、CMOS图像传感器模块、存储模块(DDR2)和视频输出显示模块组成,硬件平台如图1所示。

图1 棒材计数硬件平台

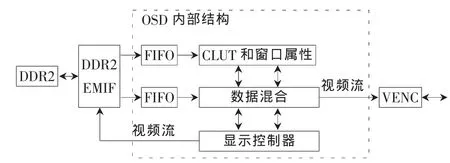

1.2 TMS320DM6437的OSD内部数据传输架构

TMS320DM6437的OSD内部数据传输架构如图2所示。OSD模块从外部内存中读入视频数据,外部内存通常是DDR2,数据经处理转化为YUV格式后送人 VENC。OSD模块可处理两个独立的Video窗口和两个独立的OSD窗口,OSD模块的相关寄存器通过视频解码模块产生的VD信号进行嵌位,来控制显示窗口使能、窗口缩放以及窗口的显示坐标。

图2 TMS320DM6437的OSD内部数据传输架构

OSD模块控制的4个窗口中,主视频窗口VIDWIN0支持乒乓Buffers数据交换,即从内存的两个不同位置读取数据。两个位图窗口(OSDWIN0和 OSDWIN1)能够直接从DDR2中读取RGB格式数据,并支持图像或图标同时显示。位图窗口需要用到的颜色查找表格(CLUT)根据实际给定的位图像素值来决定显示颜色,OSD窗口共有256个CLUT条目和24位YUV颜色空间可用。当OSD位图窗口与视频窗口叠加时,可以通过数据混合调整图像和字符的显示效果。

2 OSD软件设计

2.1 TMS320DM6437的VPBE设置

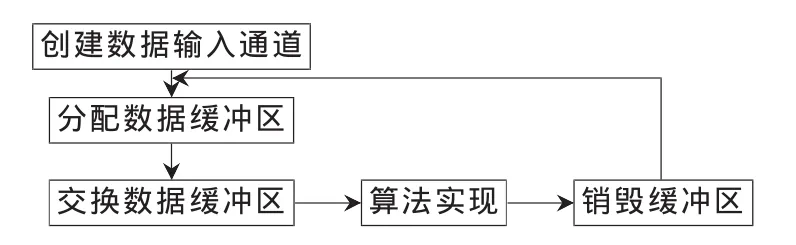

视频后端处理子系统VPBE主要包括OSD和视频编码部分 VENC(Video Encoder Module)两部分。VPBE支持OSD模块将存储在DDR2中的多种显示格式的图像数据混合成一帧,数据格式编排后传送到VENC模块显示。VPBE编程模块的主要流程如图3所示。

图3 VPBE编程模块的主要流程图

以下两个条件满足时VPBE驱动程序有效。第一是在DSP/BIOS中创建一个VPBE驱动。主程序利用函数VENCHandle=FVID_create ("/VPBE0",IOM_INOUT,NULL,NULL,&gioAttrs)打开一个 VPBE0设备,并创建 VENC通道。由于TI设计的GIO驱动模块在DSP/BIOS上使用过程中存在缺陷,应用程序在对驱动程序的缓冲区进行数据处理后不能释放缓冲区,针对这个问题可利用TI提出的FVID视频处理模型,其能够比较方便地分配缓冲区,因此,通过直接调用FVID_allocBuffer()函数和FVID_exchangeBuffer()函数申请分配和交换缓冲区,并在使用后利用FVID_deleteBuffer()函数重新释放缓冲区。第二是设置DSP/BIOS中的硬件中断。VPBE驱动程序的使用过程中,在TCF文件中设置HWI_INT8为1,配置参数为 bios.HWI.instance("HWI_INT8").interruptSelectNumber=1,即VPBE驱动优先级为8,对应VENC每帧图像处理结束后产生事件序列号为32~64之间的事件被中断,这时事件接收器检测到哪里引起了中断。

2.2 窗口显示模式选择

每个窗口可以设置为帧模式和场模式。帧模式的特点是允许每帧图像数据连续储存在DDR2中,图像显示时按照奇偶场进行读取。场模式特点是允许图像数据单独储存在DDR2中,图像显示是根据VENC的工作模式窗口高度。处理芯片DM6437集成了DDR2内存控制器,支持JESD79D-2A标准,并提供32 bit DDR2接口。图像数据存储在DDR2中,当需要VENC连续从DDR2中读取数据时,将OSD窗口设置为连续场模式,对应的寄存器位VIDWINMD.VFFO和OSDWIN0MD.OFF0使能。连续场数据读取模式如图4所示。

图4 连续场数据读取模式

2.3 OSD窗口设计

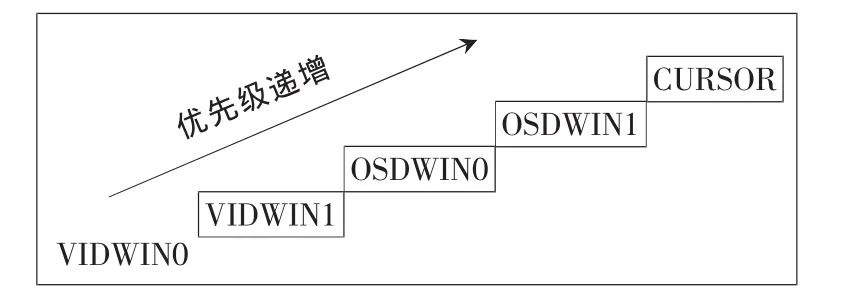

OSD模块支持VIDWIN0/VIDWIN1和OSDWIN0/OSDWIN1 4个窗口画面同时显示,并通过对应的寄存器设置OSD工作模式。OSD窗口显示优先级如图5所示。

图5 OSD窗口显示优先级

本文需要用到VIDWIN0和OSDWIN0将视频图像与文字字符叠加,VIDWIN0用于实时显示采集的棒材图像,OSDWIN0将棒材计数结果叠加到VIDWIN0窗口画面。

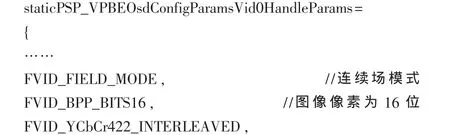

(1)VIDWIN0 窗口设置

CMOS图像传感器采集到的图像经TVP5150转化为YUV格式数字信号,并存储在DDR2中,视频后端处理子系统VPBE将数据从DDR2中读出,并通过VIDWIN0窗口显示。由于VIDWIN0对应寄存器配置参数的设置封装在DM6437自带的psp_vpbe.h头文件中,调用结构体PSP_VPBEOsdConfigParams{}可以配置 VIDWIN0窗口的工作模式、图像的格式以及图像在窗口中显示位置。例如:

本文通过软件编程的方式实现VIDWIN0窗口配置,在对结构体参数设置后,通过调用FVID_create()函数创建vid0Handle通道,FVID_alloc()函数为通道分配存储空间,调用FVID_queue()函数将要显示的数据从通道传输到VIDWIN0窗口显示。其具体软件编写流程图如图6所示。

图6 软件流程图

(2)字符数据格式

本文OSD显示技术中使用的字符(如数字0~9,字母a~z,以及一些常用符号)需按 12×16格式分割成块,把这些数据固化在Flash或者ROM中。在实验中用到的字库无法直接在DSP中读取,需将所用的汉字转换为位图形式并进行保存。DM6437可以采用32位数据处理,为了便于编程和数据读取,将位图图像的分辨率转换成192×32,取 32位的整数倍,如图 7所示。

图7 文字字符显示图

对于数字字符,由于棒材计数是一个动态的过程,因此OSD窗口数字显示根据棒材计数的算法运行结果的返回值确定,设置数字位图图像的分辨率为32×32。位图图像转换为数组形式后存储在Flash中,为了节约存储空间,要求将图像数据转换成RGB565格式。数字如图8所示。

图8 数字显示图

(3)OSDWIN0 窗口设置

OSDWIN0用于显示RGB565格式的字符和数字图片,对应的寄存器配置参数的设置封装在DM6437自带的psp_vpbe.h头文件中,配置参数的流程与配置VIDWIN0步骤一样,调用结构体PSP_VPBEOsdConfigParams win0Params{}设置相应寄存器值,结构体中包含的参数需包含叠加的图片和文字的显示属性,如混合模式、透明度和颜色等。

(4)VGA显示驱动设计

本文通过修改PSP文件的相关参数设计VGA的显示驱动,基于 PSP(Platform Support Package)上的驱动程序可以直接实现S端子显示和LCD屏幕显示,同时驱动程序支持VENC编码器的连续场输出模式,但是程序存在缺陷不能直接用于VGA显示,因此需要在驱动中增加VGA的显示驱动程序。TI官方提供的基于PSP的视频驱动程序建立在实时操作系统DSP/BIOS上,总共分为IOM层、DDC层和CSLR层3层。

本文利用的OSD技术产生的叠加效果通过VGA显示,VPBE模块为VGA图像显示提供了接口,VGA接口有3路基本输出信号,分别用来显示RGB 3个分量。VPBE模块提供的模拟接口拥有4路的视频DAC信号,通过设置寄存器DACSEL来选择所需要的3路信号,寄存器DACSEL上的对应关系为:DAC_A位控制输出R模拟信号,DAC_B位控制输出G模拟信号,DAC_C位控制输出B模拟信号,同时DM6437通过I2C总线接口输出行同步信号HD和列同步信号VD,这5路信号组成了VGA接口输出信号。

在DDC层中修改一个PSP声明,并添加LLC_setVGAdisplay()显示函数对5路信号使能,LLC_setVGAdisplay()代码如下:

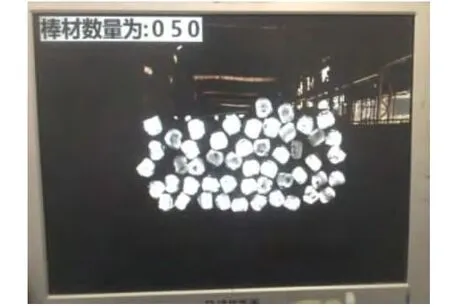

(5)运行效果

VGA 5路信号使能后,程序运行后OSD叠加技术的最终效果如图9所示。

图9 OSD叠加技术的最终效果

本文利用TMS320DM6437芯片自带的OSD模块,通过软件编程实现OSD叠加技术,并以在钢铁生产中的棒材计数结果与视频叠加为例,OSD界面上的汉字、数字或其他特殊字符可根据工作人员的要求修改,并在窗口任意位置动态显示,其设计原理具有通用性。OSD模块实现的动态棒材视频图像与棒材计数结果叠加,方便了人机对话,可以应用在工业生产实践中。

[1]TI.TMS320DM643x DMP video processing back end(VPBE)[Z].2007.

[2]合众达.SEED-DEC6437用户指南[Z].2008.

[3]TI.How to use the VPBE and VPFE Driver on TMS320DM643x devices[Z].2007.

[4]TI.TMS320DM643x DMP inter-integrated circuit (I2C)module user′s guide (Rev.A)[Z].2007.

[5]TI.TMS320DM643x DMP DDR2 memory controller user′s guide (Rev.B)[Z].2007.

[6]TI.TMS320C64x+image-video processing library programmer′s reference[Z].2007.