一种软件双环锁相同步方法研究

张 东, 顾祥龙, 孟君泽

(1中国人民解放军63850部队 白城 137000 2中国人民解放军装备学院 北京 101416 3中国人民解放军65044部队 大连 116000)

引 言

在分集接收系统中,为了实现最大的输出增益,在信号合并前必须先完成同频同相调整,使各路信号的瞬时相位和频率达到一致。双环锁相同步法,由于实现简单、性能稳定,被广泛应用于分集接收系统中[1]。本文在前人研究锁相同步的基础上,研究软件双环锁相同步方法的实现[2]。用软件实现的双环锁相同步方法,可以更充分有效地利用数据,避免硬件实现的研发周期长、成本高等缺点,更具备灵活性与通用性。文中介绍了双环锁相同步中的差模环与共模环原理,并进行了仿真分析,论证了软件双环锁相同步方法的可行性。

1 软件双环锁相同步技术原理

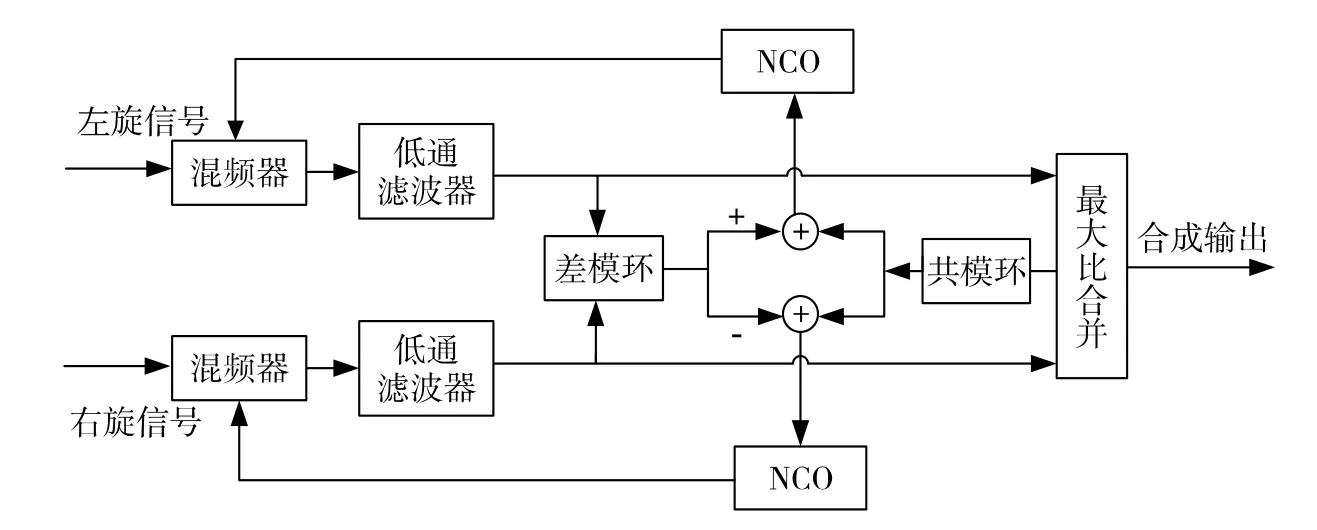

双环锁相结构由差模环和共模环构成,差模环的作用是完成左、右旋两路信号的同步,共模环的作用是消除信号的频率偏移。双环锁相同步原理如图1所示。

该方法可有效地完成两路信号的同频同相[1],下面分别对双环锁相中差模环、共模环的实现展开研究。

图1 双环锁相同步原理

1.1 差模环原理

差模环的原理如图2所示,两路信号分别经过正交下变频后,由低通滤波器将零中频以外的数据滤除掉,然后对四路信号进行互相关运算(见图3),将计算出的I、Q信号进行反正切求出两路的相位差,所得的相位差值送入环路滤波器,再将滤波器输出以相反的极性送到各自通道的NCO中,使两路信号的相位向中间靠拢,进而达到两路信号相位同步的目的。基于互相关的同频同相方法原理如图3所示。

图2 差模环原理

根据图3所示,对算法进行以下推导[3]:

假设接收到的两路信号分别为SL(t)和SR(t),由于输入基带事后处理设备的信号已经经过自动增益控制(AGC)调制,因此可设两路信号幅值均为A,有

图3 互相关运算

式中,ωL、ωR分别为左、右旋信号的中心频率,θL、θR分别为左、右旋信号的初始相位,nL、nR分别为叠加在左、右旋信号上的高斯白噪声,Φ代表调制数据信息。根据Φ物理意义不同,接收信号可以代表BPSK、QPSK、FSK、FM等各种信号形式。

左、右旋本地信号同相支路可表示为

正交支路为

式中ω为本地载波频率,在这里认为本地载波初始相位为零。

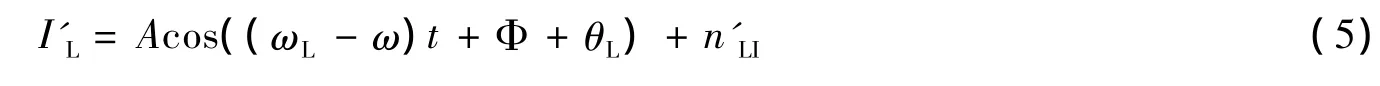

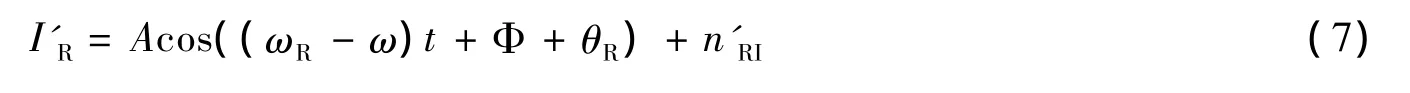

左旋信号经过下变频并滤波后,同相信号变为

正交信号为

右旋信号经过下变频并滤波后,同相信号变为

正交信号为

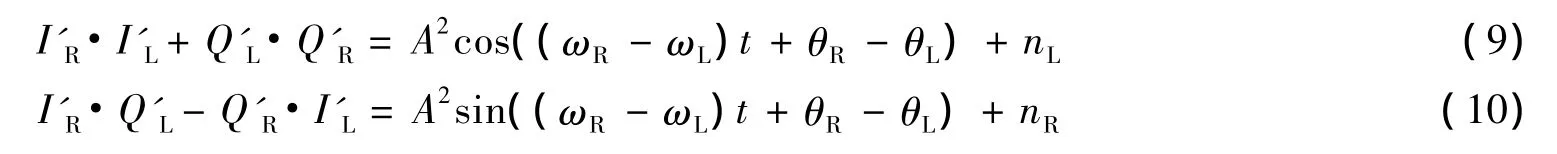

对左、右旋两路信号作互相关,可得

式中,nL、nR为噪声。

将式(9)、式(10)联立,二者相除,求出反正切的值,则误差分量将含有(ωR-ωL)t+θR-θL的信息,再将该信号送入环路滤波器,得到控制信号,分别控制左、右旋信号的NCO,使得(ωL-ω)t+θL和(ωR-ω)t+θR相等,从而达到左、右旋两路信号同频同相的目的。而且,从式(9)、式(10)可以看出这种方法适用于各种类型的调制信号[4]。

1.2 共模环原理

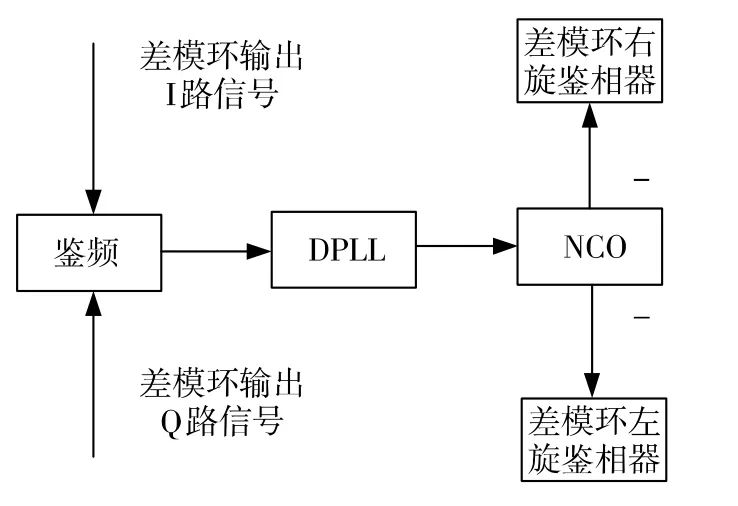

在事后基带数据处理的过程中,极化分集合成主要是完成两路信号的同频同相以及最大比合并[5]。共模环的作用是消除多普勒频移以及载波的频率偏差[6]。在两路信号经过差模环的同频同相并相加后,进入共模环。共模环路利用二阶锁相环的低通特性,将缓慢变化的频偏信号保留,并将其作为相位误差信号送入NCO,最后送入混频器闭环。NCO跟踪输入信号的频率,锁定误差信号频率,并消除频偏分量[7]。共模环原理如图4所示。

DPLL中环路滤波器的参数如下

其中,Ts=1/fs,fs为系统采样频率,ωn为自然频率,η为阻尼因子。

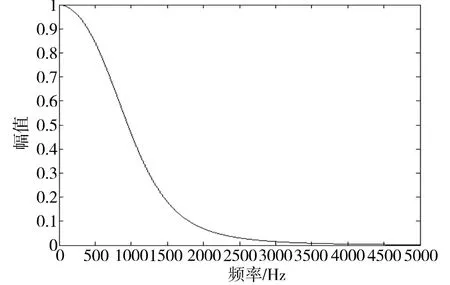

DPLL在该参数下的幅频特性曲线如图5。由于在事后处理的过程中还要对高频频偏进行处理,因此在共模环部分能够消除缓慢变化的频偏分量即可。从图5中可以看出DPLL可将较缓慢变化的低频频偏分量滤除,产生的误差信号即为频差。

图4 共模环原理

图5 DPLL幅频特性曲线

2 仿真分析

2.1 差模环仿真

根据图2的原理,进行了差模环在Matlab下的仿真,输入信号的采样率fs=56MHz,载波频率fc=70MHz,码速率Rb=1.28Mb/s,频率分辨率为100kHz。信号类型为FM调频信号。混频器采用两个乘法器来实现正交下变频,并采用低通滤波器进行滤波。

图6为两路信号输入相差为π/4、频差为0时相位反馈信号的幅度值。图6幅度己对π进行单位化,根据差模环原理,两路信号各自得到π/8的反馈量,总相位差调整量为π/4,实现了两路信号的同相调整。

图7为当两路信号相差为π/4、频差为10kHz时相位反馈信号的幅度值。相位反馈信号斜升代表频率差的存在,说明差模环能够跟踪相位频率的差值,从而完成同相调整。

图6 相位差为π/4、频差为0时相位反馈示意图

图7 相位差为π/4、频差为10kHz时相位反馈示意图

通过实验论证和分析可以看出,互相关法的差模环能够有效地使左、右旋信号同步,起到消除两路相差频差的作用。

2.2 共模环仿真

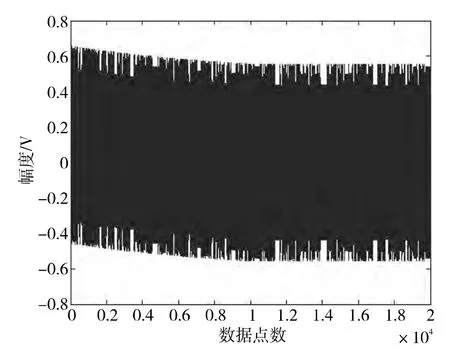

经过共模环处理前后的反馈信号波形如图8、图9所示。

图8 频偏未消除时反馈信号仿真图

图9 频偏消除后反馈信号仿真图

图8 为没有经过共模环作用时的鉴相器输出,图中码型为带有直流偏移的码序列,所以其码型并不关于幅值为0的轴线对称,码型幅值在-0.4V~0.6V之间。图9所示为共模环作用后鉴相器误差传递函数输出,可见其直流偏移量被抑制,码型逐步关于幅值0轴对称,码型幅值在-0.5V~0.5V之间。由此可以看出,在共模环作用后频偏已被消除。

2.3 双环锁相同步仿真

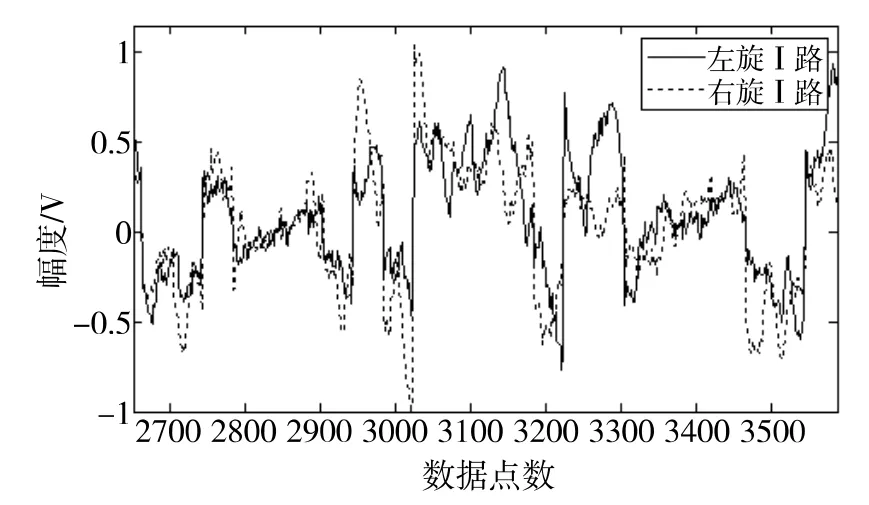

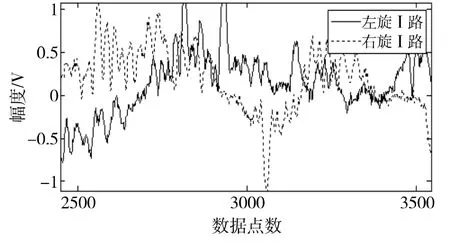

为了验证双环锁相结构的有效性,将C语言程序处理过的数据载入Matlab中,对输出数据进行绘图。数据格式分别为BPSK和FM信号,采样率为56MHz,载波频率为70MHz,频偏为100kHz,测试数据为基带记录设备回放数据。为了明显看出同步效果,各取一段测试数据。BPSK信号的Ⅰ路同步效果对比图如图10、图11所示。

图10 BPSK左、右旋Ⅰ路信号(未同步)

图11 BPSK左、右旋Ⅰ路信号(已同步)

BPSK信号的Q路同步效果对比图如图12、图13所示。

图12 BPSK左、右旋Q路信号(未同步)

图13 BPSK左、右旋Q路信号(已同步)

由图10~图13可以看出,对于BPSK信号I、Q两支路都能较好地完成信号同步。从图10、图11的对比中可以看出,在两路信号相位差较大时,需要有数十个数据点的相位跟踪。在图12中左旋Q路信号较弱的情况下,双环锁相结构仍能较为有效地完成两路信号的同频同相。

FM信号的I路同步效果对比如图14、图15所示。

图14 FM左、右旋Ⅰ路信号(未同步)

图15 FM左、右旋Ⅰ路信号(已同步)

FM信号的Q路同步效果对比如图16、图17所示。

由图14~图17可以看出,对于FM制式的信号,软件双环锁相结构仍可以有效地完成两路信号的同频同相。

图16 FM左、右旋Q路信号(未同步)

图17 FM左、右旋Q路信号(已同步)

3 结束语

本文对软件实现的双环锁相技术进行研究,双环锁相结构由基于互相关运算的差模环以及基于DPLL二阶锁相的共模环构成。从仿真结果看出,软件实现的双环锁相结构的性能满足需求。这种双环锁相结构不受信号类型的限制,可以在高性能计算机上灵活实现,随着高性能计算机平台的发展,软件实现的双环锁相同步方法将有更强的通用性、适用性。

[1]张 芳.PM体制下极化分集合成技术的研究[D].燕山大学工学硕士学位论文,2004.

[2]陈精杰.一体化接收机关键技术研究[D].兰州大学,2011:37~40.

[3]董 齐.基于FPGA的极化分集研究[D].哈尔滨工业大学,2006.

[4]罗 涛,佟学俭,乐光新.无线衰落信道下的分集接收技术[J].无线通信技术,2001,(4):25~28.

[5]郑立岗,吕幼新,等.PCM/FM遥测系统中用于去除多普勒频率和载波频偏的新方法[J].信号处理,2004,20(3):236~240.

[6]宋伟先.软件锁相环研究与接收机的设计[D].哈尔滨工程大学,2009:12~14.

[7]Balaban P,Salz J.Optimum Diversity Combining and Equalization in Digital Data Transmission with Application to Cellular Radio[J].IEEE Trans.on Communications,1992,40(6):885 ~894.