基于Basys开发板的VGA显示控制设计※

徐彬,詹华群

(江西科技师范大学通信与电子学院,南昌330000)

引 言

如今随着液晶显示器的出现,越来越多的数字产品开始使用液晶作为显示终端。基于VGA标准的显示器仍是目前普遍使用的显示器。若驱动此类显示器,需要很高的扫面频率,以及极短的处理时间。正是由于这些特点,所以可以用FPGA来实现对VGA显示器的驱动。

虽然VGA专用芯片具有更稳定的VGA时序和更多的显示模式可供选择,但设计和使用VGA显示控制更具有以下优势:

①使用芯片更少,节省板上资源,减小布线难度;

②当进行高速数据传输时,具有更小的高频噪声干扰;

③FPGA(现场可编程门阵列)设计VGA接口可以将要显示的数据直接送到显示器,节省了计算机的处理过程,加快了数据的处理速度,节约了硬件成本。

1 系统整体设计框架

VGA显示控制整体设计方案框图如图1所示,将其划分为电源模块、时钟电路模块、VGA接口模块、字库/图库模块、显示器等。再利用Verilog语言对FPGA的各个子模块进行编程设计,同时对各个子模块的功能分别进行调试,最后将所有调试成功的子模块并在一个顶层模块下,最终实现VGA显示控制设计。

图1 VGA显示控制整体设计方案框图

2 VGA显示控制的FPGA实现

2.1 存储功能模块

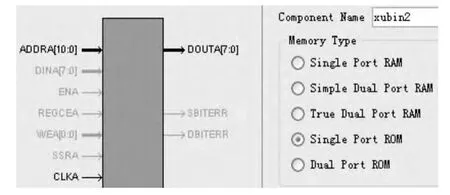

存储功能模块的主要功能是存储图片色彩信息,其存储媒介为FPGA内部的硬核块RAM,块RAM是以硬核的方式内嵌到FPGA芯片中的,不占用芯片的逻辑资源,是FPGA芯片内部的一种宝贵资源。FPGA内嵌的块RAM组件可配置为单口RAM、双口RAM、分布式ROM、块ROM和先进先出存储器FIFO等存储结构。

本文只进行图片的显示,所以使用单口的块ROM存储图片信息,如果想实现更复杂的设计,如文字的滚动显示、图片的动画显示等,可以使用双口RAM进行设计。由于图片信息比较大,而BASYS板子上的资源又有限,这就要求图片不易过大。搜集的各种资料和不断的实验结果表明,大小在8 192字节内的图片是可以显示的。这里第一幅图选用自己的名字徐彬。图片信息大小为:63×32×8=16 128位。第二幅选用江西科技师范大学。图片信息大小为120×50×8=48 000位。寻找到图片后,利用Xilinx ISE中的IP核生成工具Core Generator生成单口ROM,如图2所示。

图2 单口ROM图

将要显示的图片信息存储到块ROM中。第一幅图片选择数据宽度为8,深度为2 016的ROM。第二幅图片选择的ROM数据宽度为8,深度为6 000。在工程里使用IP核生成工具生成单口ROM,在生成过程中处理好ROM的数据宽度和深度。块存储的时候,需要加载的是一个.coe文件来初始化存储器的内容,这时候需要用到Image2Lcd软件,取图片的色彩信息保存为.coe文件初始化到ROM中。

2.2 VGA控制模块

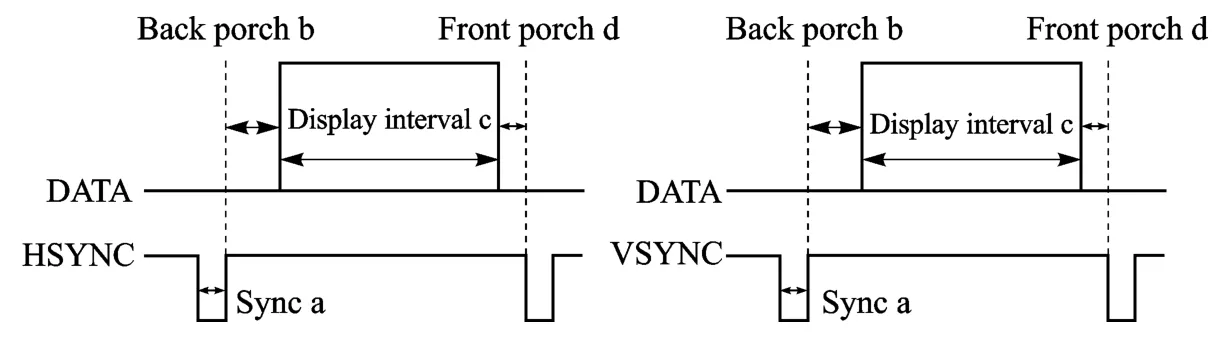

时序的驱动是设计VGA显示控制的一个重要问题,关系到设计是否成功。时序若不正确,则不能够正确地显示,有时候甚至还会损害显示设备。因此,时序的设计必须严格遵循VGA的标准,在此设计中使用的分辨率为800×600,要求像素时钟为50MHz。

图3 VGA时序图

根据VGA时序的标准行、场同步信号有4种状态,时序图如图3所示,具有同步脉冲信号(Sync)、显示后沿信号(Back porch)、I显示的时间间隔(Display interval)、显示前沿(Front porch),这4种状态具有很清晰的时序规律。设置两个计数器,模为1056的行计数器和模628的列计数器,系统时钟为50MHz用来控制行计数器,通过计数器的值来控制行信号HSYNC,然后在通过行信号HSYNC来控制列计数器,通过计数器的值来控制列信号VSYNC。

2.3 ROM读取控制模块

ROM读取控制模块是VGA显示设备和存储数据信息ROM之间的通道,为了使VGA显示设备能够准确地显示图片信息,必须严格遵循显示设备的扫描规律,产生相应的显示信息。

首先,在程序中通过两次例化分别调用存储在FPGA内嵌ROM中的两幅图,然后在程序中通过坐标定位将图片显示到想要显示的区域。本文的两幅图片分别将显示区域定在从屏幕的(500,350)坐标到(563,382)坐标区域内从屏幕的(400,350)坐标到(520,400)坐标区域内。

因为设计实现的功能是利用键盘上的按键对两幅图进行切换,所以不必担心显示区域有重叠而产生覆盖现象。在图片的显示过程中,每当坐标计数器刷新到图片显示指定区域内时,就要判断相应扫描点所包含的图片信息,将其赋给RGB进行色彩的显示。

3 PS2显示控制器的FPGA实现

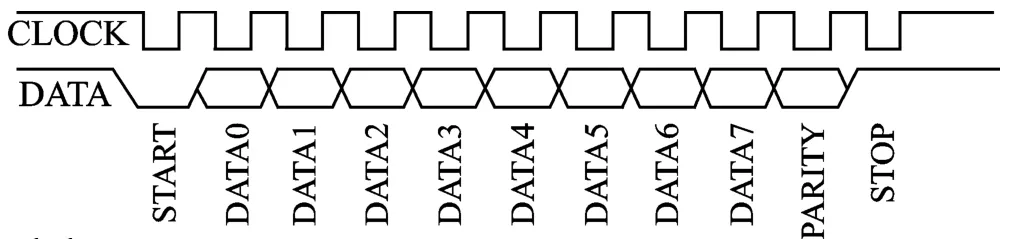

3.1 PS/2传输协议

PS/2键盘到主机单向通信的原理如下:PS/2主从设备之间采用双向同步串行的机制进行数据传输,从设备的晶振时钟信号作为通信过程中的同步时钟信号,键盘发送到主机的每一帧数据包含11位二进制代码,每位数据在键盘时钟的下降沿被主机从数据线上读走。PS/2传输协议如图4所示。

图4 PS/2传输协议

这11位数据的含义分别是:START为起始位,总是为0,以作设备同步之用;8个数据位DATA0~DATA7低位在前;PARTTY为奇校验位;STOP为停止位,总是为1。正如键按下就会有扫描码(通码)发往主机一样,只要键一释放,就会有扫描码(断码)发往主机。

每个按键都被分配了唯一的通码和断码。PS/2键盘第二套扫描码中,大多数按键的通码只有一个字节,一帧就可以发完,这些按键的断码一般是在通码前面加个F0h,所以这些两个字节的断码就需要两帧来发送。比如G键的通码34h、G键的断码F0h34h,按下G键后,然后松开G键,键盘就会依次向主机发送34h、F0h34h。但此次设计所用到的输入按键是通码有两个字节,断码有三个字节的特殊按键。

3.2 键盘按键控制实现

设计中只用到了两个按键——左键和右键,而且实验只需用左键控制第一幅图片的显示,右键控制第二幅图片的显示。因此,只需要在程序中检测到这两个按键的通码即可,即检测到左键的通码到来即显示徐彬二字的图片,当松开按键时,不需要考虑其断码需要带来某种操作,继续保持第一幅图片的显示。

当检测到右键的通码到来即显示江西科技师范大学的图片,当松开按键时,也不需要考虑其断码需要带来的某种操作,继续保持住第二幅图片的显示。而对其余的按键在本次设计中暂不需要考虑。

4 数码管动态显示控制

4.1 数码管点亮控制

数码管按其段数分可七段数码管和八段数码管,它们的区别在于八段数码管比七段数码管多一个发光的二极管单元,即多一个小数点显示段。按照显示“8”的个数,又可分为1位、2位、4位等数码管。

数码管按发光二极管的连接方式可分为共阳极数码管和共阴极数码管。共阳数码管指将所有发光二极管的阳极连接到一起形成一个公共阳极数码管。共阳数码管应用时,应将公共阳极接到+5V或+3.3V,若某一段的发光二极管的阴极为低电平,则相应段就点亮,若为高电平,则相应段就不被点亮。共阴数码管指将所有发光二极管的阴极接到一起形成一个公共阴极的数码管。共阴数码管应用时应将公共阴极接地,若某一段发光二极管的阳极为高电平,则相应段就被点亮,若某段的阳极为低电平时,则相应段就不被点亮。

可以看出数码管是共阳极的4位数管码,即给低电平时数码管点亮,如图5所示。

4.2 数码管数字显示控制:

由于所有数码管共用一个段选,为了能够独立显示每位数码管,只能用位选来区分不同的数码管。即每次只将某一位数码管的位选置为有效,其他的数码管位选都无效。此时的段选决定了该位数码管的显示内容,然后在下一时刻,置下一位数码管的位选有效,而其他的数码管位选都无效。依此类推,不断循环往复。

每次位选刷新速度比较快,同时由于数码管自身的余辉特性,使每位数码管在其变暗之前就又会被重新刷新,因此人眼则无法感觉到数码管变暗。如果刷新频率低于一定值,则人眼会感觉到数码管在闪烁。所以,一般刷新频率会在60Hz~1kHz之间,这样多位数码管显示比较理想。

图5 数码管点亮

该设计是在开发板Basys上进行实验,其是共阳极的4位数码管,而在此项目工程中只需使用到1个数码管,所以在动态显示中将其他的3位数码管置1屏蔽不亮。程序如下:

这样即实现了实验所想达到的要求。

以上是对位选的一个介绍,而对于段选,数码管可以显示从0到f这16个字符,只需要分别对0到f进行编码显示。本次设计不需要如此复杂,由于只用到1和2两个数字,因此,对1和2进行段选编码即可。程序如下:

这样即实现了实验所想达到的要求。

5 实验结果

5.1 实验的环境

实验的环境包括:

①开发工具:Xilinx ISE 9.1。

②开发语言:硬件描述语言verilog HDL。

③目标板:Xilinx公司Basys开发板。

5.2 实验结果

如图6、图7所示,屏幕上显示两幅图片,利用键盘,通过控制键盘的左右键实现对两幅图片的切换,并使用数码管显示。当按下左键的时候屏幕出现第一幅图片(徐彬)并且数码管显示为1,当按下右键的时候屏幕出现第二幅图片(江西科技师范大学)并且数码管显示为2。

图6 实验图一

图7 实验图二

实验结果已经达到了预想的效果。如果增加块ROM的容量,则可以显示更大的图片,更改方便,也可以调整图片的显示位置。

结 语

利用FPGA完成VGA显示控制,可以使图像的显示脱离PC机的控制,形成体积小、功耗低的格式嵌入式系统(便携式设备或手持设备),应用于地面勘测、性能检测等方面,具

有重要的现实意义。该技术方案已经在工业现场中有多种实际应用。

本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1] 张亚平,贺占庄.基于FPGA的VGA显示模式设计[J] .计算机技术与发展,2007,17(6).

[2] 刘福奇.FPGA嵌入式项目开发实践[M] .北京:电子工业出版社,2009.

[3] 张明.Verilog HDL实用教程[M] .成都:电子科技大学出版社,1999.

[4] 潘松,黄继业.EDA技术实用教程[M] .北京:科学出版社,1999:262-265.

[5] 基于IP Core的Block RAM设计[EB/OL] .[2013-08] .http://wenku.baidu.com/view/1e6f13e49b89680203d825fc.html.

[6] 夏宇闻.Verilog数字系统设计教程[M] .北京:北京航空航天大学出版社,2006.

[7] 夏宇闻.复杂数字电路与系统的Verilog HDL设计技术[M] .北京:北京航空航天大学出版社,1998.

[8] 王志辉,林水生.基于FPGA的键盘扫描模块的设计实现[J] .集成电路应用,2006,67(5).

[9] 吴蓬勃,张启民,王朝阳,等.基于FPGA的VGA图像控制器设计[J] .东北电力大学学报,2006,26(4).

[10] XILINX ROM使用教程[EB/OL] .[2013-08] .http://wenku.baidu.com/view/22744b4de518964bcf847c93.html