基于有限状态机的短波接收机频谱扫描的设计与实现

王李民,刘卫华,周志文

(1. 92493部队,辽宁葫芦岛 125000;2. 92403部队,福州 350007;3. 海军工程大学,武汉 430033)

0 引言

短波接收机频谱扫描[1]的作用是对目标信号的频谱进行搜索截获,提取信号的特征参数,从而对敌方的通信信号进行监听。频谱扫描的主要性能指标[2]之一为扫描速度,影响扫描速度的因素包括模拟前端频率合成器的换频时间、AGC的调整时间以及信号分析检测的时间。在数字化短波接收机中,可编程逻辑器件(比如DSP,FPGA等)的应用可大大提高,由于DSP的灵活性所以较适合在数字化结构中起逻辑控制作用。

本文在基于DSP和FPGA的短波数字化接收机硬件平台上设计平实现了满足工程应用的频谱扫描流程,并针对扫频速度难以满足实际工程要求的情况,运用有限状态机的思想合理设计和调用DSP的线程,使得在不影响接收机指标前提下有效提高了扫频速度。

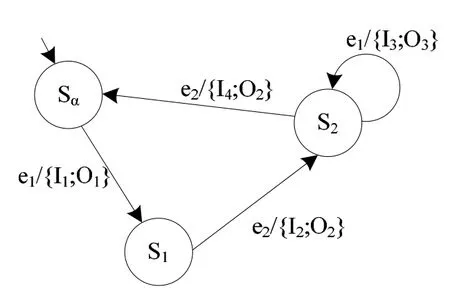

1 有限状态机

图1 有限状态机状态转移图

2 频谱扫描设计方案

在本设计中,数字化短波接收机的硬件平台采用的为中频带通采样结构[3],既可完成解调也可进行扫频,本文只探讨频谱扫描。当接收机工作在频谱扫描状态下时,天线端的射频信号经过前端混频、放大后到模拟中频,设计的中频频率为63.078 MHz。经ADC中频采样后送往FPGA和DSP进行数字处理,DSP将频谱分析的结果最终送给 PC终端进行提取通信信号参数。其中数字处理部分主要包括FPGA进行数字下变频,将I、Q两路信号送给DSP进行FFT频谱分析。频谱扫描的系统框图如图2所示。其中数字处理部分的详细流程图如图3所示。

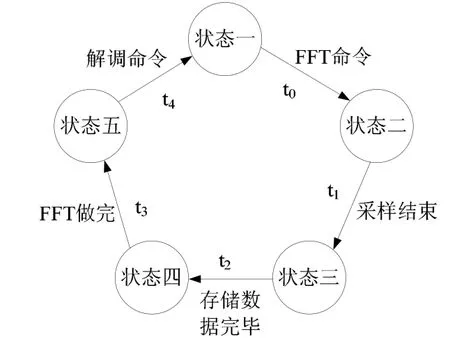

由于在实际工程中要求频谱扫描的速度必须大小200 MHz/s,这就要求在扫描1 MHz的频段范围须在5 ms内完成。然而对接收机而言,每对频谱扫描一次需要完成五个状态之间的切换:1)主控发解调命令,在 DSP中做 AGC;2)主控发FFT命令,FPGA中开始进行采数;3)FPGA中采数结束,DSP读取2*N个I/Q两路数据到FIFO中;4)DSP的FIFO中数据存储完毕,开始做FFT分析;5)FFT分析做完,通知主控通过主机并行接口(HPI,Host Parallel Interface) 取数,并等待主控下发一条命令。状态的切换控制与时间把握决定了扫频速度是否满足指标要求。

图2 频谱扫描系统框图

图3 频谱扫描数字处理部分流程图

在本设计中 DSP以 64 kHz的中断速率与FPGA进行数据交互,DSP通过调用BIOS中的API函数,比如SWI_post来触发软件中断(SWI,Software Interrupt),其处理时间相对于硬件中断(HWI,Hardware Interrupt)比较充裕。因此,主控每次给DSP发送命令时产生硬中断,保证命令的优先级,而信号处理置于SWI层。由于高优先级可打断低优先级的SWI,所以设计了如图4的状态机[4,5,6]。

图4 频谱扫描状态机示意图

如图4中的状态为前述一次扫频的五种状态,外部触发事件可能是为主控发送的命令,也可能为信号处理产生的标志位。当接收到外部触发事件时,转移到下一个状态,两个转移的时间为ti。由前述可知,完成1 MHz的频段扫描时间T=t0+t1+t2+t3+t4,T=≤5 ms。主控在读取DSP的频谱扫描数据时发下一条解调命令使数据和命令并行处理,压缩主控处理的时间。

3 频谱扫描的实现

在本设计中,当工作在接收机的频谱扫描状态下时,DSP为保证整个运算的精度,对FPGA送来的缓存数据进行移位处理,使得进行FFT处理时的数据为满16位。移位后进行加窗处理,然后调用dsp64x.lib中的 DSP_fft16x32(const short*ptr_w, int npoints, int *ptr_x, int *ptr_y)函数,其中ptr_w为输入的旋转因子,为16位浮点型,npoints为FFT点数,ptr_x为输入的正交数据I/Q两路,其存放顺序为I0,Q0,I1,Q1,…IN,QN,N=n points,ptr_y为线性FFT变化的32位数据。

4 效果测试

测试条件为输入中频信号频率为 63.398 MHz,幅度为-22 dBm,进行谱分析时频率分辨率为1 kHz,扫描范围为fIF±400 kHz。DSP将计算的频谱分析结果由 32位线性数转化为 32位Q16格式的dB值,如图5所示为DSP中分析的信号频谱。

在输入单音信号情况下,在 DSP中做 FFT谱分析后捕捉到通信信号(即为图所示的主峰位置)频率63.398 MHz(其中400点的位置为中频频率,右偏为正、左偏为负,所以右偏320点即中频偏移+320 kHz),幅度为-83 dBm(由于为中频输入,模拟前端的放大量60 dB没有计算在内),所以本数字化短波电台的频谱扫描在短波范围内能够有效捕捉到目标信号。

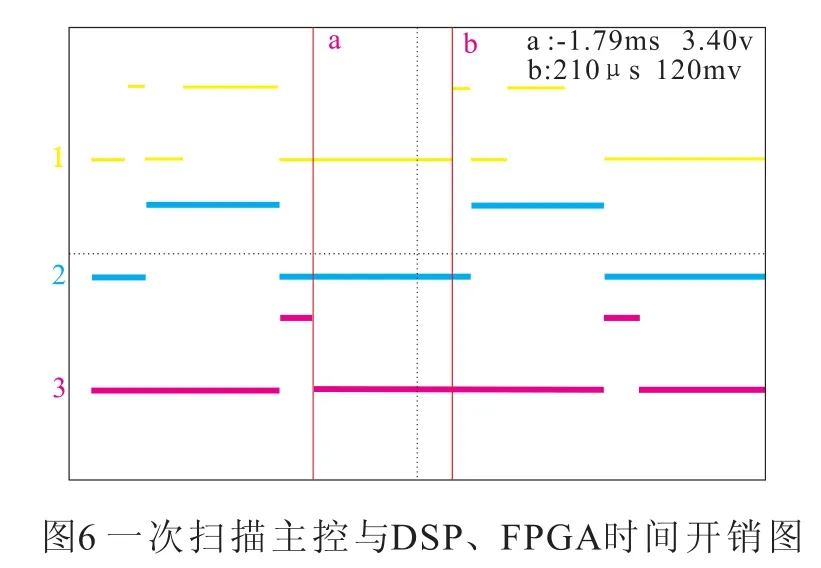

为测试频谱扫描时每个状态的开销时间,采用示波器三个探头的高低电平来捕捉。如图6所示,图中每个探头的高低电平代表1/0状态,比如此时电平状态分别为低高低,则扫频状态为010(2进制),代表DSP正从FPGA中读取采样值。依此类推,由图可知每部分时间开销分别为t0=2 ms,t1=260 μs,t2=510 μs,t3=1.4 ms,t4=500 μs,满足T=t0+t1+t2+t3+t4=4.67 ms≤5 ms。由此可见,将有限状态机运用在接收机的频谱扫描中可有效提高扫频速度,使得满足工程需求。

5 结束语

本文设计和实现了数字化短波接收机中的频谱扫描功能,并针对扫频速度难以满足工程需要的现状,运用有限状态机的思想合理调度DSP的线程,在不影响接收机性能指标的前提下压缩了扫频时间,满足实际应用提出的扫描1 MHz的频段在5 ms以内。

图6 一次扫描主控与DSP、FPGA时间开销图

[1]许军, 汪芙平, 王赞基. 基于软件无线电的数字侦听接收机研究[J]. 电子技术应用, 2007, (8):110-112.

[2]山娟苗. 通信侦察接收机的数字信号处理技术[J].计算机与网络, 2006, (9): 41-43.

[3]远海鹏, 刘峰, 龙腾. 基于射频采样的短波侦察接收机设计[J]. 微计算机信息, 2008, 24(8) : 173-175.

[4]黄新林, 王钢, 刘春刚. 有限状态机在单片机编程中的应用[J]. 哈尔滨理工大学学报, 2008, 13(4) :7-9.

[5]Stoter Arjan, Dalmolen Simon, Drenth Eduard, et al.Real-time context aware reasoning in on-board intelligent traffic systems: An architecture for ontology-based reasoning using finite state machines[J]. ICAART, 2011: 637-642.

[6]Zhu Lin, Wu Zhangguo. Finite State Machine to optimize multi-tasking concurrence technology for real time operating system[J]. Advanced Materials Research. 2011, (383): 2522- 2527.

[7]周先存, 聂尧. 有限状态机在数字调度系统中的建模及应用[J]. 洛阳理工学院学报, 2010, 20(3) :52-55.