基于ARM11的视频无线异步串行传输系统的设计

方晓科,赵 利,伍耀常,黄继聪

(桂林电子科技大学信息与通信学院,广西桂林 541004)

与传统模拟视频系统相比,数字视频系统具有可数字化采集、储存、处理、传输等特点,以及视频质量高、抗干扰能力强等优势,已得到广泛应用。某微波视频传输系统,目前采用模拟技术体制,存在占用带宽较大,可用频点较少,而且相邻信道之间会相互干扰,多系统无法同时工作,在传输过程中容易造成颜色的失真等系列问题,需要进行技术改造,实现数字化。

为了解决这些问题,在原系统保留射频模块和主要功能不变的基础上,需要对系统进行数字化改造。新系统以基于Linux的ARM11多媒体处理平台为核心,实现视频数字化采集和压缩处理以及收发处理,实现彩色LCD视频播放;采用异步串行传输方式,减少开发的难度和周期;采用mmap和多线程方式,优化了视频数据读取的实时性,保证了视频的流畅性。采用中频CP-FSK调制方式,实现高速视频传输。新的数字视频系统以简单的结构、低廉的成本,易实现的技术完成了高速视频的采集、压缩处理、数字传输和实时回放,达到了设计目标。

1 系统方案

1.1 视频采集与发送端方案

保留原有微波发射电路的中频以上部分电路不变,采用中频FSK调制器,以中频频率60 MHz为中心,实现高速FSK调制,调制速率设计为1 Mbaud。FSK调制采用灵活配置的DDS芯片AD9854实现。视频采集与处理模块采用基于ARM11的Linux嵌入式系统,完成图像采集、H.264压缩处理以及视频数据的发送,采用触摸屏显示采集到的视频。视频数据经过压缩和成帧处理后送到FSK调制器,发送方案如图1所示。

图1 视频采集与发送框图

串行数据传输有同步和异步两种方式。同步方式性能好,但收发处理复杂,软硬件成本高,而异步方式实现简单、方便、成本低。综合考虑各种因素,方案采用UART异步串行方式。由于现有嵌入式平台UART所支持的最大速率为115.2 kbit/s,无法满足设计要求,因此采用USB转UART方式,提升串口传输速率。采用单片CP2102实现USB转UART,速率最高可达1 Mbit/s,且具有硬件电路简单,成本较低等特点。

视频采集与处理模块可以采用三星公司的多媒体处理器S3C6410。S3C6410处理器集成了视频处理子系统MPEG-4/H.263/H.264协处理器和ARM内核以及多种外设。开发平台前期选用广州友善之臂计算机公司生产的Tiny6410开发板,支持USB摄像头输入,支持彩色触摸屏,满足各项技术要求[1]。

1.2 视频接收端与回放方案

保留原有微波接收电路的中频以上部分电路不变,采用中频FSK解调器,以中频频率38 MHz为中心,实现速率1 Mbit/s FSK解调。FSK解调采用集成PLL芯片NE564,单片直接完成FSK解调,接收方案如图2所示。

图2 视频接收与回放方案框图

与发送端相同,视频接收与处理模块亦采用基于ARM11-S3C6410的Linux嵌入式系统,完成视频接收和H.264解码处理以及LCD视频回放。

2 硬件设计

2.1 高速异步串行接口设计

串行传输接口采用的USB转UART方式,使用CP2102作为桥接器,外围电路器件较少。S3C6410平台通过USB实现与CP2102数据交换,经过转换后通过UART接口实现异步串行发送。该芯片集成了USB收发器和时钟,USB控制器符合USB2.0规范,内部集成48 MHz时钟发生器,发送缓冲640 byte,接收缓冲为576 byte,波特率最高可达到 1 Mbaud[2]。

2.2 FSK调制电路设计

FSK调制方案采用亚德诺(Analog Devices)半导体公司高性能 DDS芯片 AD9854,其工作时钟可以高达300 MHz,支持FSK,BPSK,PSK,CHIRP,AM 等5 种工作模式[3],串行通信速度达10 Mbit/s。

在FSK模式下,DDS的输出频率是频率调谐字寄存器1、频率调谐字寄存器2和引脚29(FSK/BPSK/HOLD)逻辑电平的函数,引脚29的逻辑低电平选择频率f1,逻辑高电平选择频率f2。DDS系统框图如下图3。

图3 DDS系统框图

AD9854输出的模拟信号经过D/A处理,含有高次谐波分量,需进行低通滤波改善频谱纯度。为此,采用Elliptic函数,设计输入输出阻抗为50 Ω,通带截止频率61 MHz,阻带截止频率80 MHz,阻带损耗60 dB,带内波动为1 dB的7阶的LC低通滤波器。设计中采用了村田公司提供的实际电感电容模型替换ADS仿真设计出的理想模型,并不断对LC参数进行调整后得到了较为满意的仿真结果。滤波器结构和特性见图4、图5。

图4 滤波器结构图

图5 滤波器特性图(截图)

2.3 FSK解调电路设计

采用单片锁相环芯片NE564[4]只需外接少量的辅助电路即可方便构成如图3所示的FSK解调电路,解调波形如图6所示。

图6 NE564解调电路

NE564解调电路的电路参数可设计如下:

NE564的l2/l3端的定时电容CT决定着压控振荡器的固有频率,如式(1)

中心频率为38 MHz时,计算得CT=11.96 pF,那么就可以选6.8 pF和10 pF的可调电容来调节VCO的中心频率。

环路滤波电容的选定:当规定环路的ξ=0.5,芯片供电电压为5 V,且调节2脚电位器使2脚对应电流I2为200 μA后,4、5脚的电容大小,可用如下式子计算得到4、5脚电容约为5 pF。

3 软件设计

3.1 系统软件架构设计

考虑到Linux操作系统的开源、可移植和裁剪,选用Linux-OS平台。在ARM11+Linux平台上,为了实现既定目标,需要开发底层的USB/UART驱动、USB摄像头驱动、LCD驱动和MFC驱动,以及视频采集和回放、H.264硬编解码、异步串行收发、LCD显示与人机界面等应用软件。为保证视频采集、压缩、传输和解码、回显的实时性,采用了多线程方式设计。系统软件架构如图7所示。

图7 系统软件结构图

3.2 视频采集及处理软件设计

3.2.1 视频的采集模块的设计

V4L2(Video for Linux 2)是Linux下开发视频采集设备驱动的一套规范,为驱动程序的开发提供了清晰的模型和统一的接口。应用程序使用统一的API函数来进行操作,视频采集流程如图8。

1)使用open函数只读模式打开摄像头设备文件。接着调用V4L2接口函数设置视频设备采集格式,采集视频分辨率320×240等。相关参数保存在结构体struct v4l2_format fmt中。

2)向驱动申请4个帧缓冲。

3)将申请到的帧缓冲映射(mmap)到用户空间,用户可直接获取帧数据。

图8 视频采集流程

4)使用命令VIDIOC_QUERYBUF将申请到的缓冲区入采集消息队列,系统返回每个缓冲区的首地址和长度,这些参数保存在结构体struct V4L2_requestbuffers中。

5)开始采集视频,当采集到完整一帧视频后,使用命令VIDIOC_DQBUF控制缓冲出消息队列,用户依据地址和帧长度就可以获得采集到的视频数据。

6)将帧缓冲重新入队列,实现循环采集。

S3C6410 H.264压缩处理单元进行H.264压缩编码时要求输入原始数据格式必须为YUV420。本文中USB摄像头采集到的图像数据格式是JPEG,需要进行格式转换。配合使用S3C6410 MFC-JPEG处理单元和Post Processor,可以将采集的图像格式转换成YUV420。

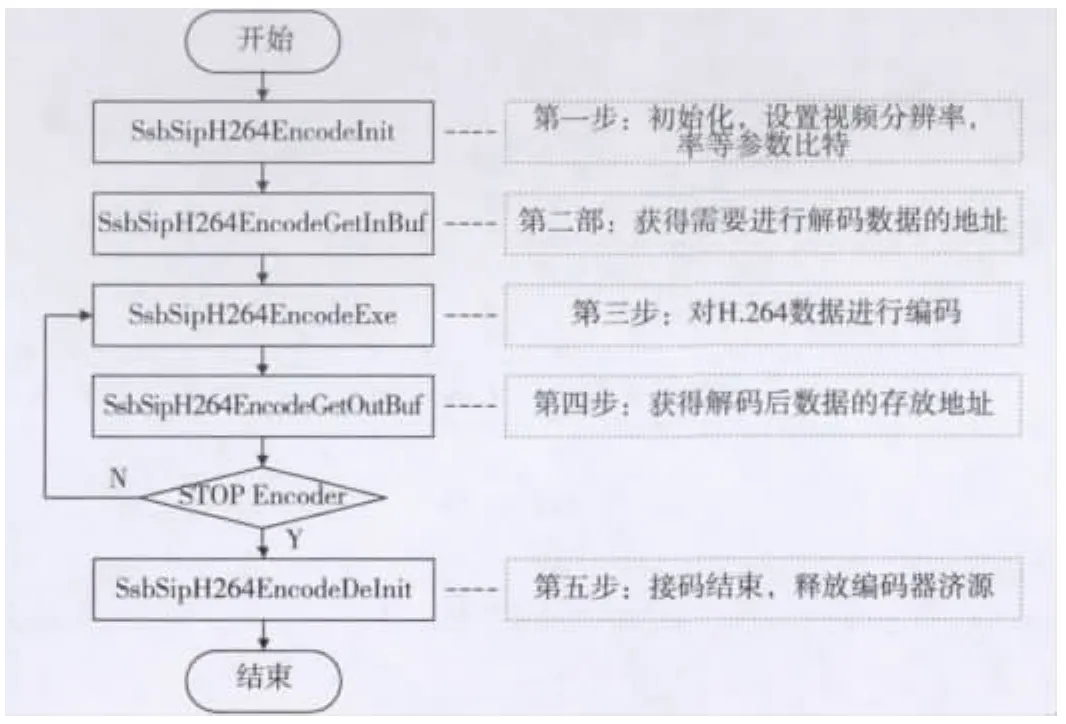

3.2.2 视频的编码与解码

S3C6410编解码单元具有高性能的H.264视频编解码功能,它还能同时处理图像的压缩和解压,也能同时对不同格式的图像进行处理。编解码单元包括BIT处理器和视频编解码模块,BIT处理器能处理比特流和控制视频编解码硬件。编解码单元可以达到全双工720×480,30 f/s(帧/秒)压缩和解压的性能。

1)本文采用H.264编码格式,对YUV420格式的数据进行压缩以减小其传输所需要的带宽。H.264硬件压缩方式,效率高且占用CPU时间少。经测试使用该编码器可以压缩掉90%以上原始数据,编码顺序如图9。

2)H.264视频格式的解码同样采用S3C6410 H.264硬件解码器,解码后的数据格式是YUV420,需要将该YUV420格式转换成RGB格式后才能在LCD屏上预览,流程如图10所示。

图9 H.264编码流程图

图10 H.264解码流程图

3.2.3 视频数据发送与接收帧处理

1)视频数据帧格式

压缩后对数据进行拆分,组帧发送,依据驱动buffer大小,以每次发送1 024 byte对数据进行划分,并定长1 029 byte发送。划分的每一组数据加入一些标志位进行组帧,帧头2 byte,数据大小2 byte,帧尾1 byte,拆分组帧如图11。

图11 数据划分处理结构

在进行数据划分时要考虑两种情况:一是编码后的数据可以分成n整数帧,二是编码后的数据不能整数划分,能分成n帧和余下不足1 024 byte的数据帧m。

2)UART配置及收发流程

串口参数包括控制模式,波特率,起始位停止位数量等参数,串口主要参数设置是在Linux提供的一个标准接口temios中,该接口在头文件temios.h中定义。需要注意的是本文使用串口来传递二进制数据,所以要关闭软件流控,发送模式设置为非规范模式,输入的数据不会被合成一行,不对数据进行加工处理。本设计在此设置串口主要参数如下:

配置好这些关键参数后,串口的运行环境就准备就绪了,这时就可以调用write函数将要发送的数据写入串口设备。

串行数据经过调制过后送如发射机无线传输。处理流程见图12、图13。

图12 发送处理流程

图13 接收处理流程

3)数据接收处理流程

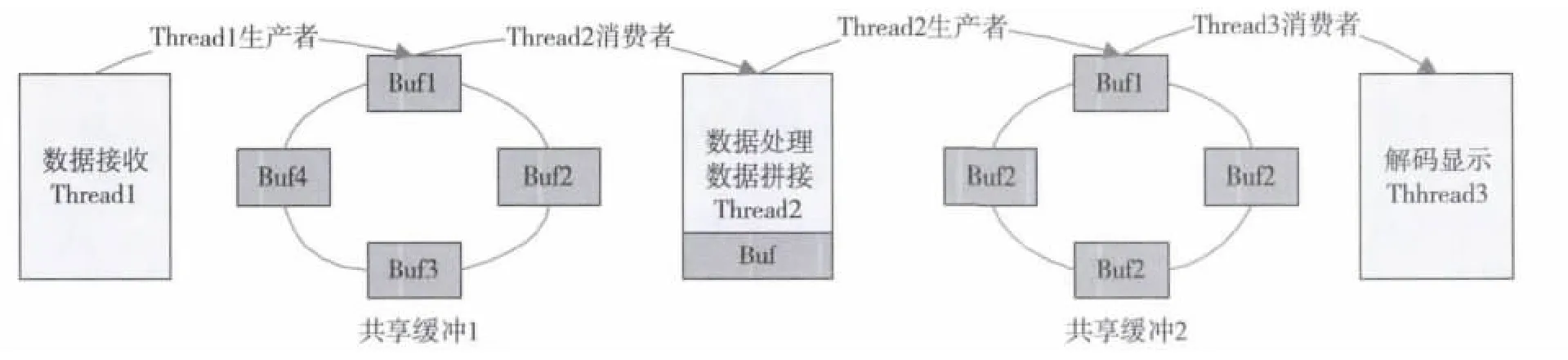

接收机收到数据经过低噪声放大,下变频到中心38 MHz频率和中频放大之后送入解调模块恢复出串行数据。在接收上采用中断方式,当串行接收缓冲区接收到1 029 byte数据通过软中断信号告知应用程序读取,并把数据存在环形缓存区1内。

应用程序读取接收的数据后,通过一些标志位获得视频数据,并将视频流拷贝到一个视频暂缓存区域Buf进行数据的拼接,数据的拼接按照接收顺序和上一帧数据的大小来偏移本次存视频的地址实现。

当完整的接收到一帧视频数据后,将完整的数据转到共享缓冲2,解码线程调用MFC提供的接口函数将接收的视频数据解码并在LCD上显示。因为接收线程,数据处理线程和解码线程是同时运行的,而且共享同一缓冲区进行数据的交互,因此必须采用信号量机制实现同步。进行实际操作之前,进程(或线程)先检查信号量的值,如果当前值大于0,则进行P操作(P操作使信号量值减1),否则休眠,等待其他进程(或线程)在该信号量上V操作(V操作使信号量值加1)[7]。解码操作流程和函数如图14。

图14 数据处理流程

3.2.4 视频数据读取和实时性优化

在数据采集压缩端,主要有两个处理任务,一是采集的视频本地回显,二是将采集的视频数据格式转换后进行H.264压缩并发送,如图15所示。考虑到视频数据流向较为复杂,对实时性要求很高,需要进行优化处理。

图15 数据流向图

因此,视频数据读取和实时性优化采用了如下措施:

1)视频采集时采用mmap方式,其具体功能就是直接将物理内存直接映射到用户虚拟内存,使用户空间可以直接对物理空间操作,相比较在用户控件和内核空间互相拷贝数据,效率更高。

2)视频本地回显,压缩和解码数据流交互采用共享环形缓冲区和多线程机制。在采集视频端主线程负责视频采集和LCD本地回显,子线程实现数据的转换和H.264压缩与传输。在接收端除接收主线程之外,开辟了一个数据拆帧和数据拼接线程,一个解码显示线程,组成了一个类似于三级流水线形式的处理流程,保证了画面的流畅。

4 结束语

采用了高速串行异步通信方式,实现视频的无线传输和接收,硬软件实现较为经济。设计中采用了ARM+Linux平台,可以根据需要进行软硬件裁剪,解调采用了NE564,即可在中频阶段实现数据的恢复,在发送接收端采用了多线程,实时性得到了提高,经系统级联实验测试,在分辨率为320×240情况下,可以较稳定的传输接收并解码显示,色彩保持度较好,平均帧率在10 f/s以上,达到了设计要求。

:

[1]广州友善之臂计算机科技有限公司.Tiny6410硬件手册[EB/OL].[2013-11-05].http://wenku.baidu.com/link?url=k0kJVn5naeD BCnWsMxg8AH5CPowCDZPsEKmbgWhGWcN727EvOdZkxUNhmhyhTJq WGzI3ehrfjzKYT5ZFKypsjDZ66CFoNCpMPdX7Q16WoyO.

[2]CP2102 single-chip usb to uart bridge datasheet[EB/OL].[2013-11-05].http://www.docin.com/p-214094872.html.

[3]孙文友,胡永红,刘海川.高速2CPFSK调制器的设计与实现[J].测控技术,2006,12(25):7-9.

[4]Philips Semiconductors NE/SE564 phase-locked loop datasheet[EB/OL].[2013-11-05].http://ne564.chinaicmart.com/.

[5]Video for Linux two api specification revision 0.24[EB/OL].[2013-11-05].http://www.linuxtv.org/downloads/legacy/video4linux/API/V4L2_API/spec-single/v4l2.html.

[6]S3C6400/6410 HW Multimedia Codec(MFC)Use’s Guide REV 3.20.[EB/OL].[2013-11-05].http://wenku.baidu.com/link?url=RLLADCEK1Z6hzCMQ7YUPSeVXAnt-5NqNoFuzzU8GK8h1-Y3jAHl0y 0-AGtCy0qBy3Rs9sDl-ZQutM-0hLBneHQxVsocJ0bwRQSlrHpzBrq.

[7]王社国.Linux信号量通信机制分析与实践[J].微机发展,2002(6):63-66.