基于FPGA的千兆以太网数据传输的设计与实现*

瞿 鑫,吴云峰,李华栋,郑天策,戴 磊,夏 涛

(电子科技大学能源科学与工程学院,成都 611731)

基于FPGA的千兆以太网数据传输的设计与实现*

瞿鑫,吴云峰*,李华栋,郑天策,戴磊,夏涛

(电子科技大学能源科学与工程学院,成都 611731)

摘要:为了解决大数据量长距离传输的稳定性和传输速率的问题,采用复杂可编程芯片FPGA设计出千兆以太网传输系统。为了简化设计,采用MAC+PHY方法实现以太网帧的封装及传输,MAC采用Virtex-4的嵌入式以太网IP核实现,PHY采用MARVELL公司的88E1111芯片实现,两芯片接口采用GMII连接模式。实验仿真结果表明,该传输系统能支持1 000 Mbit/s传输速率,该设计方案是可行的,有一定的实用价值。

关键词:千兆以太网;FPGA;IP核;GMII;MAC+PHY

随着网络技术的发展,网络化是不可避免发展的大趋势。本设计为了解决图像采集数据传输系统中大数据量传输的要求,分析设计了千兆以太网传输系统,与传统的百兆以太网相比,它的传输容量更大,对及时图像采集系统来说,以常见的1 024×1 024大小的16 bit图像为例,当相机帧为50帧/s时,计算所得的实时传输帧为800 Mbit/s[1]。普通图像传输就达到了千兆级的传输速率,这对数字相机的图像数据传输提出了较高的要求。因此解决大数据量的图像传输有着至关重要的意义[2]。

现在主流的一般的以太网传输设计方法,一是采用专用网络芯片,芯片集成了MAC和PHY的功能(比如DM9000A[3],AX88180[4]),这种方法设计简单可靠,缺点是传输协议支持有限,而且传输速率受限于该芯片。另一种是采用FPGA设计方法,FPGA的EDK集成开发环境采用PPC或者MicroBlaze处理器可以方便用户开发出自己理想的系统[5],EDK选用IP核进行连线和地址映射,SDK用C语言可以编写软件对IP核进行配置。采用EDK开发方法灵活,并且可以外挂三方工具(如Xilkernel和Lwip等[6-7]),但是操作比较复杂,CPU受外界环境特别是温度的影响比较大,并且需对嵌入式系统开发有较深入的了解。本设计采用Xilinx的IP核[8],用纯硬件方式设计网络传输,系统简单,移植方便。

1 系统总体结构及基本原理

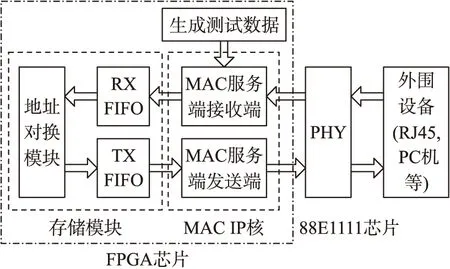

根据计算机网路基本模型,为了实现最基本的数据传输,需要实现数据链路层和物理层。物理层采用PHY芯片88E1111,数据链路层实现数据封装成帧,用FPGA的IP核实现。系统框架如图1所示,测试数据按照Ethernet Ⅱ型帧格式编写,MAC每次发送8 bit数据而网络传输是按照一帧一帧地传输,所以需要在发送端加FIFO,进行缓存,每一帧加入目的地址和源地址以及标志位,当一帧数据发送完进行下一帧数据发送,根据帧序列网络判断网络类型和长度等信息。帧的封装在MAC的IP核中完成,到FIFO存储端时目的地址和源地址互相对调。帧的发送时在FPGA内部完成。发送接收端口外部接物理芯片88E1111,然后连接网络变压器和RJ45接口,经CAT-5类线连接到PC机。

图1 系统组成框图

2 系统结构分析及其设计

2.1传输模式的配置

网络传输模式种类很多,10M/100M就有MII模式,1000M的有GMII、SGMII、RGMII以及BASE-T等等,选用模式需要对PHY芯片的引脚进行配置,在FPGA中配置寄存器中赋值。其基本的赋值语句如下:

component EMAC is

port(

……

TIEEMAC0CONFIGVEC:in std_logic_vector(79

downto 0);

……)end component;

signal tieemac0configvector_i:std_logic_vector(79 downto 0);

tieemac0configvector_i<=′1′ & phy_config_vector_0_i &has_mdio_0_i &speed_0_i &……;

其中,phy_config_vector_0_i指PCS/PMA没用到,赋值“1000”;has_mdio_0_i指是不是使用外部MDIO与PHY相连,本设计需要对PHY进行读写操作,赋值‘1’;speed_0_i指网络速度,按约定“00”是10M,“01”是100M,“10”是1000M,“11”不可用,这里赋值“10”选用1000M。

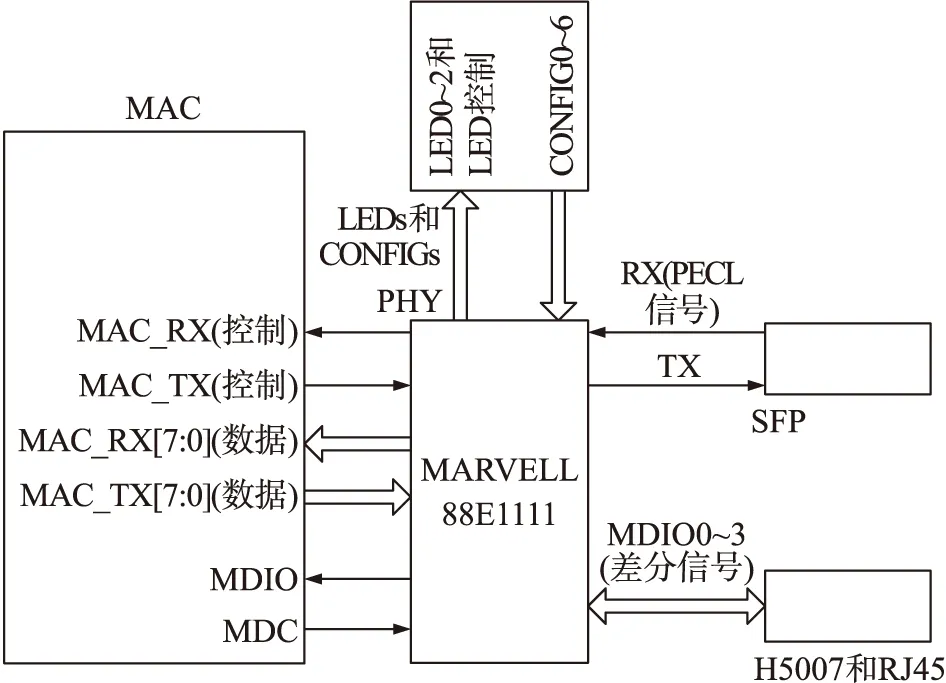

图2 模式选择及外围电路

配置向量共80 bit,需要按照MAC说明赋值。

PHY读写在MDC时钟驱动下,MDIO从FPGA发送一串字节序列到PHY芯片,由芯片检测到序列执行相应操作,其中MDIO是双向端口。

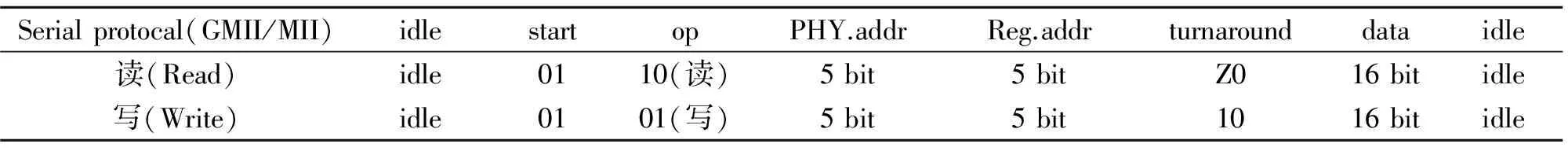

Serialprotocal(GMII/MII)idlestartopPHY.addrReg.addrturnarounddataidle读(Read)idle0110(读)5bit5bitZ016bitidle写(Write)idle0101(写)5bit5bit1016bitidle

写操作的示例如下:

2.2时钟选择

本设计需要的时钟包括传输速率驱动时钟,1 000 Mbit/s对应的是125 MHz时钟(当全局时钟,时钟线分布最广),MAC服务端驱动时钟200 MHz,以及PHY的MDC,按照要求,MDIO的频率不得超过8.3 MHz。

由于外围电路FPGA工作频率选用的是100 MHz,所以用2个DCM_ADV模块可以得到125 MHz和200 MHz。由于DCM不能设定输出8.3 MHz,采用计数器设计一个分频器对100 MHz输入分频即可。

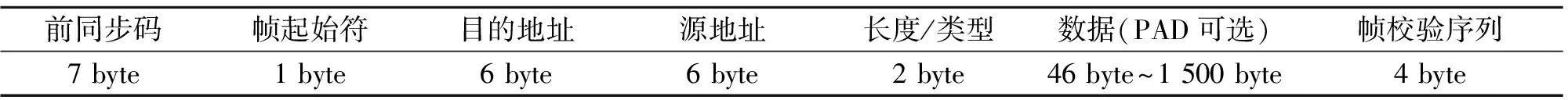

2.3帧格式

基本网络传输是按照以太网帧格式进行传输,本设计用的是最广泛应用的Ethernet Ⅱ型帧格式。其基本结构如下:

前同步码帧起始符目的地址源地址长度/类型数据(PAD可选)帧校验序列7byte1byte6byte6byte2byte46byte~1500byte4byte

前同步码(preamble field):让物理层信号(PLS)与接收帧时序达到永久同步。前同步码是7个0xAA(小字节10101010),这里VHDL赋值是大字节序,需要倒过来,是”01010101”。

时钟上升沿来到时,循环7次赋值。

for j in 0 to 6 loop

gmii_rxd<="01010101" after dly;wait until gmii_rx_clk_int’event and gmii_rx_clk_int=‘1’;

end loop;

帧起始分解符(SFD):帧起始序列字段为10101011(小字节序)0xAB

gmii_rxd<="11010101" after dly;wait until gmii_rx_clk_int’event and gmii_rx_clk_int=‘1’;

地址需要定义数据类型,定义matrix(5 downto 0)of std_logic_vector(7 downto 0)的数据类型。

长度类型标明后面数据位长度,数据部分当实际数据不够长度时,需要补0填充。类型0x0800代表IP协议数据,16进制数0x809B代表AppleTalk协议数据等,这里采用IP协议数据。

帧校验根据CRC[9-10]计算生成的校验和填充到末尾。

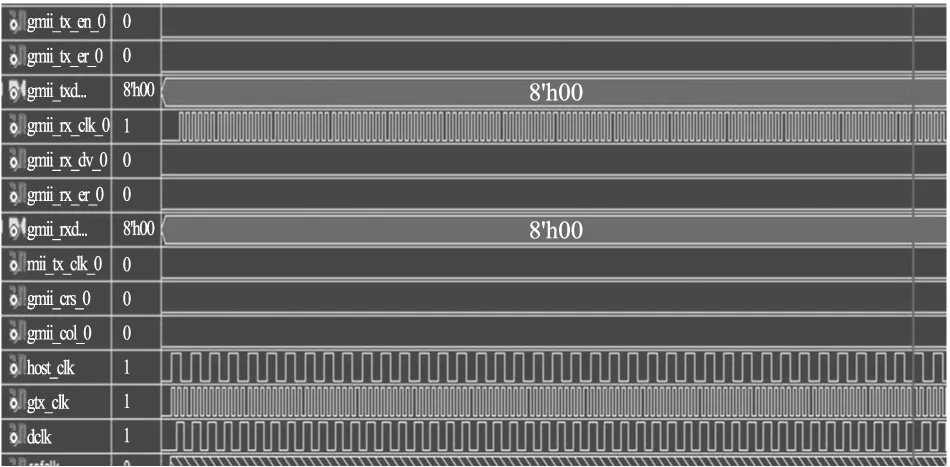

3 实验结果及分析

实验仿真芯片采用Xilinx Virtex-4芯片XC4VFX20-10FF672,该芯片集成千兆以太网IP核以及DCM管理时钟,能满足设计要求。

在ISE中模拟发送端(gmii_txd_0)发送字节0x00,能在接收端(gmii_rxd_0)接收到数据0x00,并且全局时钟gtx_clk和客户端host_clk的时钟均能满足设计的要求,说明该设计能满足实验目的。

图3 仿真结果

4 结论

本文从以太网传输的总体结构和基本原理出发,设计了千兆以太网传输系统的方案,以MAC+PHY为核心,完成了网络架构中物理层和数据链路层的基本功能。与传统网络设计相比,传统网络传输协议单一,不能更改,本设计的灵活性很高。在图像采集系统中,新修订的相机接口的GigE Vision 2.0协议[11-12]是在UDP基础上做的改进,网络传输就只能自己搭建网络协议,本设计的出发点就是为了匹配该协议,为后续做图像传输做工作。实验结果表明该设计能实现网络数据的传输,稳定性好,灵活性高,在科研生产中有很强的实用价值。

参考文献:

[1]何家维,何昕,魏仲慧.高速Cameralink图像数据光纤传输系统设计[J].信息技术,2011(10):9-12

[2]刘民.嵌入式千兆以太网络图像传输系统设计[D].大连:大连理工大学,2012(6):1-2

[3]马文超,张涛.一种基于FPGA的以太网高速传输平台[J].计算机工程,2012,38(1):242-243

[4]马腾飞,高世杰,吴志勇.基于千兆以太网的图像采集系统设计[J].技术与方法,2010,9:72-74

[5]王长清,陈栋.基于FPGA的千兆以太网通信板的设计与实现[J].河南师范发现学报(自然科学版)2011,39(1):86-89

[6]鲍兴川.TCP/IP通信技术在Xilinx FPGA上的实现[J].水泥水文自动化,2007(2):20-22

[7]高一沅,黄春晖.基于MicroBlaze的以太网通信系统平台设计的研究[J].现代电子技术,2007(17):29-31

[8]ug074 Virtex-4 FPGA Embedded Tri-Mode Ethernet MAC User Guide[EB/OL].Xilinx.com

[9]Giuseppe Campobello,Giuseppe Patane,Marco Russo.Parallel CRC Realization[J].Transaction on Computers,IEEE,2003

[10]曹云鹏.以太网MAC层协议研究与FPGA实现[D].兰州:兰州大学,2011:4-24

[11]Norouznezhad E,Bigdeli A,Postula A,et al.A High Resolution Smart Camera with Gige Vision Extension for Surveillance Applications[C]//Distributed Smart Cameras,2008.ICDSC 2008.Second ACM/IEEE International Conference.

[12]He Wenhao,Yuan Kui,Xiao Han,et al.A High Speed Robot Vision System with GigE Vision Extension[C]//Proceeding of the 2011 IEEE International Conference on Mechatronics and Automation.2011:452-457

瞿鑫(1989-),男,汉族,湖南衡阳人,电子科技大学硕士研究生,主要研究方向光电测控与精密仪器(电路系统),quxinnh@126.com;

吴云峰(1972-),男,汉族,电子科技大学光电信息工程学院博士,能源科学与工程学院副教授,研究生导师,主要研究方向为光电检测仪器,功率变换器与智能控制系统。在电子科技大学工作期间,作为课题负责人,完成了总装新品项目和横向课题10余项,总经费超600万;独立或合作发表论文90余篇,一级学报发表论文20余篇,yfwu-72@163.com。

DesignandImplementationforGigabitEthernetDataTransmissionBasedonFPGA*

QUXin,WUYunfeng*,LIHuadong,ZHENGTiance,DAILei,XIATao

(University of Electronic Science and Technology,Chengdu 611731,China)

Abstract:In order to solve the stability and transmission rate problems during the long-distance transmission of large amounts of data,the complex programmable-chip FPGA is used to design the Gigabit Ethernet transmission system.To simplify the design,we use MAC+PHY strategy to achieve the Ethernet frame encapsulation and transmission,Virtex-4 embedded Ethernet IP core to act as MAC,MARVELL 88E1111 chip as PHY.Two-chip connect with GMII interface.The simulation results show that the transmission system can support transfer rate 1 000 Mbit/s.This design is feasible and has certain practical value.

Key words:Gigabit Ethernet;FPGA;IP core;GMII;MAC+PHY

doi:EEACC:6210C10.3969/j.issn.1005-9490.2014.04.018

中图分类号:TN914

文献标识码:A

文章编号:1005-9490(2014)04-0662-03

收稿日期:2013-08-11修改日期:2013-08-28

项目来源:中国工程物理研究院流体物理研究所“分幅相机图像传输系统”