八核浮点型DSP的双千兆网接口设计

刘德保,汪安民,韩道文

(1.同方电子科技有限公司研究所,九江 332009;2.解放军电子工程学院)

八核浮点型DSP的双千兆网接口设计

刘德保1,汪安民1,韩道文2

(1.同方电子科技有限公司研究所,九江 332009;2.解放军电子工程学院)

单个千兆网口无法满足一些系统的需求。采用PCIe或者RapidIO接口可以进一步提高接口速率,但加大了系统的复杂度,而且和大部分既有设备无法直接连接。为此,本文提出一种双千兆网口接口实现技术,将网络数据传输速率提高2倍。以多核DSP芯片TMS320C6678为应用平台,介绍了双千兆网口的通信设计方法以及详细的软硬件设计方法。

多核;千兆网口;DSP

引 言

千兆网络接口具有数据传输速率快、连接方便、可以即插即用的优点,使得其应用较为广泛。随着电子技术和处理器的发展,很多应用场合的数据通信速率超过千兆网口的实际传输速率。例如,在A/D采样中,需要直接存储A/D转换的采样数据,如果A/D转换位数为16位,工作在100 MHz,则实际数据量为1.6 Gbps。为了实现高速传输,必须采用更高传输速率的接口,例如PCIe或者RapidIO接口。但这些接口不具有即插即用功能,与很多工业既有设备不能直接连接,限制了其应用场合。

DSP(数字信号处理器)具有较高的工作频率,其内部集成硬件网络MAC接口,外接一个物理层芯片就可以方便地实现千兆网络通信。多核DSP芯片可以连接多个千兆网口,使得其可以应用到高速数据传输场合。本文介绍一种基于多核数字信号处理器TMS320C6678的嵌入式双千兆网络接口,实现单个芯片连接两个千兆网口,这两个网口可以各自独立传输数据,也可以联合传输数据,提高了实际的数据传输速率。

1 C6678及其结构

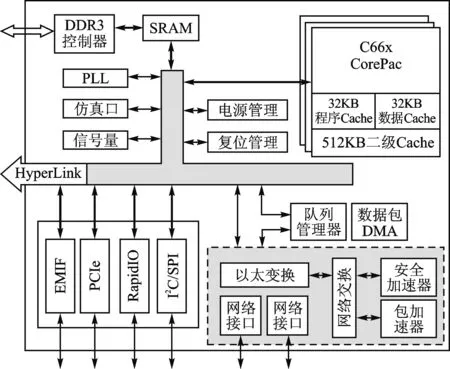

TMS320C6678是TI公司多核处理器中的一款8核浮点型DSP,每个核最高工作频率可达1.25 GHz,每个核可以提供40GMAC定点计算或者20GFLOP浮点计算能力,单个芯片可以提供320GMAC或者160GFLOP计算能力。TMS320C6678的片内结构如图1所示。

图1 TMS320C6678内部结构图

TMS320C6678的每个核具有32 KB的程序、32 KB的数据以及512 KB的2级Cache存储空间,芯片片内具有一个4MB的共享SRAM。TMS320C6678具有DDR3控制器接口,可以外接DDR3,直接寻址范围达到8 GB。TMS320C6678的片内外设有RapidIO、PCIe、EMIF、SPI、I2C总线等接口。这些接口通过片内的高速互联总线和各个处理器交互数据。

和网络相关的片内设备如图1右下角灰色模块所示,主要包括两个对外的SGMII接口、以太交换和网络交换模块,以及用于数据管理的安全加速器和包加速器,可以快速检测数据的校验以及协议是否遵循网络标准,对于错误的数据直接丢弃,降低CPU的负担。为了加快网络和CPU的数据交换,片内的队列管理器用于管理网络包或者网络帧的缓存、分发等功能。这些数据都采用数据包DMA读写,不需要CPU参与。

TMS320C6678的其他片内设备包括PLL、仿真口、信号量、电源管理和复位管理等模块。其中PLL配置CPU和外设的工作时钟;仿真口用于连接仿真器,实现对软件运行的监控;信号量实现对DSP/BIOS操作系统中信号量的控制;电源管理实现整个芯片电流电压的控制;复位管理配置启动的方式,硬复位进行全启动,软复位进行部分启动。

2 88E1111及其结构

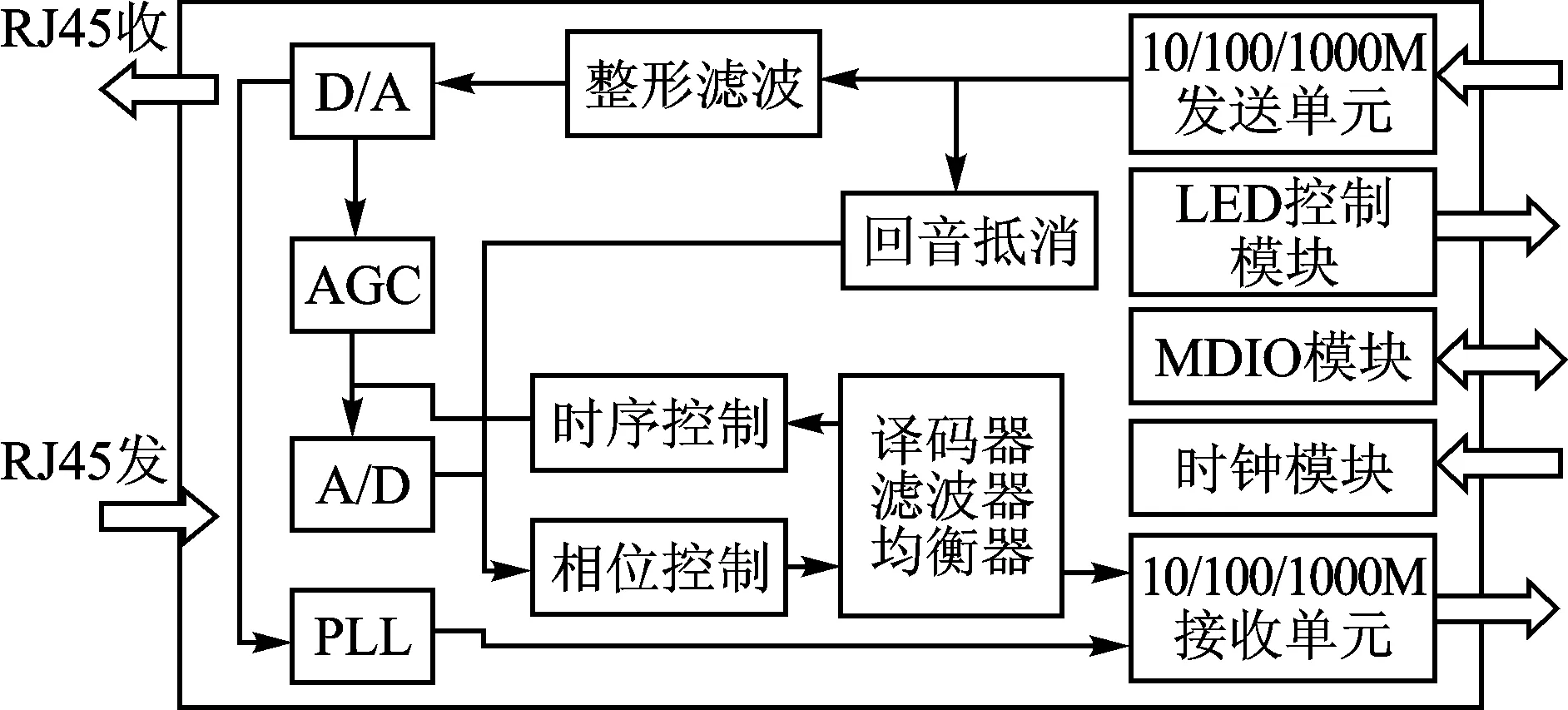

网络物理层芯片很多,一般都兼容MII、RMII以及SGMII等接口标准之一或者多个。但TMS320C6678只提供了SGMII接口,所以和TMS320C6678连接的物理层芯片必须具有SGMII接口。本文使用两片Marvell公司的88E1111物理层芯片进行双千兆网络的连接。88E1111的片内结构如图2所示。

图2 88E1111内部结构图

网络RJ45接口发送过来的带有调制数据的模拟信号经过A/D转换变成数字信号,然后依次经过均衡、整形滤波和译码后由接收单元传输到MAC芯片,实现数据的接收。MAC发送的数据经过整形滤波后由D/A转换成模拟信号发送到RJ45接口。为了降低误码率,88E1111内部具有锁相环(PLL)、自动增益控制(AGC)、时序/相位控制、回音抵消等模块,这些模块都是为了提高数据传输的可靠性,在不同环境或者不同外接设备下,都可以高速可靠地通信。图2中的LED控制模块实现数据传输时的灯光显示,MDIO模块实现链接建立和状态监测,时钟模块提供工作时钟。

3 硬件设计

硬件设计主要包括TMS320C6678和两个88E1111的接口、88E1111和RJ45的接口、88E1111的硬件配置设计等几个部分。

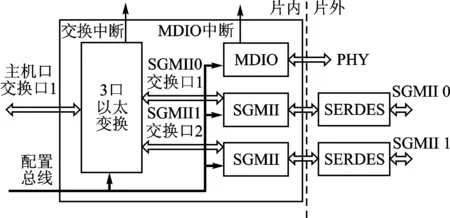

TMS320C6678的网络模块结构如图3所示。片内集成了一个3口的以太交换机,负责将两个千兆网口的数据交换到主机,同时提供交换中断到主机,主机通过中断可以实时接收和发送数据。主机通过总线配置或者监控外部的物理层芯片,配置和监控数据通过MDIO接口连接到物理层芯片。

图3 TMS320C6678网络模块结构

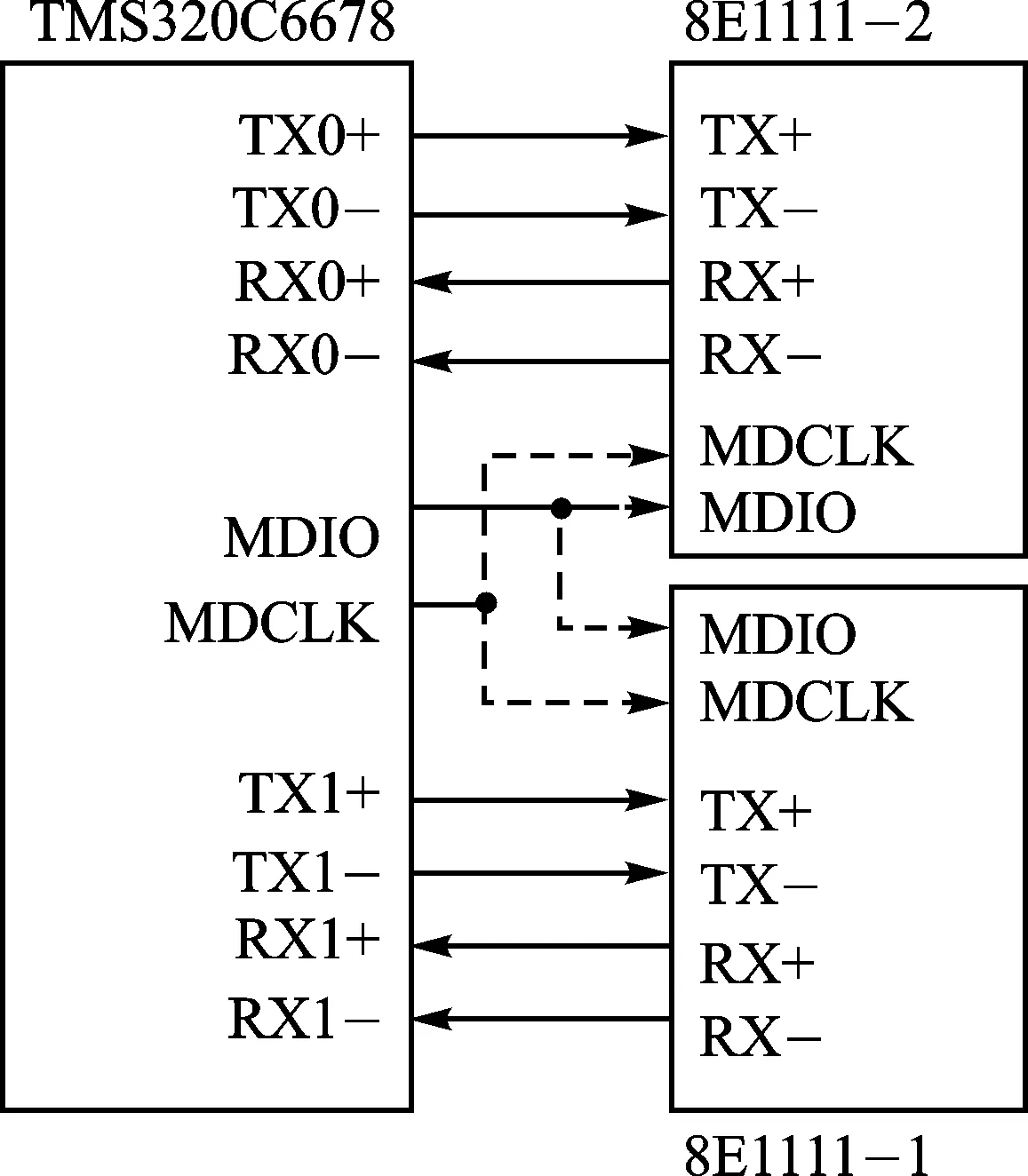

图4 TMS320C6678和88E1111的接口

TMS320C6678和两片88E1111的接口电路如图4所示。TMS320C6678采用SGMII(SerialGigabit Media Independent Interface)接口,兼容10/100/1000M工作方式。SGMII为串行数据收发方式,具有较少的引脚连接。从图4中可以看出,实际上只有两对收发的差分线,分别连接到对应的88E1111引脚上。读写时钟隐含在数据上传输,由硬件自动识别,无须软件参与。

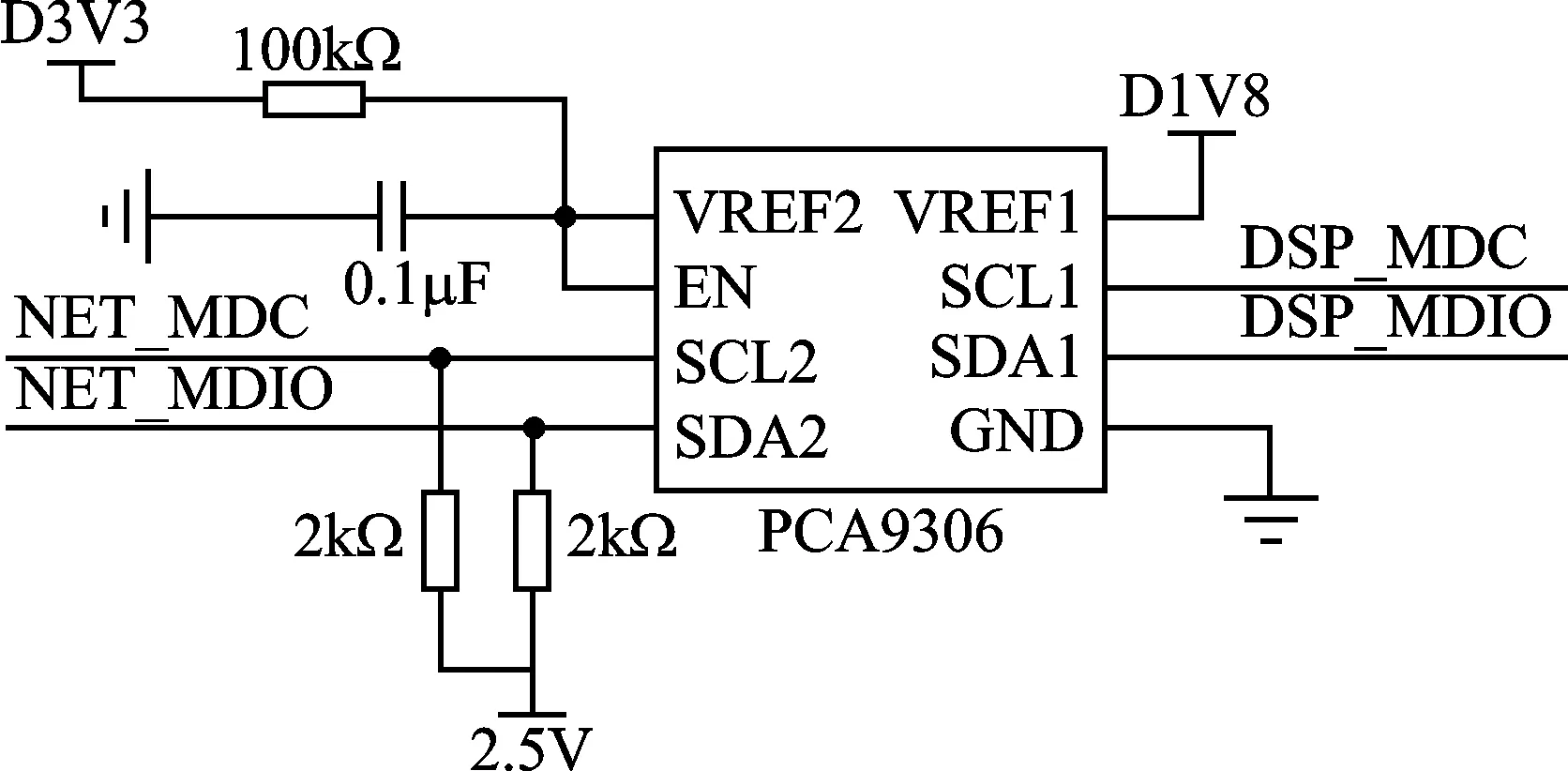

MDIO和MDCLK为TMS320C6678内部MDIO模块的数据和时钟,用于TMS320C6678和88E1111建立连接,TMS320C6678可以通过该接口配置88E1111,或者读取88E1111的信息。由于88E1111的MDIO模块接口电平为2.5 V,而TMS320C6678的MDIO模块接口电平采用1.8 V电压,所以两者之间需要增加电压转换芯片,本设计采用PCA9306实现电压转换,接口电路如图5所示。

图5 MDIO接口的电压转换电路

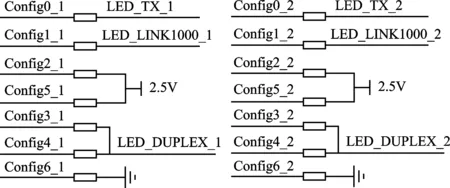

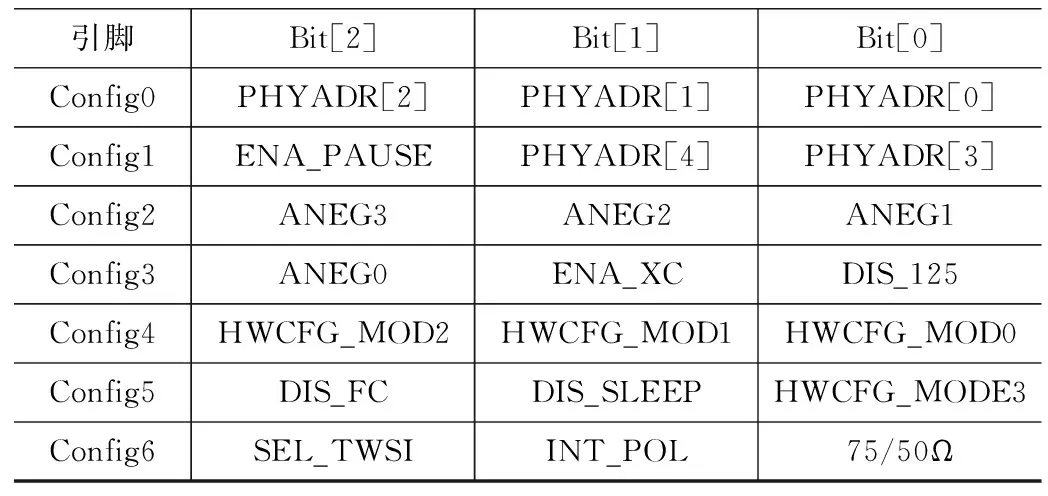

需要注意的是,由于存在两个88E111芯片,MDIO和MDCLK引脚直接连接到两个芯片上,MDIO可以最多控制32个物理层芯片,物理层芯片地址分别为1~32。88E1111的地址配置如图6所示。

图6 88E1111的硬件配置

表1为对应的配置信息,根据图6和表1,可以看出88E111的地址分别为4和8。

表1 配置引脚设置

4 软件设计

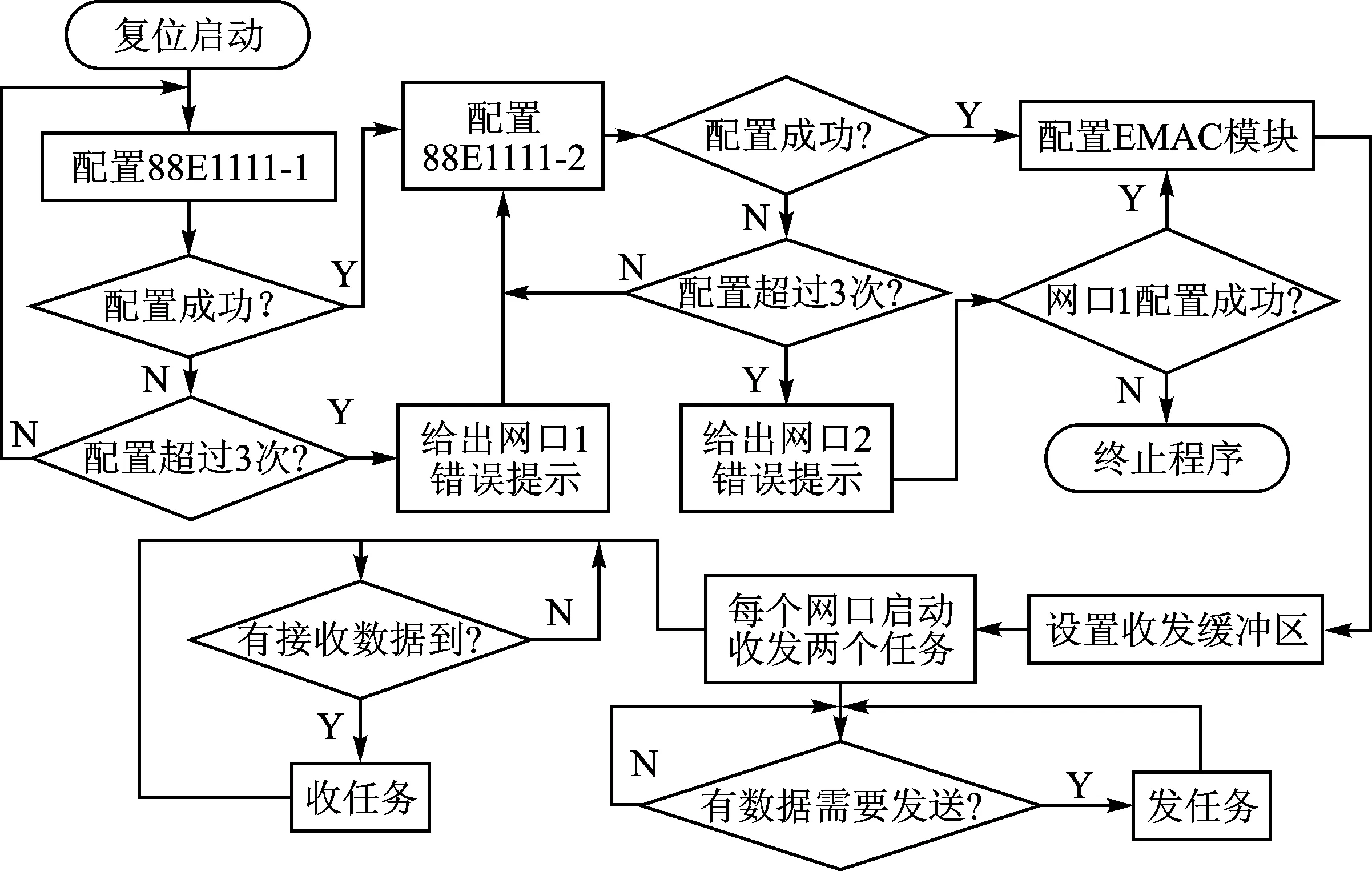

系统软件设计包括硬件初始化、网络配置以及数据通信流程等。TMS320C6678复位后的工作流程如图7所示。首先配置第一个网口,记录其状态后配置第二个网口。只要两个网口有一个配置成功,将配置TMS320C6678的EMAC模块,为成功配置的网口设置收发缓冲和收发任务。这些配置好后,就可以实现网络的数据收发。需要注意的是,在用户应用程序中,需要考虑到网口配置失败的情况。例如,用户应用程序通过双网口实时传输1.2 Gbps的数据,如果一个网口配置失败,则应用程序应有相应的机制将实时传输速率降低到0.8 Gbps以下(单网口实际传输速率可能低于0.8 Gbps)。本文硬件系统在没有其他任务开销情况下,实测可以传输1.5 Gbps的数据(传输过程中不考虑错误,不进行重发)。

图7 数据通信流程

结 语

[1] 丁有源,汪安民. 基于多核DSP的软硬件设计[J].单片机与嵌入式系统,2012(5).

[2] Texas Instruments.TMS320C6678 Multicore Fixed and Floating Point Digital Signal Processor Datasheet,2010.

[3] Texas Instruments. TMS320C645x DSP Ethernet Media Access Controller (EMAC) Management Data Input Output(MDIO)Module User’s Guide, 2010 .

[4] Marvell Semiconductor. 88E1111 Datasheet Integrated 10/100/1000 Ultra Gigabit Ethernet Transceiver (Rev. H),2006.

Design of Double 1G Base-T Ethernet Based on 8-Core Floating-point DSP

Liu Debao1, Wang Anmin1,Han Daowen2

(1. Research of Tongfang Electronic and Technology Ltd Co.Ltd., Jiujiang 332009,China; 2. Electronical Engineering Institute of PLA)

A single Gigabit Ethernet port cannot satisfy the system requirements, using PCIe or RapidIO port can further improve the interface rate, but this method will add system complexity, and either port cannot be connected directly to most available equipments. For this purpose, the paper presents a dual Gigabit Ethernet ports interface technology, the network data transfer rate are increased by 2 times.Based on the multicore DSP chip TMS320C6678, this paper introduces the communication design of the double Gigabit Ethernet port, and the software and hardware design are given in detail.

multicore;1G Base-T Ethernet;DSP

TP336

A

迪娜

2013-08-03)