通过淀积-腐蚀-淀积实现平坦化的研究

王 岳

(中国电子科技集团公司第四十七研究所,沈阳110032)

通过淀积-腐蚀-淀积实现平坦化的研究

王 岳

(中国电子科技集团公司第四十七研究所,沈阳110032)

在半导体器件和集成电路的研制和制备过程中,随着工艺水平的提高及技术进步,双层乃至多层布线越来越多,尺寸也越来越小。然而,在尺寸较小、台阶较高的情况下,如果在第一层金属上淀积介质后直接形成上层布线就会导致断条现象的出现,这就导致了平坦化成为非常重要的一项工艺。给出了平坦化工艺的基本原理,通过优化工艺条件并进行实验验证,确定了平坦化的最佳工艺条件,可以确保进行一次金属刻蚀以后,片子表面仍能基本平坦,这样就为二次布线打下了良好基础,杜绝了断条现象的产生。

平坦化;刻蚀速率;二氧化硅;光刻胶

1 引 言

在半导体行业的制造工艺中,平坦化作为一项重要工艺具有非常重要的作用。对于台阶较高尺寸较小并且采取双层金属布线工艺的电路来说,会在第一层金属线条形成后出现金属台阶。这时如果仅仅在淀积上介质后就开始形成上层布线的话,势必会导致第一层金属台阶被传递到上层金属。这样就会导致上层金属在刻蚀时位于台阶的位置很容易出现断条的现象,所以在淀积介质前有必要使表面趋于平坦。以下介绍了平坦化的基本原理,从大量工艺试验中摸索工艺条件,给出了淀积-腐蚀-淀积平坦化技术,从根本上解决了出现断条的问题。

2 淀积-腐蚀-淀积平坦化基本原理

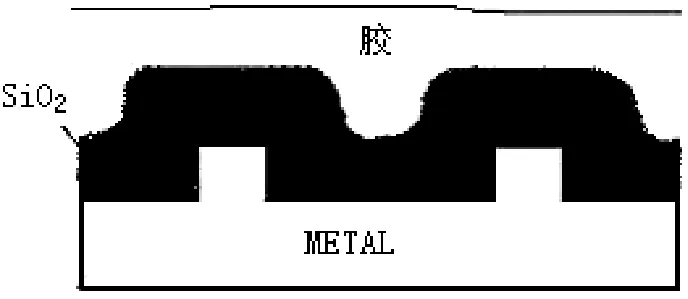

在一次金属刻蚀完毕后,先在金属台阶上淀积一层SiO2,然后进行光刻胶的涂覆,这样就可以利用液体的流动性填充形成一个较平的表面,如图1-图2所示。

图1 在SiO2上涂胶

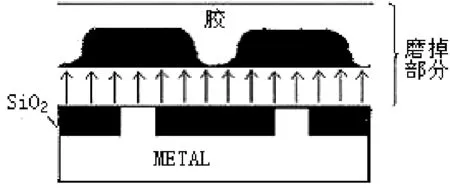

图2 腐去多余部分形成平坦表面

涂胶完毕后,将硅片送入烘箱或固胶机进行坚膜,待其形成固体表面后再送入干法刻蚀机并通过调整CF4和O2的流量比率以及机器功率等刻蚀条件,使刻蚀光刻胶和SiO2的速率几乎一致,这样在腐蚀到金属台阶表面时,就会保持表面的平坦化,如图2所示。平坦的表面形成以后,再在其上淀积SiO2、刻通孔、溅二次金属,这样就确保了二次金属光刻、刻蚀过程中图形的完整性,如图3所示。

图3 在平坦表面上淀积SiO2和二次金属

3 光刻胶和二氧化硅刻蚀速率一致性的实现

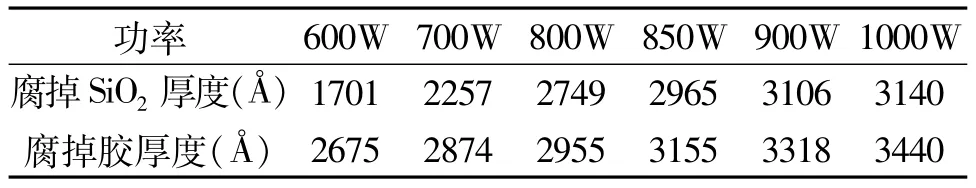

淀积-腐蚀-淀积平坦化的关键技术就是使光刻胶和二氧化硅的刻蚀速率基本达到一致,这样就可以在刻蚀过程中,使片子表面始终保持平坦状态。刻蚀二氧化硅的主要气体是CF4,刻蚀光刻胶的主要气体是O2。V胶/VSiO2主要受功率、CF4的流量及O2的流量控制。首先调整功率大小,先找到比较合适的功率再调整气体流量。首先将条件定为:CF4的流量为40sccm、O2的流量为20sccm、反应室压力40mT、刻蚀时间定为10分钟,由小到大增加功率,分别测出光刻胶和二氧化硅的刻蚀速率,找出最合适的功率。

将淀积有SiO2的试验片和涂好光刻胶的试验片分别测出上、中、下、左、右五点的厚度。将两片同时放入机器刻蚀10分钟后取出,测出对应5点的厚度,与先前测的对应5点做差之后取平均值,试验结果如表1所示。

表1 相同时间不同功率刻蚀掉SiO2与胶厚度表

由于刻蚀时间相同,所以SiO2和胶腐蚀掉的厚度比即是速率比,据以上数据画出SiO2和胶速率比的曲线图。如图4所示。

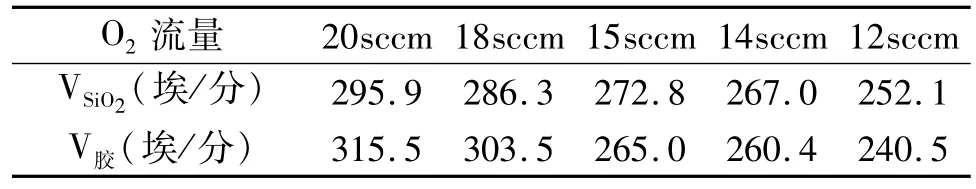

从图5可以看出,随着功率的增加,V胶和胶速率都增大,但是在850W,VSiO2和V胶的速率最接近,所以将功率定在850W。不过胶的腐蚀速率还是稍大一些,所以减小O2流量以减小V胶。虽然SiO2的腐蚀速率也会因此降低但要比胶的腐蚀速率下降的慢,随着O2流量的减小,就可以找到VSiO2和V胶速率相同的点。将结果列于表2。由试验结果画出图5所示。

图4 不同功率下胶和SiO2腐蚀速率

表2 不同O2的流量下,VSiO2和V胶的速率

图5 不同O2流量下胶和SiO2腐蚀速率

由图5可以看出O2的流量为15sccm时,VSiO2和V胶的速率最接近。因此确定出平坦化腐蚀的最佳条件:功率850W、CF4的流量为40sccm、O2的流量为15sccm、反应室压力40MT。

4 结束语

由于断条现象一直是影响多层布线的不利因素,经过研究分析,优化工艺,最终确定平坦化的工艺条件为:功率850W、CF4的流量为40sccm、O2的流量为15sccm、反应室压力40MT。在确保一次金属刻蚀后,片子表面基本平坦,为二次布线打下了良好基础。

[1]Michael Quirk,Julian Serda,韩正生,等.半导体制造技术[M].北京:电子工业出版社,2000.

[2]Stephen A.微电子制造科学原理与工程技术[M].北京:电子工业出版社,2003.

[3]朱正涌.半导体集成电路[M].北京:清华大学出版社,2004.

Study on Planarization By Deposit-corrosion-deposit

WANG Yue

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

As the improvementof technical progressand the technology of the semiconductor during its integrated circuitmanufacturing and preparation,thewiring size in double layer andmulti layer is gettingmuch smaller.However,under the high level in small size,if the upperwiring ismade directly after themedia isaccumulated on the first layer of themetal,the breakagewill appear.So,the planarization processing becomesmore and more important.The paper describes the principle of the planarization processing and it is tested by the technical process for determining the optimal processing condition in order to prevent the second wiring from breakage.

Planarization;Velocity of etching;SiO2;Photoresist

10.3969/j.issn.1002-2279.2014.04.010

TN4

:A

:1002-2279(2014)04-0030-02

王岳(1984-),男,辽宁省沈阳人,助理工程师,主研方向:集成电路制造。

2014-01-10