阵列信号源程序更新模块设计

胡琪 颜科峰 蒋国军

(第七一五研究所,杭州,310023)

阵列信号处理是现代信号处理的重要分支,它被广泛应用于雷达、移动通信、声呐、地震勘探、射电天文、电子医疗等多个领域。阵列信号源包含多个按一定空间规则排布的信号产生单元,通过控制每个单元的信号延时产生不同形状的波束。基于这个目的,阵列信号源有时被设计成为“一个主控,多个阵元”的结构。主控是指上位计算机,阵元即信号产生单元。信号产生单元通常以MCU或DSP为核心,独立产生信号和计算延时。这样的硬件组成可以提供更灵活多样的输出,但通常会增加软硬件维护的复杂性和备件成本,尤其在信号阵元数量很大时,所以,研究一种适用于这种系统结构的固件维护与升级方法具有重要意义。

1 硬件介绍

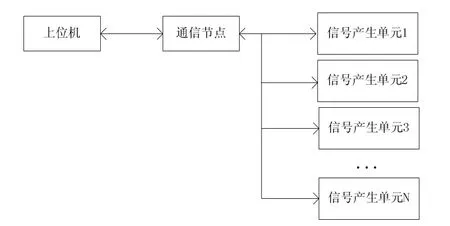

阵列信号源可抽象为图1所示。其中用户通过上位机生成指令,指令通过通信节点进行协议或接口转换,然后被送到各个信号产生单元生成信号。本文描述的阵列信号源系统中,信号产生单元的核心是Freescale公司的MCF52259,这是一款32位MCU,主频最高可达80 MHz,片上包含64 kB的RAM和512 kB的Flash ROM,接口包含UART、I2C、SPI等[1]。这款芯片可以在程序中对Flash ROM进行读写操作,而且程序可以运行在RAM或Flash ROM中,这些特性将被用于这个设计中。上位机与通信节点间使用LAN网络通信,通信节点与信号产生单元间使用UART接口通信。上位机对各个信号产生单元进行程序更新。

图 1 阵列信号源架构图

2 软件设计

2.1 上位机部分

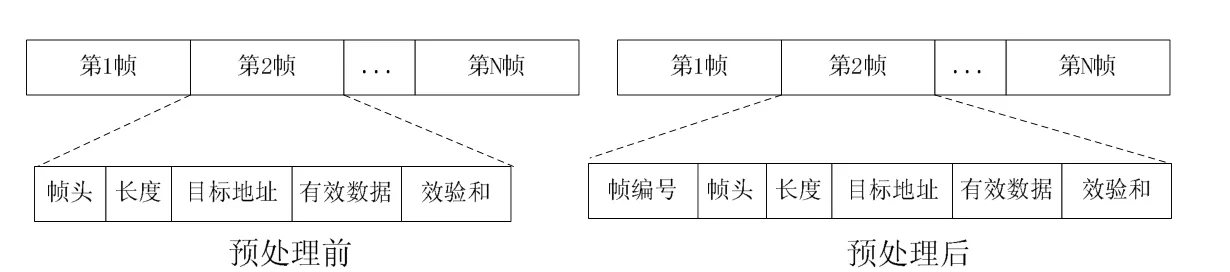

信号产生单元的固件更新,实质上就是将在上位机编译产生的目标程序烧录到信号产生单元MCU的Flash指定空间上。MCF52259的目标文件是标准格式的S19文件,这是一个ASCII码文件,需要将内容转换成十六进制进行传输。根据文件结构定义,S19文件分为若干个固定大小的帧,每帧内容包括帧头、长度、目标地址、有效数据与校验和[2]。在程序更新前,上位机将对S19文件进行预处理,给每帧添加一个编号。信号产生单元可以通过编号判断文件中帧的完整性,通过校验和判断帧内数据的完整性,如图2所示。

图 2 S19文件结构

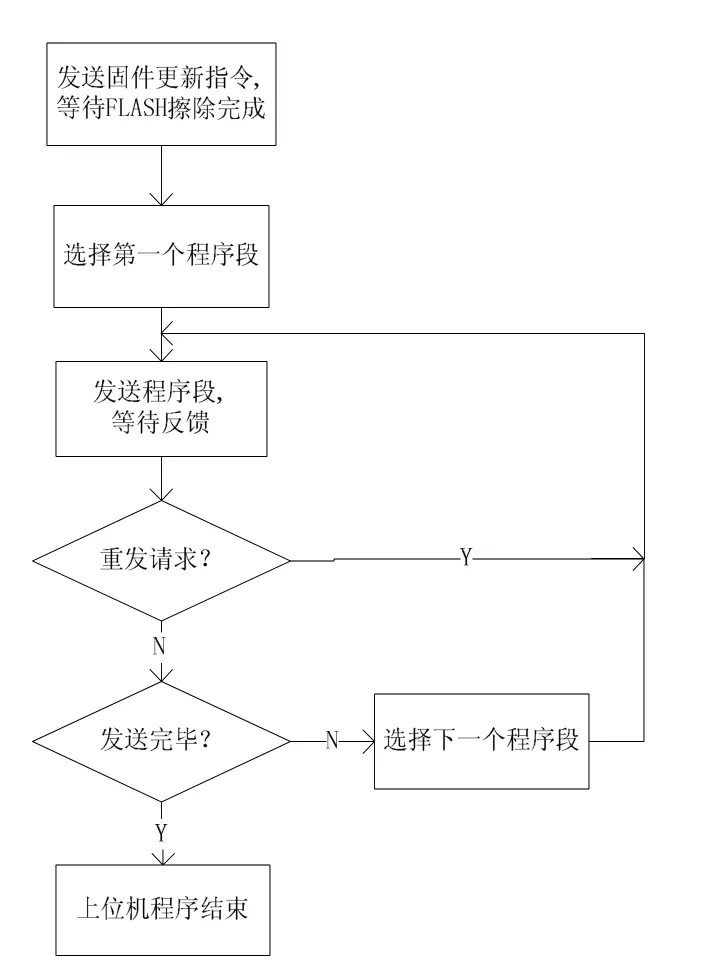

程序更新过程中,上位机与节点板之间进行多次数据传输,每次传送一个帧。节点板将内容转发给各个信号产生单元。信号产生单元接收到数据后需要进行校验与反馈,仅当校验通过才能执行写入操作,对校验失败的帧应进行重发,确保固件的完整性。图3是上位机工作流程图。

图 3 上位机工作流程图

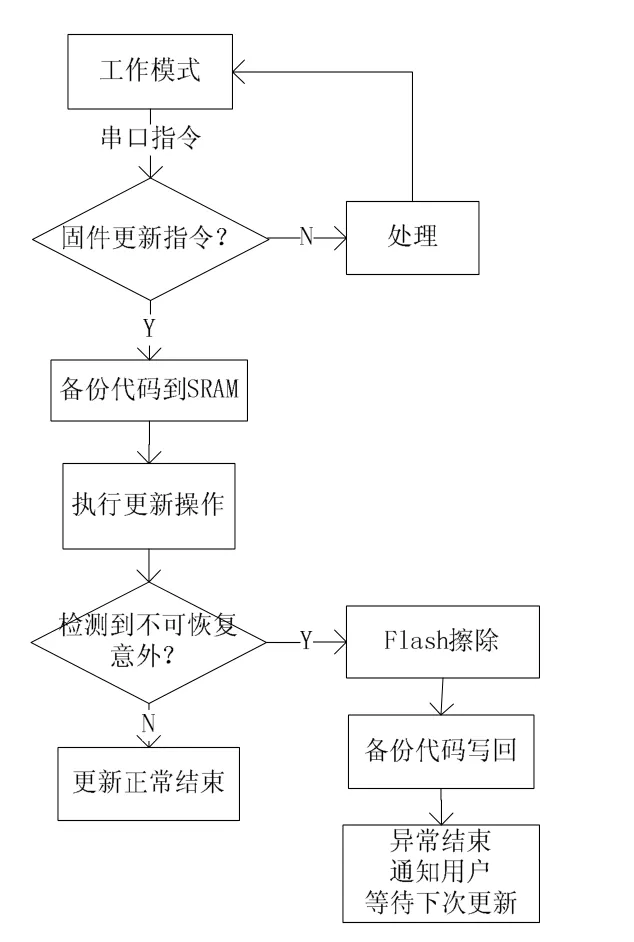

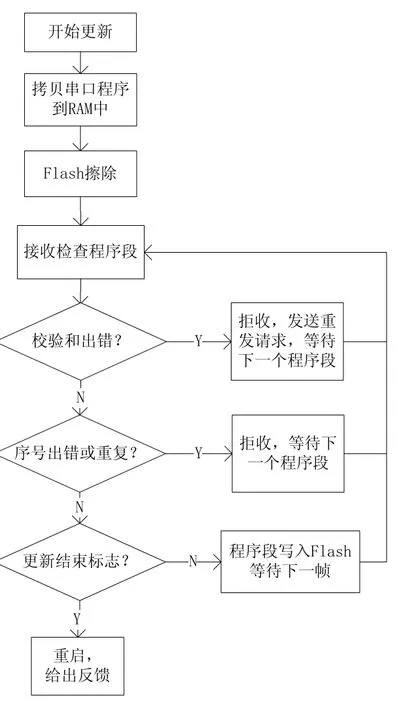

2.2 信号产生单元部分

信号产生单元工作流程如图4(a)所示,正常的更新过程流程如图4(b)所示。对信号产生单元而言,整个操作流程涉及到Flash擦写操作,如果操作过程中某个环节出问题,比如上位机发送过程中出错且无法恢复时,将会使所有信号源的固件失效。这里采用备份最小系统的方法来加强系统的可靠性。信号产生单元通过串口接收到更新指令后进入更新模式。更新模式过程中,首先备份一个最小系统到SRAM 中,然后执行具体的更新操作。最小系统代码中包含了必要的硬件初始化设置、串口收发等操作,能独立完成程序更新任务,更重要的是,它也能实现自我备份和还原,防止最小系统在更新过程中遭到破坏。当更新操作中检测到不可恢复错误时,比如主机失去响应,看门狗程序将被激活,最小系统被写回Flash中,系统下次加电时直接启动最小系统,避免系统因更新失败而无法启动。正常更新过程中,因为Flash会被擦除,所以期间需要运行的代码应该被拷贝到内存上,然后通过修改程序指针的方法从内存中运行代码[2-3],完成擦写Flash、与主机通信接收新程序段等任务。接收过程中,程序将完成校验和比对、帧序号比对,一旦比对出错将生成信息反馈到主机。

图 4(a) 信号产生单元工作流程

图 4(b) 更新操作流程

3 功能验证

实际测试中,我们对六路信号产生单元同时进行了固件更新,其中S19文件大小为183.8 kB,每帧长度为138 byte,由于每个字符的ASCII码占用8 bit,转换为十六进制数后空间减半,算出实际帧数为682帧。最小系统在其中占用了约40帧空间,即 5 kB左右大小,相对于 512 kB大小的 Flash ROM来说完全可以接受。

传输速率方面,为保证上位机发送数据后信号产生单元有足够时间进行处理,每帧发送结束后上位机都进行延时。起始帧因为要等待Flash擦写完成还要额外延时5 s,其余每帧发送完毕后延时20 ms,总耗时小于20 s。

4 结论

本文方法在线进行,无需外加电路,仅通过已有的硬件链路就可完成,避免用仿真器对硬件进行逐个操作,它能将本来需要几个小时甚至数天才能完成的大量繁琐工作在几分钟内完成,节省时间、人力和硬件资源。在烧写过程中备份最小系统的设计能增强可靠性,有效降低系统升级维护风险。这种方法已在工程项目中得到应用,并适用于具有类似架构的其他大型系统。

[1] Freescale. MCF52259 ColdFire Integrated Microcontroller Reference Manual[M].2009.

[2] Freescale. Implement UART Boot-loader On Coldfire V1 Products[M].2010

[3]Freescale.TN259:Placing Varibles and Code in ROM Using the Codewarrior Linker Configuration File for ColdFire Architecture[M].2008.

[4] Freescale. ColdFire编程参考手册[M].2009.

[5]谌利. 深入浅出ColdFire系列32位嵌入式微处理器[M].北京: 北京航空航天大学出版社,2009.