基于FPGA的数字锁相环设计

贾志城(甘肃政法学院图书馆,甘肃 兰州 730070)

1 引言

在无线通信系统中,锁相技术应用广泛,其位同步提取至关重要。为在信宿接受信号中恢复出与信源同频率码元时钟信号,实现码流位同步,通常利用锁相环直接从接收的数字信号中提取位同步信号。

利用数字电路实现的锁相环具有易于存储、易于生产、成本低、元件无漂移和无容差等优点[1][2],而且数字积分器没有失调和易失性的问题,能够完成模拟电路无法完成的任务,数字锁相环发展动力强劲。数字锁相环易于集成,功耗低,体积小,性能可靠,应用灵活且性价比较高,在实际通信系统中得到了很好的应用。

2 插/扣型数字锁相环的典型结构和工作原理

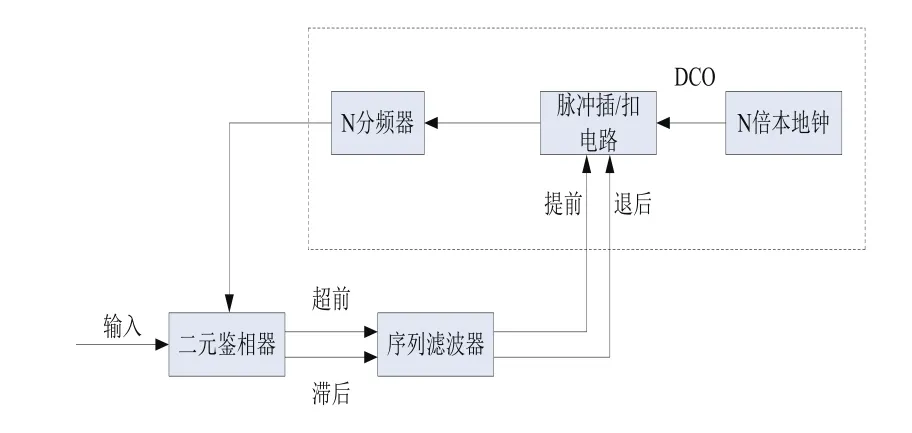

插/扣脉冲型数字锁相环的结构如图1所示[3]。主要由二元鉴相器、序列滤波器和数控振荡器(DCO)三部分组成。

图1 插/扣脉冲型数字锁相环的典型结构

数字锁相环是一个闭环相位反馈控制系统。输入信号与N分频输出的信号进行超前-滞后二元鉴相,由反映相位误差的误差信号通过序列滤波器后输出控制信号,控制高倍本振时钟插/扣脉冲,以调整其时钟的频率再分频输出。

2.1 二元鉴相器

二元鉴相器是将相位误差θe(k)量化为1比特的鉴相器,其鉴相特性为

式中,sgn[x]代表对变量x取符号运算。广义来讲,对任何模拟鉴相器的输出进行如上式的运算后都可实现数字二元鉴相。对输入、输出为数字信号时,输入信号与输出信号比相,形成超前脉冲或滞后脉冲输出。超前脉冲意味着输出信号滞后,θe(k) > 0 ,故超前脉冲的作用是使环路调整输出信号的相位提前;滞后脉冲表示θe(k) < 0 ,其作用是使输出信号的相位推后。

2.2 序列滤波器

数字环路滤波器在环路中对输入噪声起抑止作用,并且对环路的校正速度起调节作用,其设计的结构形式和方法繁多,是一种专门的技术。数字环路滤波器专用于校正网络引入环路,选取合适的数字滤波器结构就能使数字锁相环满足预定的系统性能要求。

平滑鉴相器输出的控制脉冲的方法是在二元鉴相器后接序列滤波器[4]。常用的序列滤波器有“N先于M滤波器”和“随机徘徊滤波器”,基于前

者的设计理念,所设计的滤波器结构如图2所示。

图2 “N先于M”序列滤波器的结构图

“N先于M”序列滤波器的工作原理:二元鉴相器输出的超前、滞后脉冲分别在两个长度为N的寄存器内计数并存储,其和在长度为M的寄存器内计数存储,且选择N<M<2N。设初始时3个寄存器均复位为0,随着二元鉴相器脉冲的不断输出,3个计数存储器的数值不断增加,直至出现下列情况之一为止:

1)若某一个N寄存器在M寄存器存满之前或者与M寄存器同时存满,则相应送出一个“提前”(若超前N寄存器满)或“推后”(若滞后N寄存器满)脉冲到后续DCO,同时该脉冲复位3个寄存器到0。

2)若M寄存器先于任何一个N寄存器计数满,则同时复位3个寄存器到0,不产生“提前”或“推后”脉冲。该情况在环路相位差较小而输入信噪比又比较低时发生,因为此时鉴相器输出的超前、滞后脉冲数目相差不多,考虑到M寄存器设计长度介于N与2N之间,它会先于两个N寄存器计满,并清空该轮累计过程。

采用“N先于M”序列滤波器,只要选择适当的系数N与M,可以大大减小随机噪声造成的错误调整概率,同时又不过分降低输入信号相位漂移的跟踪能力。

2.3 数控振荡器(DCO)

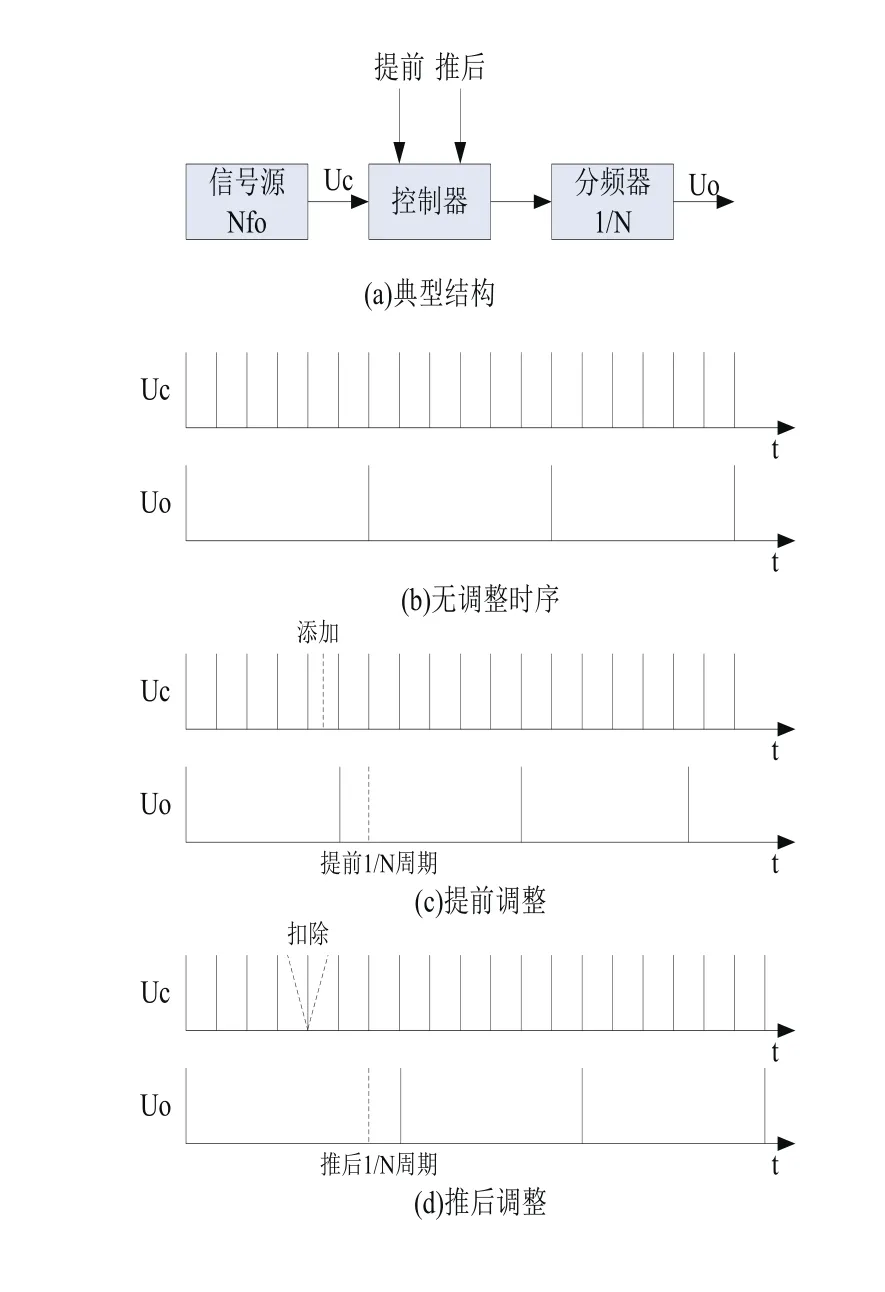

DCO的结构如图3所示,其中信号源输出频率fc=Nfo的窄脉冲序列,在无超前、滞后脉冲控制时,该序列经N分频器分频后,输出本振信号频率为fo。

当环路输入信号的相位滞后DCO输出信号的相位时,序列滤波器将“推后”脉冲加到控制器上,扣除一个本振源输出的高频脉冲,经N分频后使输出信号相位推后1/N周期,如图3(d)所示;反之,如果输入信号相位超前DCO输出信号相位时,则序列滤波器产生“提前”脉冲加到控制器上,控制器在窄脉冲序列流内插入一个脉冲,经N分频后使DCO输出相位提前1/N周期,如图3(c)所示。

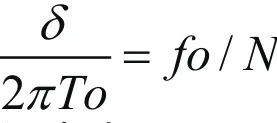

DCO的一次相位调整步长为

相应的频率调整步长为

上式中To是DCO输出本振信号的周期,To=1/fo,DCO输出信号相位与控制信号的关系为

其中uc(k)是序列滤波器输出的控制脉冲。

图3 DCO的典型结构

3 系统整体仿真和分析

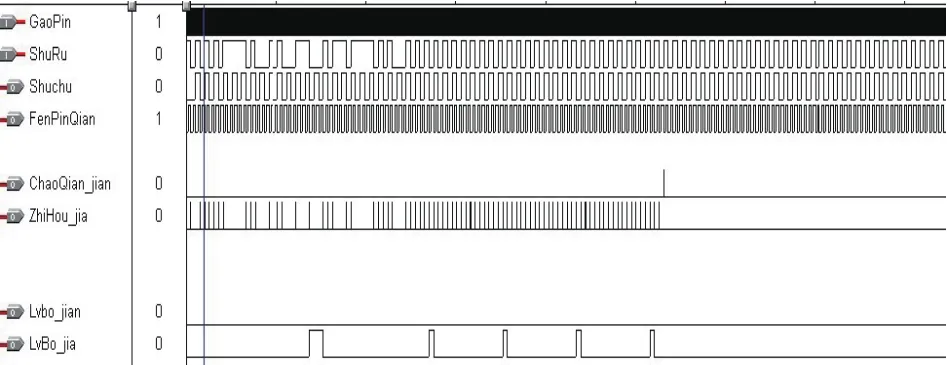

利用Verilog语言针对系统进行自顶向下的设计后,通过quartusII6.0集成环境进行仿真、综合、验证。如图4所示,其中GaoPin为高频信号,ShuRu为输入信号,ShuChu为本地输出信号,FenPinQian为输出信号未经过2分频的信号,ChaoQian_jian为控制减脉冲信号,ZhiHou_jia为控制加脉冲信号[5]。Lvbo_jian为滤波减脉冲信号,Lvbo_jia为滤波加脉冲信号。

由图可知,在锁定状态下消除了超前滞后脉冲的来回摆动,抗干扰性能有改善,但锁定时间有所增加。若位同步脉冲的相位超前较多,鉴相器需输出N个超前脉冲才能使位同步脉冲相位调整一次,显然调整时间增加N倍,需要考虑改进滤波电路的相位调整时间以及提高锁相环精度。

图4 仿真波形

4 结 语

基于模块化设计的数字锁相环具有结构简洁、调参方便、稳定可靠、设计灵活和易于实现的优点。

数字锁相环的设计对于基于FPGA的数字应用系统具有现实的意义。

[1]季仲梅,杨洪生,王大鸣.通信中的同步技术及应用[M].北京:清华大学出版社,2008.

[2]姚剑清.锁相环技术(第3版)[M].北京:人民邮电出版社,2007.

[3]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[4]倪虹霞,杨信昌.基于VHDL的全数字锁相环的设计[J].长春工程学院学报,2005.

[5]崔建庆,石江宏.基于FPGA的积分型数字锁相环的设计与实现[J]..现代电子技术,2005.