基于PCI Express总线的数字电视传送流发送/采集卡设计

娄新磊,吕 卫,宋 垣

(1.天津大学 电子信息工程学院,天津 300072;2.南京炮兵学院廊坊校区,河北 廊坊 065000)

基于PCI Express总线的数字电视传送流发送/采集卡设计

娄新磊1,吕 卫1,宋 垣2

(1.天津大学 电子信息工程学院,天津 300072;2.南京炮兵学院廊坊校区,河北 廊坊 065000)

提出了一种基于PCI Express总线的数字电视传送流发送/采集卡设计方案。详细阐述了板卡的整体设计、硬件接口以及软件实现,重点介绍了如何发挥PCI Express总线高带宽的优势实现高速DMA数据传输。最后,利用Quartus II 13.0开发环境下的SignalTap II工具对自行开发的PCI-E接口板进行了在线调试,测试表明该设计能满足数字电视传送流传输系统的要求。

PCI Express总线;FPGA;链式DMA;WinDriver

随着数字电视技术的发展,数字电视传送流采集系统在数字电视系统中的需求越来越广泛,并且对计算机总线技术提出了越来越高的要求。目前,个人计算机与工业控制计算机中常用的总线主要有USB2.0/3.0总线、PCI总线和PCIExpress总线[1]。USB2.0总线和USB3.0总线的理论最大传输速率分别可达到480 Mbit/s和5.0 Gbit/s,但USB总线的CPU占用率较高,不适合多任务系统的应用。PCI总线具有即插即用和传输速率高的特点,在常用的32 bit数据宽度、33 MHz总线时钟频率下可达到132 Mbit/s的峰值传输速率,许多数据采集卡都采用了32 bit@33 MHz或更高的32 bit@66 MHz、64 bit@66 MHz的PCI总线接口。然而,作为一种并行总线,PCI总线的引脚数量多,容易出现接触不良的故障,而且时钟频率不高,实现多路数字电视传送流发送/接收的应用比较吃力。PCIExpress(简称PCI-E)总线继承了PCI总线多方面的优点,且数据传输速率有了很大程度地提高,同时机械结构得到简化,工作更为可靠。针对PCI-E总线的技术优势,本文以FPGA为控制器,设计了一款基于PCI-E总线的数字电视传送流发送/采集卡,详细讨论了板卡的整体设计方案、硬件设计方案、Win⁃Driver驱动程序和上层应用程序设计,实现了4路数字电视传送流的实时传输。

1 硬件设计

在硬件上,以Altera公司的Cyclone IV GX系列FP⁃GA为控制器,实现数字电视传送流的接收和发送、DDR2 SDRAM缓存的控制,并且使用FPGA集成的PCI-E硬核实现PCI-E总线接口。在主机端,开发了Windows 7操作系统下的PCI-E驱动程序和MFC应用程序来测试数字电视传送流数据的接收、发送等功能。

1.1 硬件整体设计

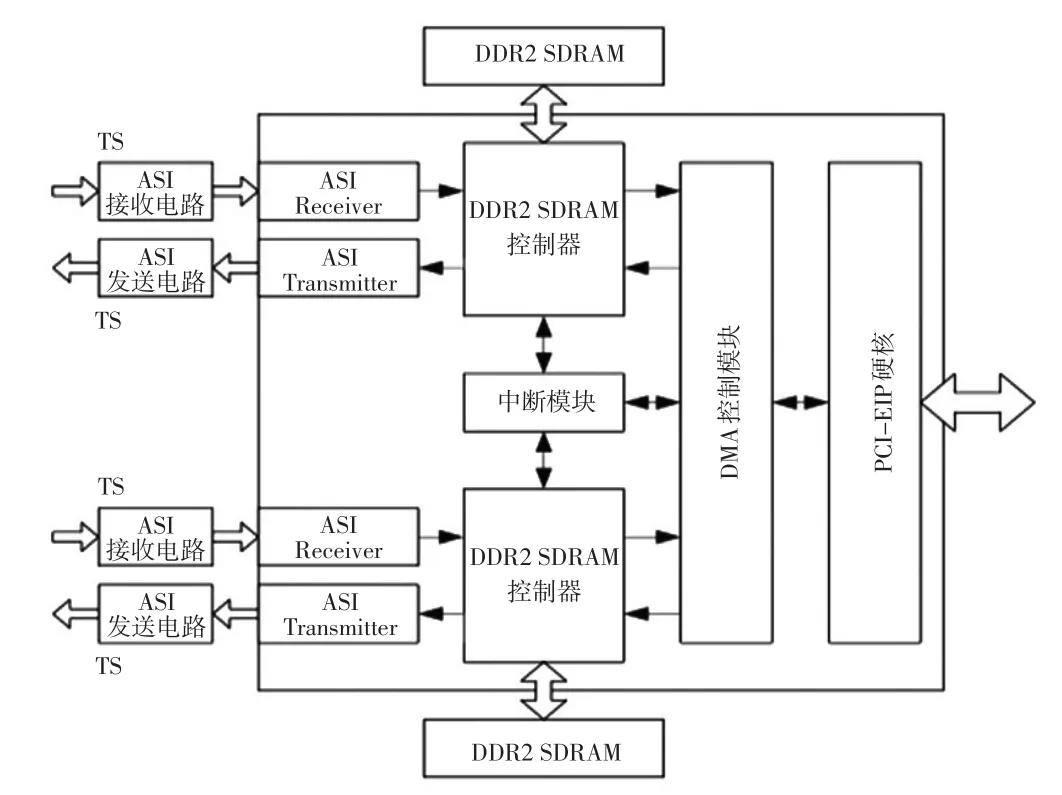

硬件系统的总体设计如图1所示。硬件设计主要分为4部分:1)ASI接口部分,该部分包括两路ASI接收接口和两路ASI发送接口,共4路,分为两组,每组包含一路接收接口和一路发送接口,ASI接收接口由ASI接收电路和FPGA上的ASI接收器模块(ASIReceiver)组成,ASI发送接口由ASI发送电路和FPGA上的ASI发送器模块(ASI Transmitter)组成;2)DDR2 SDRAM缓存部分,该部分由FPGA上的DDR2 SDRAM控制器(DDR2 SDRAM Control⁃ler)和外部DDR2 SDRAM存储器组成;3)DMA控制部分,该部分由自定义的逻辑来实现;4)PCI-E总线接口部分,该部分由Altera公司提供的PCI-E IP硬核实现。

图1 硬件系统设计框图

硬件系统的数据传输包括数字电视传送流接收通道和数字电视传送流发送通道两部分。

传送流接收通道:串行传送流经过ASI接收电路进入FPGA,ASI接收器模块对其进行串并转换、解码等操作,将串行传送流转换为并行码流,然后存入DDR2 SDRAM缓存中。当DDR2 DSRAM缓存中数据达到一定量的时候,中断产生模块产生中断,PC端的中断服务程序和上层软件通过PCI-E总线接口将缓存中的数据读出。

传送流发送通道:首先PC端软件将一定量的传送流写入DDR2 SDRAM缓存中,然后ASI发送器模块将缓存中的码流读出进行编码、并串转换等操作,将并行码流转换为串行传送流,并通过ASI发送电路发送出去。当DDR2 SDRAM缓存中的数据减少到一定量的时候,中断产生模块会产生中断,PC端软件检测到中断后再将一定量的传送流写入DDR2 SDRAM缓存中,如此反复。

1.2 数据缓存

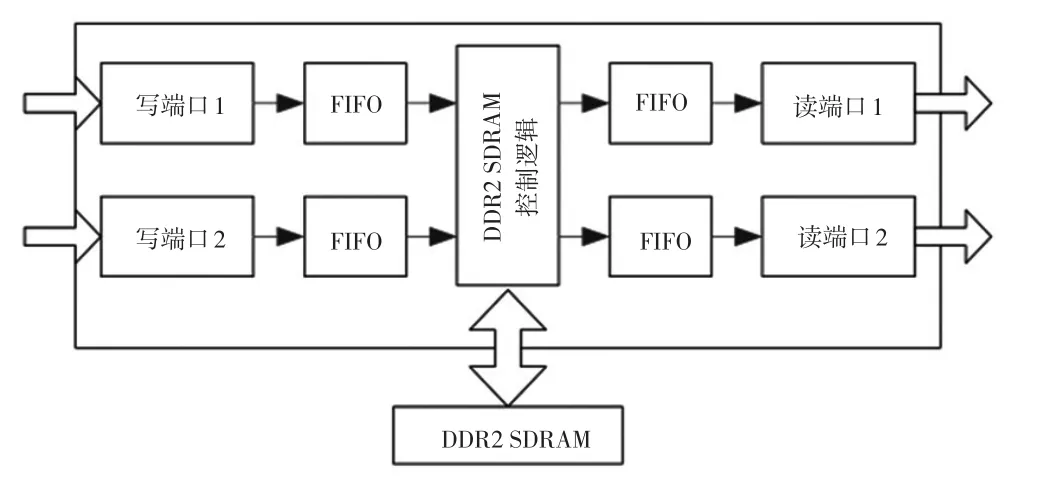

本设计使用DDR2 SDRAM存储器作为数据缓存,由FPGA硬件逻辑实现对DDR2 SDRAM的控制。缓存部分的设计原理如图2所示,DDR2 SDRAM控制器包含2个写端口和2个读端口,每个端口通过1个FIFO与DDR2 SDRAM控制逻辑连接,4个端口共享DDR2 SDRAM的带宽,分时占用DDR2 SDRAM的数据通道。DDR2 SDRAM控制逻辑实现对4个端口的仲裁控制和对DDR2 SDRAM接口的控制,仲裁控制决定某时刻DDR2 SDRAM数据通道由哪个端口使用。其中,数字电视传送流接收通道使用写端口1和读端口1,发送通道使用写端口2和读端口2。本设计实现了2个传送流输入接口和2个传送流输出接口,4个接口分为两组,使用两片DDR2 SDRAM存储器。

图2 4端口DDR2 SDRAM控制器

1.3 PCI-E IP硬核介绍

系统选用Cyclone IV GX系列的FPGA,它内嵌了一个PCI-E硬核模块,符合PCI-E Base Specification V2.0标准,支持×4通道,单向链路速率可达到8 Gbit/s[2]。

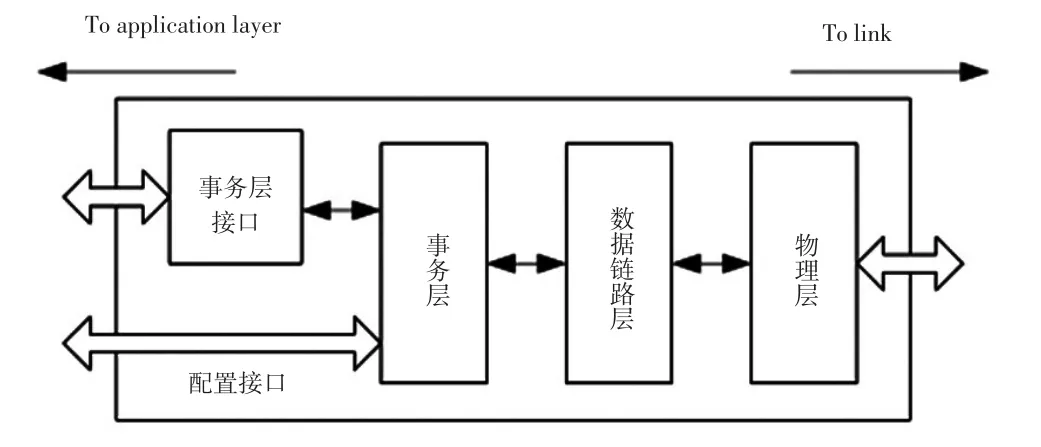

PCI-E IP硬核结构如图3所示,其功能模块分为事务层、数据链路层、物理层3部分。事务层主要负责事务层数据包(TLP)的接收、缓存和发送,事物层接口既可以使用Avalon-ST接口,又可以使用Descriptor/Data接口。数据链路层位于事物层和物理层之间,作用是保证数据包完整性,提供了CRC检测和恢复、DLLP的生成与拆解等服务。物理层位于最底层,分为MAC层和PHY层:MAC层通过链路训练与状态指示状态机完成链路初始化、训练以及维护工作,实现了扰码与解扰码功能;PHY层实现了8B/10B编码与解码、弹性缓冲、串行化/解串行化等功能。

图3 PCI-E IP硬核

PCI-E硬核模块和应用程序层之间的接口主要包括事物层接口和配置接口。事务层接口实现事物层数据包的发送和接收,本设计中使用Avalon-ST接口;配置接口实现中断信号的传送和PCI-E IP硬核配置空间的访问。

1.4 DMA控制逻辑设计

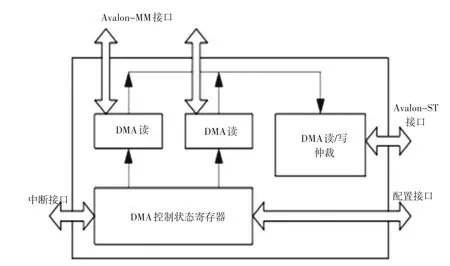

DMA控制逻辑设计原理如图4所示,该模块主要有4部分组成:DMA读模块、DMA写模块、DMA读/写仲裁模块、DMA控制/状态寄存器模块。DMA读模块和DMA写模块通过Avalon-MM总线与DDR2 SDRAM控制器连接,分别从DDR2 SDRAM中读取数据和写入数据;DMA读/写仲裁模块决定某时刻进行DMA读操作还是DMA写操作,并通过Avalon-ST总线与PCI-E IP硬核模块连接;DMA控制/状态寄存器模块包括与DMA操作相关的控制寄存器和状态寄存器,该模块通过中断接口从中断模块获取中断请求,并通过配置接口发送到PCI-E IP硬核模块。

图4 DMA控制逻辑

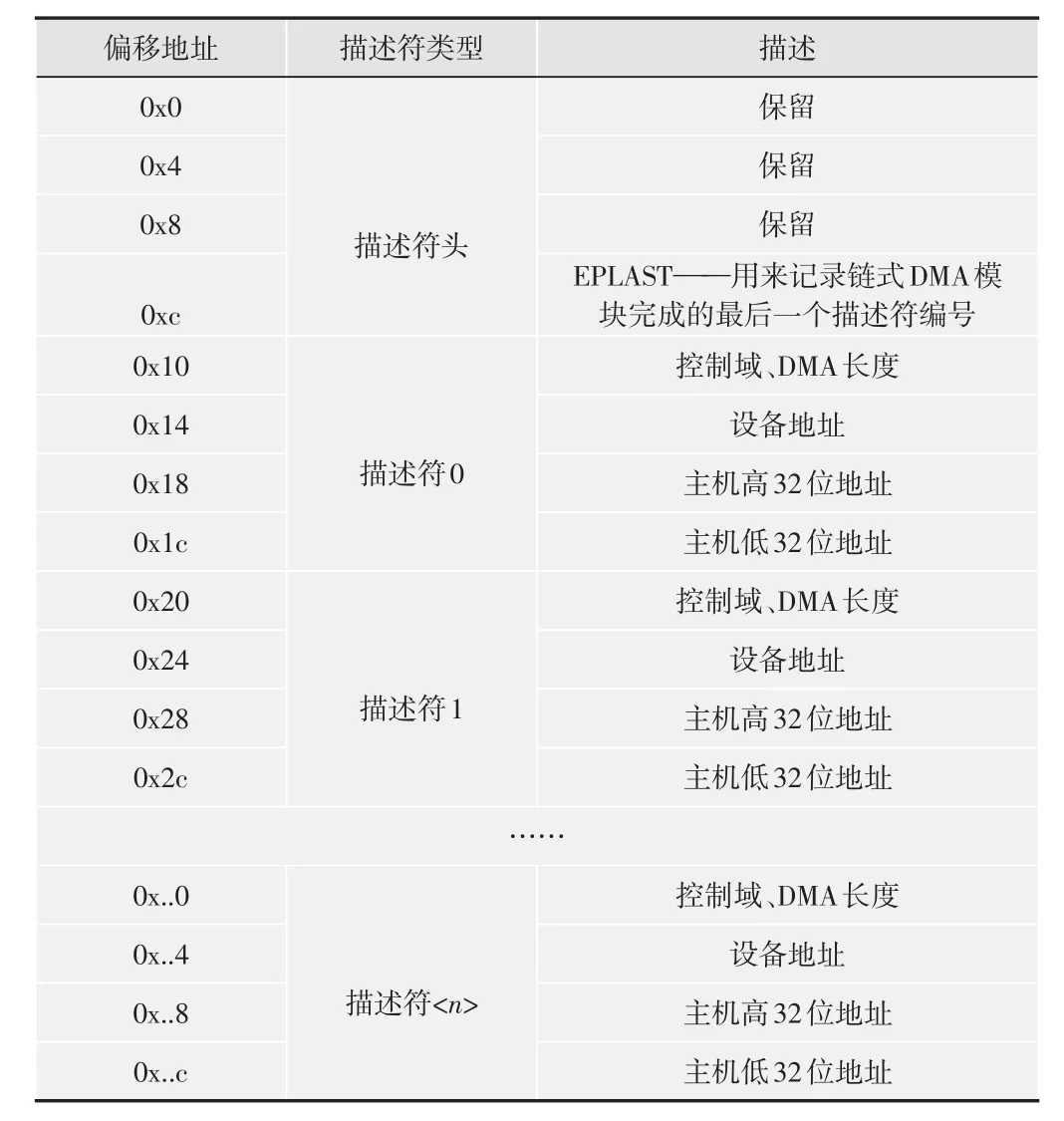

DMA的传输方式可分为两种:简单DMA和链式DMA。为了提高DMA传输效率,本模块实现链式DMA。该DMA模块工作原理是[3]:首先,在主机端开辟一块内存区域存储描述符表。描述符表描述的是主机与外设之间与数据传输相关的地址和长度信息,它由一个表头和多个描述符组成,其中的每一个描述符对应一次DMA操作。描述符表中的内容由用户自己填写,描述表如表1所示。然后,主机通过设置设备端DMA模块中的控制/状态寄存器告诉设备要传输数据的描述符表起始地址和描述符个数。最后,主机端启动DMA传输,设备收到启动DMA传输的命令后,首先根据主机提供的描述符表信息检索相应的描述符,然后根据每一个描述符中的地址和长度信息,进行相应的DMA数据传输。所有的DMA描述符处理完成后,设备更新描述符头部的EPLAST域,主机通过查询EPLAST域获得链式DMA传输完成的信息,从而可以启动下一次链式DMA传输。

表1 链式DMA描述符表

2 软件设计

2.1 驱动程序设计

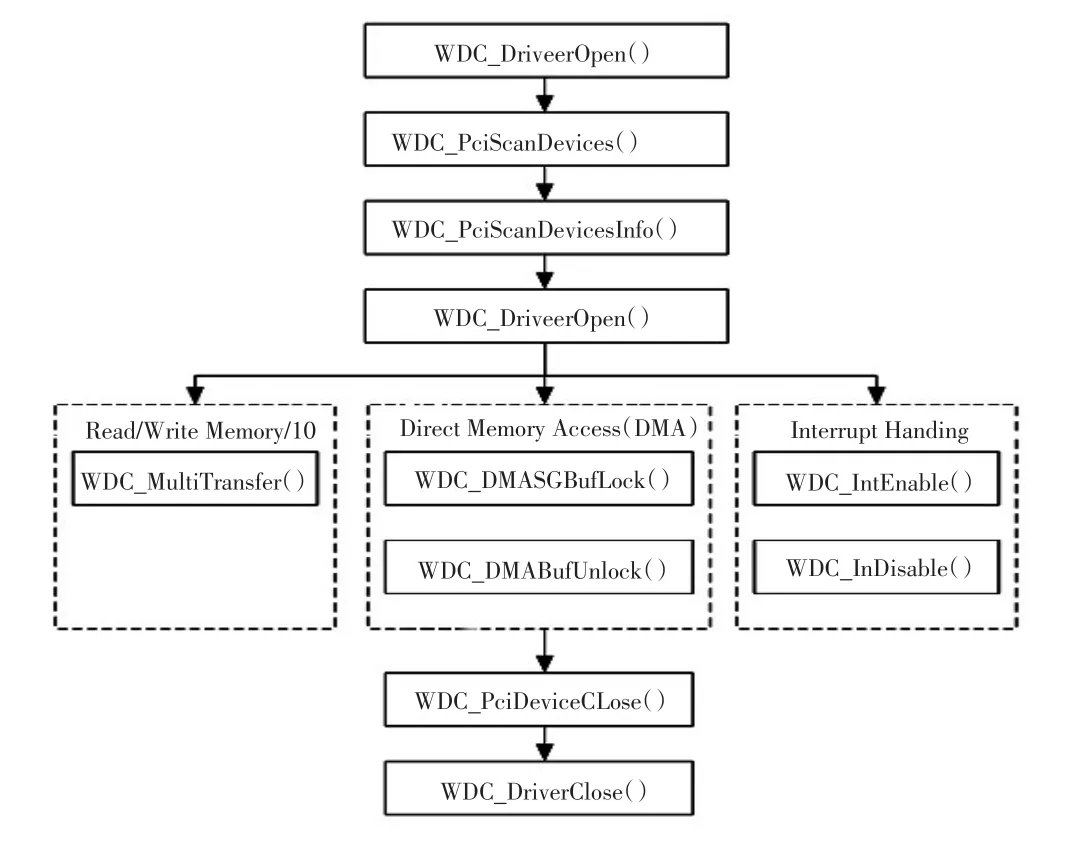

WinDriver是Jungo公司提供的驱动程序开发工具包。该软件提供了对PCIExpress接口设备的驱动支持,也可以为兼容DMA功能的底层设备提供DMA服务[4]。驱动程序的主要功能是初始化设备、配置FPGA、设置DMA操作、设置中断操作以及为应用程序提供接口函数。驱动程序的工作流程如图5所示。

图5 WinDriver驱动程序的工作流程

首先,通过调用WDC_DriverOpen(),WDC_PciScan⁃Devices(),WDC_PciDeviceOpen()等函数对设备进行初始化;其次,通过简单数据传输函数例如WDC_Multi⁃Transfer()完成对FPGA的初始化、配置等操作,并且根据需要设置DMA操作和中断操作;最后,当操作结束时,调用WDC_PciDeviceClose(),WDC_DriverClose()等函数结束进程。

2.2 应用程序设计

根据需要在Visual Studio 2010下开发了基于MFC的应用程序用来测试板卡的功能和性能。应用程序主要实现设备的打开和关闭、对FPGA硬件逻辑中寄存器的访问、数字电视传送流的接收和发送功能。其中,数字电视传送流的接收和发送由4个独立的传输线程实现,包括2个传送流接收线程和2个传送流发送线程。发送线程负责将一定量的数据写入到板卡的DDR2 SDRAM缓存中,接收线程负责从DDR2 SDRAM缓存中读出数据来验证发送数据和接收数据的正确性和完整性。该应用程序与板卡驱动程序的关系如图6所示。

图6 系统的软件结构

3 测试结果与分析

测试时使用Acterna公司的数字电视码流分析仪输出测试码流,并监视发送/采集卡的输出码流有无误码,同时用Quartus II中的SignalTap II工具监测DDR2 SDRAM缓存单元有无上溢/下溢的情况出现。反复测试表明,在4个通道传送流传输均无误的前提下,4个ASI接口的传送流传输速度均可达到200 Mbit/s以上。

4 结束语

本文利用集成了PCI-E硬核的Cyclone IV GX系列FPGA设计了一种基于PCI-E总线的数字电视传送流发送/采集卡,完成了FPGA硬件逻辑设计和主机端驱动程序和应用程序开发。该设计与使用专用的PCI-E桥接芯片的方案[5]相比,本地总线可支持更大的数据宽度,另外硬件成本也显著降低。与文献[6-7]提出的设计方案相比,本设计使用大容量的DDR2 SDRAM作为数据缓存,提高了数据传输的稳定性。

测试表明,该系统性能稳定、传输速度高,很好地满足了数字电视系统基带信号传输的要求。此外,本设计中的数据接口灵活性好,既可以扩充更多的ASI接口,又可以增加以太网接口、光纤接口等,能够满足多种应用的需求。

致谢:

[1] 王聪,王彬,薛洁,等.基于PCIe总线协议的设备驱动开发[J].信息技术,2013(3):32-35.

[2]PCIExpress Compiler User Guide[R].[S.l.]:Altera Corporation,2010.

[3] 黄世中,金志刚.利用WinDriver实现链式DMA[J].电子设计工程,2013,21(8):6-9.

[4]WinDriver PCI/ISA/CardBus User,s Manual[R].[S.l.]:Jungo Corpora⁃tion,2008.

[5]张小佩.基于PCI-E总线的数字电视传送流接口卡设计[D].天津:天津大学,2012.

[6]郑佳,任勇峰,李辉景,等.基于FPGA的多数据采集卡的研究与设计[J].电视技术,2013,37(1):52-54.

[7]殷玉喆,张继平,胡菊萍,等.YPbPr分量高清晰度视频分析仪的研制[J].电视技术,2013,37(10):101-104.

《电视技术》官方微博上线啦!

Design of DTV TS Transm ission/Acquisition Card Based on PCI Express Bus

LOU Xinlei1,LÜWei1,SONG Yuan2

(1.School of Electronic Information Engineering,Tianjin University,Tianjin 300072,China;2.Nanjing Artillery Institute,Hebei Langfang 065000,China)

The design of DTV TS transmission/acquisition card based on PCI Express(PCI-E)bus is presented in this paper. The overall design,hardware interface and software program of the card are introduced in detail,focusing on how to implement high-speed DMA data transfer based on the high bandwidth of PCI Express bus.Finally,an online test is done to the card with SignalTap II of Quartus II 13.0.Experimental results show that the design is adequate for transmitting/capturing multiple DTV transport streams.

PCI-E bus;FPGA;chaining DMA;WinDriver

关注“电视技术杂志”,获得更多行业资讯!

扫描上面二维码添加电视技术官方微信,可以获得更多行业资讯!

TN873

A

�� 盈

2014-08-11

【本文献信息】娄新磊,吕卫,宋垣.基于PCI Express总线的数字电视传送流发送/采集卡设计[J].电视技术,2014,38(21).

国家自然科学基金项目(61271069)

娄新磊(1990—),硕士生,主研嵌入式系统设计;

吕 卫,博士,副教授,主研数字视频技术和嵌入式系统设计;

宋 垣,讲师,主研计算机仿真。