3DSoC的多频测试架构设计

刘 蓓,汪千松,余 雷,陈 阳

(安徽工程大学 现代教育技术中心,安徽 芜湖 241000)

2012年ITRS发布数据,随着集成电路(integrated circuit,IC)特征尺寸不断减小,预计2020~2025年期间特征尺寸会跨越10nm的阈值,当减小至5~7nm时,将很难操作任何结构的晶体管.三维集成技术充分利用了垂直空间,通过硅直通(Through-Silicon-Via,TSV)解决层与层之间的相连,打破了传统平面布局中由于晶体管数目的增加导致连线长、功耗高、设计复杂度大的种种局限.由于不同类型的微电子系统可以堆叠在不同层[1],芯片的独立性也大大提高.目前三维片上系统的研究已成为IC发展的重要趋势.

在集成电路的实现过程中,测试是必不可少的一个环节,芯片通常需要依次进行裸片测试和产品测试来确保合格率.芯片的测试时间是影响测试成本的重要因素,而测试时间在很大程度上依赖于测试访问机制(Test Access Mechanism,TAM)的设计,因此在3DSoC的各项研究中,可测性设计(Design for Test,DFT)被认为是研究的重点[2].相关研究提出了传统多频SoC的测试方案并给出相应研究成果.文献[3]等研究了三维片上系统的测试优化技术,但在单一频率下对所有不同种类的IP核进行测试,很难满足异构系统的需求.本文设计了一种多频3DSoC的IP核测试外壳,并提出了相应的TAM解决方案,在功耗限制下实现了对各IP核的测试,给出了具体的测试方法和结果.

1 SoC测试结构

图1 SoC测试结构

SoC测试结构如图1所示.由图1可知,测试源可以提供被测电路所需的测试激励;测试宿通过对比预期结果和测试响应来确定测试电路功能正常与否;测试源和测试宿都由自动测试设备(Automatic Test E-quipment,ATE)提供.TAM是测试数据传输的通路,采用复用机制实现深嵌在SoC内部的IP核的测试,TAM是解决SoC测试的根本方法.IP核的测试外壳本质上是IP核与外部的硬件电路接口,负责将测试激励移入IP核,并及时移出测试响应.当IP核正常工作时,测试外壳不起作用;当IP核被测试时,它作为IP核和TAM之间的接口,为测试数据提供传送通道;当同一TAM的其他IP核测试时,它起到隔离作用,从而不影响其他IP核的测试.

2 3DSoC多频测试架构设计

目前针对IP核的测试都是在统一的工作频率下进行的,即测试访问接口Wrapper的设计基本上都是假设所有IP核在同一频率下被测试.但是针对3DSoC芯片中的不同功能模块,运行的时脉频率也不尽相同,为了降低测试成本,需采用并行测试方法来减少测试时间,这就要求ATE提供多种速率对其进行测试,使得原本就昂贵的ATE更是增加了设备投资成本.本方案拟对3DSoC中不同种类的IP核在封装时加入多频控制器,通过测试访问机制的优化,使得ATE在单一频率下就能对芯片进行测试.

2.1 测试扫描链设计

图2 细粒度扫描链结构

3DSoC中IP核的设计可分为2种[4]:粗粒度设计和细粒度设计.粗粒度设计不改变IP核原有的任何结构,采用平面布局的设计方法,内部扫描链和输入、输出单元都在同一层上;细粒度设计是根据需要将IP核的扫描单元分割到不同层芯片上,更科学地对扫描单元进行布局,在功耗和性能上与IP核粗粒度设计相比具有更多优势.本文在3DSoC的设计架构中采用IP核的细粒度设计方法,如图2所示.图2是一条扫描链,采用细粒度设计方案,将扫描链的7个扫描单元分别分布在两层芯片上,层1上有3个扫描单元,层2上有4个扫描单元,不同层之间的扫描单元通过4根TSV连接,构成一条扫描序列为1→2→3→4→5→6→7的扫描链.由于三维芯片的层间距离相对于扫描单元之间的距离非常短,因此可以忽略不计,通过这种方式构成的电路与传统电路相比就可以大大减少连线的长度,降低测试功耗.

2.2 多频测试架构设计

假定ATE的工作频率与所有IP核的内部扫描链测试频率都相同,那么ATE的端口可以直接将测试数据送入芯片进行测试.但实际情况是,ATE的工作频率越来越高,而IP核的扫描链由于并行测试时功耗的约束,通常会设置的比较低,如果整个测试过程依赖IP核扫描链的测试频率,势必会造成ATE大量处于空闲状态而导致测试时间的增加,进而影响到测试代价.

要让高速ATE和低速TAM之间互连,并充分利用测试资源,就需要让其两者的带宽匹配.带宽B可定义为数据位宽度W与频率f的乘积,即:B=W*f.通过使用串并/并串结构的频率转换器,使得高带宽的ATE可以同时与多个低带宽低速率的TAM相连,从而充分利用测试资源.假定测试过程中ATE提供的数据位宽度和频率分别是WATE和fATE,TAM的数据总线宽度和频率分别是WTAMi和fTAMi(i是TAM的个数),通过频率转换器后有下式成立:WATE*fATE=∑WTAMi*fTAMi.WATE和fATE是由ATE确定的,各子TAM通过调整各自的频率和数据位宽度来满足与ATE之间的带宽匹配.

图3 多频3DSoC的TAM架构

多频3DSoC的TAM架构如图3所示.由图3可知,被测电路包括IP核1与IP核2.假定ATE设备的工作频率是100MHZ,TAM的数据位宽度为1,经过频率转换器后,两个子TAM的工作频率分别设定为50HMZ和25MHZ.由于要满足带宽匹配原则,ATE的带宽和TAM的带宽在频率转换前后要保持一致,故IP核1和IP核2要进行测试外壳的封装以满足需要,外壳扫描链的个数分别调整为2和1,重构后的IP核测试外壳和TAM满足了频率转换的需要.频率转换器的实质是封装在IP核测试外壳上的硬件设备,本方案采用的是在IEEE1500测试外壳架构中加入多频控制器(Multiple Frequency Controller,MFC)来控制每个IP核的频率变化.

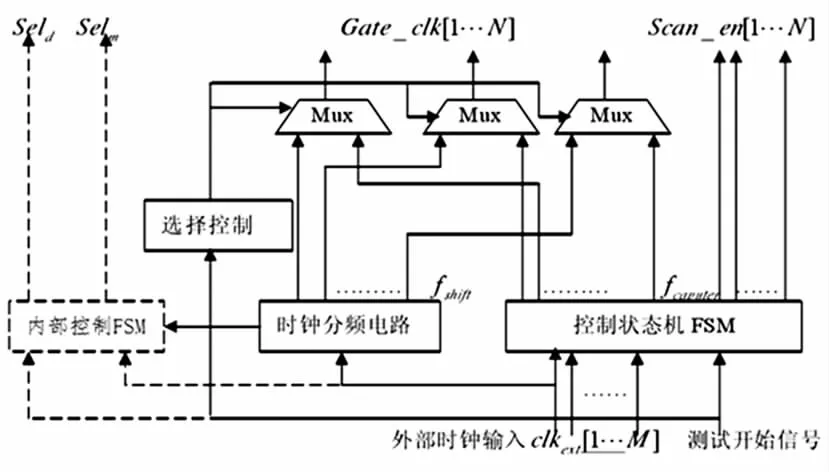

扫描控制器是多频控制器(见图4)的重要组成部分,主要的功能是产生门控时钟信号Gate_clk和使能信号Scan_en.门控时钟信号用来控制测试激励的移入,测试向量的执行以及测试响应的移出.扫描使能信号将每个IP核的测试向量按顺序执行,消除测试时钟倾斜问题.这两种信号的产生使低速TAM的时钟可以取代高速ATE的时钟成为可能.如果TAM的移位频率fTAM小于ATE的测试频率fATE,那么内部控制FSM就要为控制状态机FSM产生多路选择信号.

图4 扫描控制器

2.3 算法实现

假设一个3DSoC芯片有若干个IP核,IP核的参数包括输入输出单元个数、测试向量个数、扫描链条数以及扫描链的长度等.给定ATE提供的测试频率fATE和测试数据位宽度WATE,由于各IP核的测试频率不同,为了满足带宽匹配,必须对IP核进行测试外壳的封装,重构被测电路的TAM,在不同TAM数据位宽的限制下,结合各IP核的功耗,减少3DSoC的测试时间.

将IP核的测试扫描链按细粒度划分布局在3DSoC中,并对其进行测试.首先对所有IP核进行测试时间估算,把所有内部扫描链的输入输出端口串联成一条外壳扫描链,没有内部扫描链的IP核将其输入输出端口串接,计算一条外壳扫描链的IP核的测试时间.测试一个IP核的时间可以表示为:T={1+max(Si,So)}*P+min(Si,So),其中Si是输入外壳扫描链的长度,So是输出外壳扫描链的长度,P为测试向量的个数.根据IP核的估算测试时间进行三维空间布局,满足每个子TAM上的IP核的测试时间尽可能均衡,这样在并行测试中才能保证整个芯片的测试时间最短.这个问题在实现过程中可以转变为IP核的测试时间集合中选取任意个IP核的测试时间之和SUM与子TAM的个数之比的取法是否存在,这是一个NP完全问题.例如将IP核集分为2组,每组在其子TAM上进行测试,找出k个IP核的测试时间,使其之和最接近SUM/2,那么这k个IP核就是最优解,满足最优化原理.包含2个子TAM的最优化集合算法如图5所示.

被测IP核在并行测试时要考虑到功耗的约束,因此ATE工作频率fATE与被测电路的TAM的测试频率fTAM相比要高很多.为了在硬件中实现方便,本方案中将fATE设置为fTAM的偶数倍.例如fATE的频率设定为200MHZ,那么2个子TAM频率可分别设定为100MHZ,50MHZ,3个子TAM频率可分别设定为100MHZ,50MHZ,25MHZ.同一TAM中的IP核,在相同频率下测试.

整个芯片的测试时间取决于各个并行测试的子TAM的测试时间的最大值.由于各TAM的测试频率不同,对频率较低的TAM分配较多的测试数据位数,对频率较高的TAM分配较少的测试数据位数,采用均衡分配测试时间的原则,保证各子TAM的测试时间接近,那么芯片总测试时间最短,分配过程中保证每个子TAM的测试带宽要匹配.此外,在测试过程中还需考虑到功耗的约束,由于采用并行测试,那么各并行测试的IP核的总功耗不能超过系统的额定功耗,相应的算法如图6所示.

图5 最优化集合算法

图6 功耗限制下同一TAM的IP核测试调度

图7 本方案测试时间

文献[3]指出额定功率在1500~2500之间对d695的测试时间影响不大,故本文选择在额定功耗为2000,WTAM设置为32,40,48,56,64下d695的测试时间,实验结果如图8所示.由图8可知,随着测试数据位宽的增加,测试时间呈现递减趋势;2-TAM和3-TAM多频通道相比,2-TAM在测试时间上略占优势.因为在给定TAM下,多频通道3-TAM比2-TAM在部分数据位宽中的分配减少,导致在这些TAM中的测试时间增加,因此影响了整体的测试时间.此外,本文与文献[5-6]相比,平均测试时间分别减少了12.7%,3.5%和6.4%.

3 结论

本文提出了一种符合工业实际的3DSoC多频测试架构方案,并针对该测试架构给出了功耗限制下的测试算法.通过仿真实验的结果可以得出,在同样的数据位宽度数限制下,本方案比传统SoC相比可以获得更少的测试时间.

[1] Y Xie,G Loh,B Black,et al.Design space exploration for 3Darchitectures[J].ACM Journal on Emerging Technologies in Computing Systems(JETC),2006(2):65-103.

[2] Lee H-H S,Chakrabarty K.Test challenges for 3Dintegrated circuits[J].IEEE Design & Test of Computers,2009,26(5):26-35.

[3] 欧阳一鸣,刘蓓.一种三维SoC绑定前的测试时间优化方法[J].电子测量与仪器仪表,2011,2,164-168.

[4] Noia B,Chakrabarty K.Test-wrapper optimization for embedded cores in through-silicon via-based three-dimensional system on chips[J].Computer & Digital Techniques,IET.,2011,5(3):186-197.

[5] Iyengar V,Chakrabarty K,Marinissen.Test access mechanism optimization,test scheduling,SoC and tester data volume reduction for system-on-chip[J].IEEE Tran.On Computers,2003,52(12):1 619-1 632.

[6] Zhao D,Upadhyaya S.Dynamically partitioned test scheduling with adaptive TAM configuration for power-constrained SoC testing[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2005,24(6):956-965.