四通道数字下变频器ASIC设计

刘 翔 袁子乔

(西安电子工程研究所 西安 710100)

0 引言

DDC是软件无线电[1]的核心技术之一,它位于前端中频采样ADC与后端通用DSP器件之间,主要完成混频、滤波和重采样,将中频数字信号下变频至零中频基带信号,并使信号速率降至通用DSP器件能够处理的速率,使设计更容易实现。随着大型相控阵雷达[2]的发展和上千阵元雷达的出现,雷达前端需要大量采用ADC芯片和DDC处理通道,因此将处理过程相对简单但运算量较大的DDC模块进行ASIC设计,对于降低相控阵雷达接收通道的成本,有着非常重要的作用。

本文介绍了可配置的四通道DDC ASIC芯片的开发和设计,该DDC芯片对接ADI公司的四通道串行ADC芯片AD9633(12bit)或AD9253(14bit)的四路输出,芯片内部包括高速串并转换模块、CORDIC混频模块、多抽取率低通滤波器模块,芯片输出四个通道数字下变频后的I、Q正交信号。本文给出了基于VerilogHDL语言设计的综合与仿真结果,从仿真结果看出所设计的芯片能够满足现代雷达数字接收机设计的需要。

1 数字下变频基本原理

DDC的主要实现方法有:低通滤波法、多相滤波法[3]。低通滤波法实现简单,利用两路正交的本振信号与输入的中频信号进行混频,然后分别经过低通滤波器,可得到两路正交的基带信号,本文采用低通滤波法实现DDC。

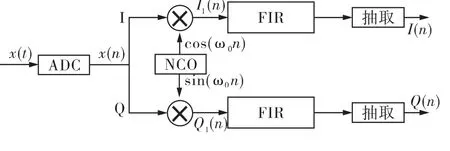

图1为低通滤波法实现DDC的结构框图,先对模拟信号x(t)进行采样,形成数字化序列x(n),然后分别与两个正交本振序列cos(w0n)和sin(w0n)相乘,再通过数字低通滤波器,最终输出正交的IQ信号。

图1 低通滤波法实现DDC的结构框图

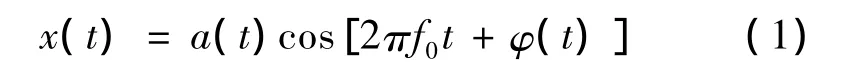

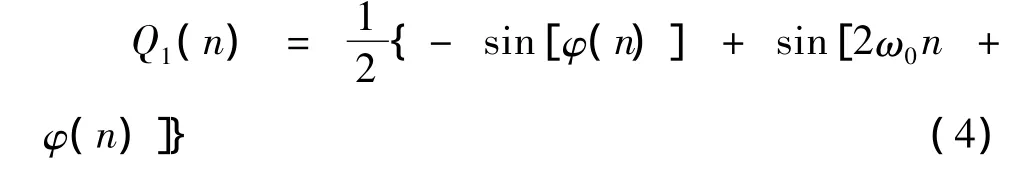

设输入的信号为:

用采样频率fs对其进行采样,得到的采样序列为:

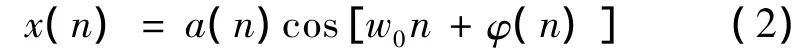

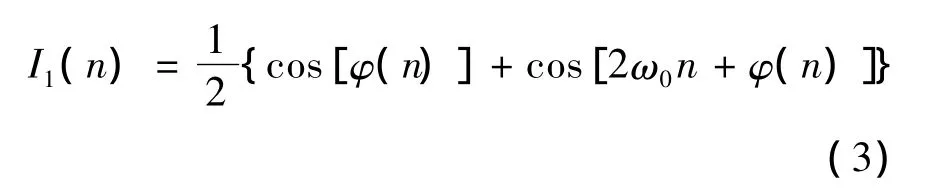

上式中ω0=2πf0/fs,φ(n)为中频信号的相位信息。NCO产生的本振为cos(w0n)和sin(w0n),对输入信号分别乘以正交的本振信号,可得到:

I路:

Q路:

经数字低通滤波器后得到基带信号:

其中I(n)和Q(n)分别表示信号的同相分量和正交分量[4]。

2 四通道DDC电路设计

2.1 四通道DDC内部结构框图

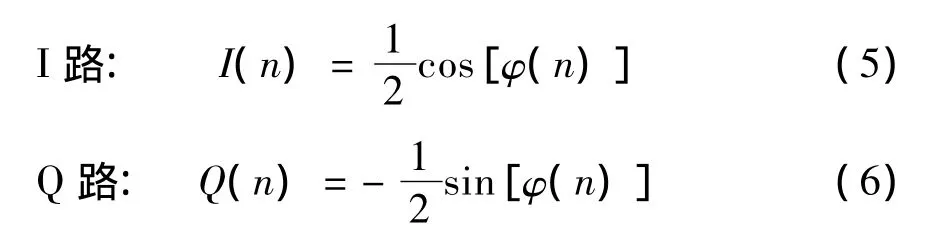

图2为四通道DDC芯片内部结构框图。DDC芯片接收ADC输出的四路LVDS串行数据,经过串并转换,将数据转换为四路并行数据;并行数据与内部数字源二选一后输入电路内部进行混频,本振信号由CORDIC算法产生;混频后的信号分两路,分别进入两个多抽取率低通滤波器,四个通道进行DDC处理后输出四路IQ正交信号,最终四路IQ正交信号并串转换为一路数据输出,由2bit通道索引区分通道号。SPI接口模块利用SPI数据线对芯片的参数和工作状态进行配置,FIR滤波器系数缓存模块用于将需要的抽取率对应的滤波器系数存入芯片内,芯片工作时从缓存中将其读出使用。

2.2 高速串并转换模块设计

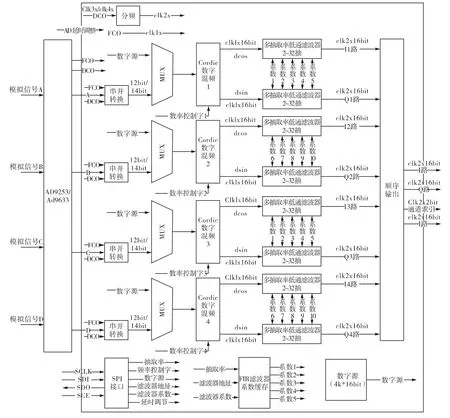

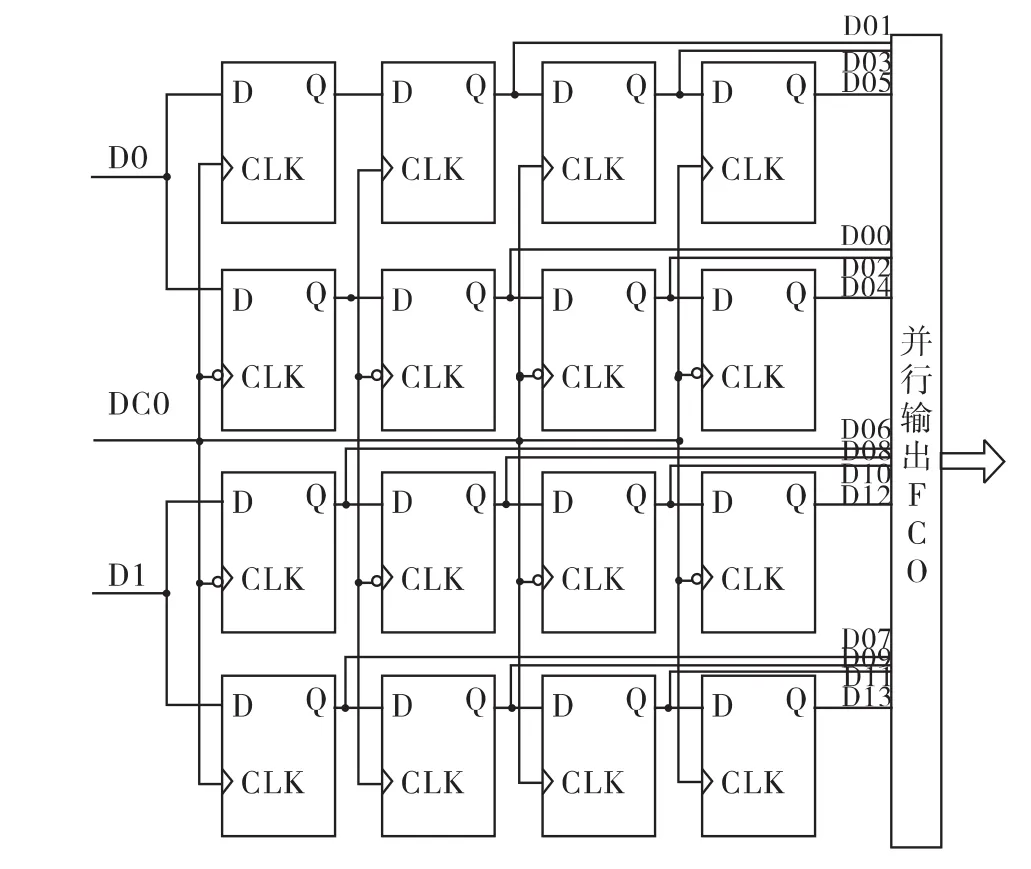

AD9633芯片工作在 DDR 模式[5]下,12bit数据分D0和D1各6bit串行输出,芯片采样率为clk1x,输出数据时钟DCO为clk3x(3倍clk1x时钟),帧时钟FCO为 clk1x。

图3为串并转换内部结构图。从图中可以看出,进行串并转换,需要使用数据时钟DCO分别在上升沿和下降沿采集信号,并对采集的信号进行延时对齐,最终由帧时钟FCO同步并行输出。对于该转换模块,由于时钟频率高,数据延迟小,所以将高速串并转换做成一个硬IP模块,单独进行布局布线,防止电路内部其他模块对其产生串扰影响。

2.3 CORDIC 混频算法[6]实现

图4为CORDIC混频算法流程,输入频率控制字,经过相位累加、象限变换、16级Cordic流水运算,输出对应频率控制字的正余弦值,再分别与输入的中频信号进行混频,输出两路混频结果。

由频率控制字计算当前相位值,CORDIC算法目标角度的取值范围为[-99.9o,99.9o],而在很多场合中需要目标角度可以覆盖[-180o,180o],因此需要对目标角度进行预处理,即象限变换,表1给出了预处理前后的变化值。变换后结果经16级CORDIC算法旋转后可给出输入角度的正余弦值。需要说明的是每级旋转后幅值会增大,16级旋转其幅值将增大1.648倍,若需消除其影响可在数据输入端对数值进行相应倍数缩小。

2.4 多抽取率滤波器模块设计

电路经过混频后,需要对信号进行整形滤波,电路中设计一个多抽取率的FIR低通滤波器[7],滤波器模块主要包括32级移位寄存器组、数据整理单元、乘法累加器及求和单元。

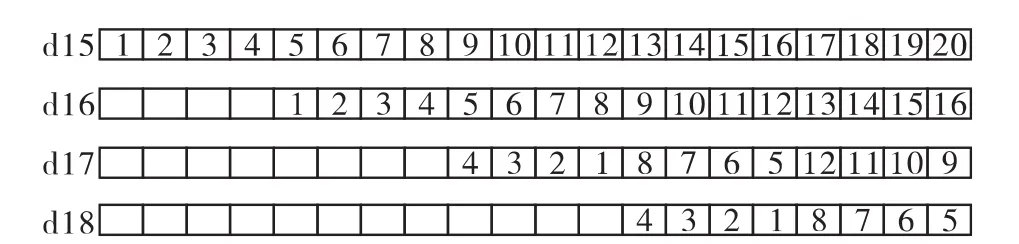

从图5可以看出,从d0到d16、d17到d32使用移位寄存器SRL进行数据延时,延时周期为抽取率,例如4抽取时,延时4个时钟周期。反序是将输入数据的顺序以每抽取个数为一组,按照相反的顺序输出。图 6可以看出,4抽取率下,d15到d16、d17到d18使用SRL延迟4个时钟周期,d15到d17采用反序延迟,数据延迟4个时钟周期且反序输出。

图2 四通道DDC芯片内部结构框图

图3 串并转换内部结构图

图4 CORDIC混频算法流程

表1 目标角度预处理机制

图5 多抽取率低通滤波器输入数据流

图6 4抽取下的数据流

图7 多抽取率低通滤波器

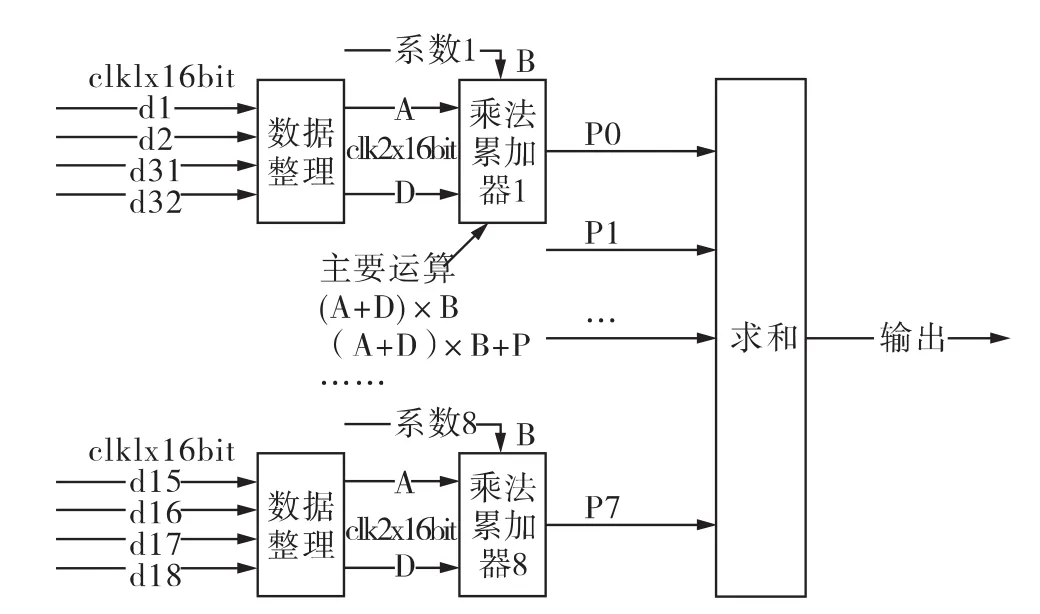

从图7可以看出,使用移位寄存器产生指定时序的数据流后,可以进入数据整理模块和乘累加模块。数据整理是将两个clk1x数据率的数据整合为一个clk2x的数据率的数据,提高后续乘累加的工作频率,可以节约一半乘法器资源,从图8可以看出此过程,在数据整合过程中使用flag区分d1和d2。当滤波器系数对称时,可通过预先加法将对称位置的数据相加,然后与对应的滤波器系数进行乘累加运算,这样可以减少一半乘法器资源。

乘累加模块利用bypass信号标识一组乘累加运算数据的第一个数,求和单元主要将8个乘累加运算结果进行相加,输出结果即为输入数据数字下变频的结果。

图8 4抽取时数据整理时序图

2.5 总体仿真

为了验证所设计的四通道DDC ASIC的性能,输入不同形式的信号,采用不同抽取率DDC进行处理,对输出信号进行分析验证DDC性能是否满足设计要求。

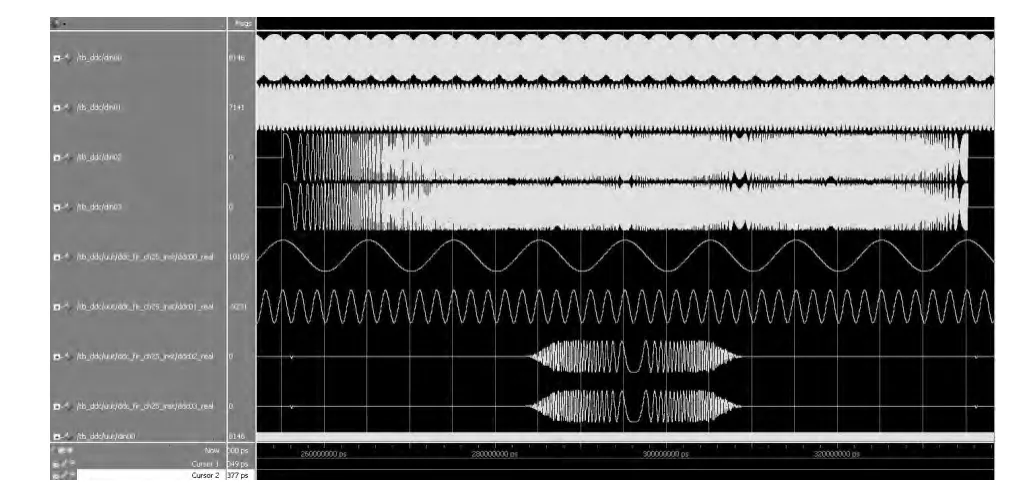

仿真条件1:A、B通道输入为正弦信号,输入频率分别为20.1MHz、20.5MHz,C、D通道为线性调频信号,中心频率为20MHz,带宽为40MHz,时宽为80μs,四个通道信号采样率都为80MHz,本振频率为20MHz。抽取率为4,滤波器阶数为128阶,设计滤波器通带截止频率为4MHz,阻带起始频率7MHz,阻带衰减大于60dB,通带内起伏小于0.1dB,频率响应如图9所示。

图9 4抽取128阶滤波器频率特性

图10 四通道输入输出信号波形仿真图(4抽取)

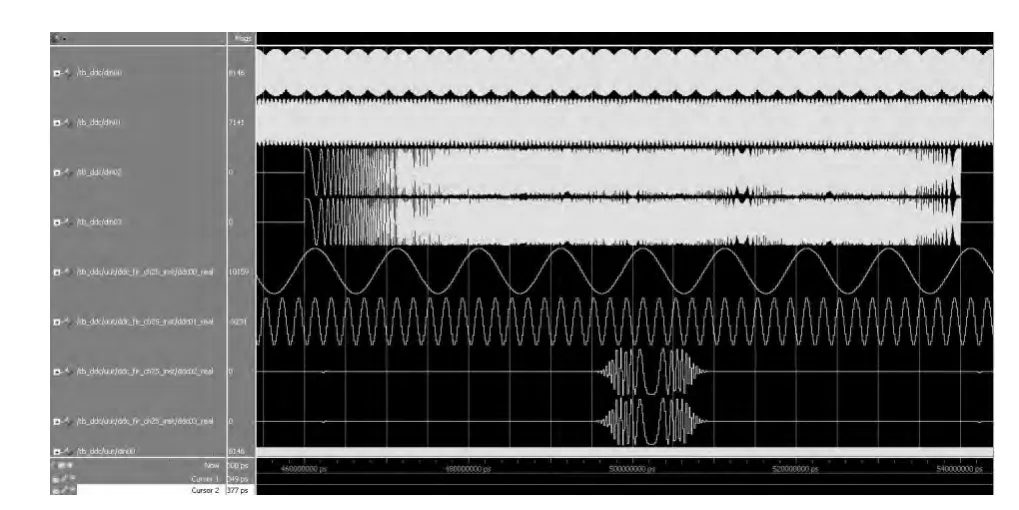

图10为四通道输入输出信号的波形仿真图,4抽取后,信号的数据率变为20MHz,从图中可以看出A、B通道输入为点频信号,经过混频滤波处理,分别得到0.1MHz、0.5MHz的正弦波,每个正弦周期内各有200、40个点;C、D通道输入线性调频信号,经过混频滤波后,滤除了不需要的频率分量,从线性调频信号最终输出为椎体形状,两端频率被滤掉,由小变大过程为过渡带,中间幅度相同的部分为通带,与设计的低通滤波器特性相匹配。仿真条件2:A、B、C、D四通道输入信号形式与仿真条件1中相同。本振频率为20MHz,抽取率为10,滤波器阶数为320阶,设计滤波器通带截止频率为2MHz,阻带起始频率4MHz,阻带衰减大于60dB,通带内起伏小于0.1dB,频率响应如图11所示。

图11 10抽取320阶滤波器频率特性

图12 四通道输入输出信号波形仿真图(10抽取)

从图12可以看出,10抽取后,信号的数据率为8MHz,对于A、B通道正弦信号下变频为0.1MHz、0.5MHz的正弦波,每个正弦周期内各有80、16个点;对于C、D通道,可以看到由于10抽取滤波器的通带变窄,因此C、D通道线性调频信号的输出相比与4抽取时的输出,信号的时宽变得更窄了,从图中也能看出低通滤波器的通带、过渡带和阻带的频率特性。

3 结束语

本文提出了一种四通道数字下变频器ASIC设计的方法。此ASIC芯片可以对接ADI公司四路串行ADC,通过串并转换模块、CORDIC混频模块、多抽取率低通滤波模块,可以实现数字下变频功能,满足雷达信号处理大部分情况的使用要求,且采用优化的结构降低了芯片功耗和设计复杂度。

[1]杨小牛,楼才义.软件无线电原理与应用[M].北京:电子工业出版社,2005.

[2]张光义.相控阵雷达系统[M].北京:电子工业出版社,1994.

[3] 屈有萍.基于FPGA的数字下变频研究实现[D].西安:西安电子科技大学,2007.

[4]伍小保.数字阵列雷达数字下变频器ASIC芯片设计[J].雷达科学与技术,2008,6(6):496-500.

[5]Analog Devices Inc.AD9633 Quad,12-Bit,80 MSPS/105MSPS/125MSPS,Serial LVDS 1.8V ADC[M]. USA:Analog Devices Inc,2011.

[6]Ray Andraka.A Survey of CORDIC Algorithms for FPGA Based Computers[A].Proceedings of the 1998 ACM/SIG-DA 6th International Symposium on FPGA[C].1998:191-200.

[7]袁子乔.一种任意抽取数字下变频器的设计[J]. 火控雷达技术,2013,42(3):66-69.