LTE辅同步检测低复杂度算法设计及实现

马 飞,赵永祥,郭年庚

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.中国工程物理研究院电子工程研究所,四川绵阳621900;3.北京科技大学计算机与通信工程学院,北京100083)

0 引言

LTE是3GPP组织为保持其在未来十年的竞争力而提出来的,因其能够提供更高的数据传输率、更大的系统容量以及支持全IP业务和可伸缩带宽配置的优点,而被世界主流运营商选为未来网络建设的制式标准。

在LTE通信系统中,小区搜索是一个非常重要的过程。移动终端开机后,首先需要进行初始小区搜索,完成同基站之间的时间和频率同步并提取出广播信息,之后才能进行正常的通信[1]。LTE系统采用了两级同步信号进行小区搜索的方案,即主同步信号进行5ms定时和获取扇区号,辅同步信号进行10ms定时和获取小区组内ID号[2,3]。

辅同步信号检测是其中的一个重要过程,目前针对辅同步信号检测所提出的算法基本思想都是采用序列相关寻找匹配序列[4,5],由于LTE辅同步信号序列每5ms发送一次,前后2个5ms发送的辅同步序列不一样,因此也就只有利用第1个5ms半帧的辅同步序列进行检测和利用2个5ms半帧的辅同步序列进行检测2种方法,主要进行5ms半帧序列的检测,介绍了提出的一种便于硬件实现的低复杂度序列检测方法,给出算法数值仿真性能,接着对算法进行硬件设计和FPGA实现[6-10]。

1 辅同步信号产生

图1是LTE系统的FDD模式帧结构,一个无线帧在时域上占用10ms的时间,每个无线帧由20个时隙构成,一个时隙长度为0.5ms。按照LTE的协议标准,主同步信号和辅同步信号分别位于slot#0和slot#10的最后一个OFDM符号和倒数第2个OFDM符号上,在频域上映射到中间的62个子载波上,两端各插入5个空子载波用于保护同步信号。LTE系统中共有504个不同的小区ID号,唯一标识系统中的基站小区,这504个小区ID又被分为168组,编号从0到167,记为小区组号,每组含有3个小区号,编号从0到2,记为扇区号和共同决定小区ID号,即

图1 FDD帧结构

D(2n)和D(2n+1)分别称为偶序列和奇序列,c0(n)和c1(n)是m序列,由主同步序列决定,按照式(2)产生:

式中,c(n)是由0和1构成的二进制m序列,因此,c0(n)和c1(n)可以看成是由基本m序列c0(n)线性移位和得到。

s(m)(n)和z(m)(n)序列是扰码序列,也是二进制m序列线性移位m得到,因此辅同步序列是扰码后的m序列。

2 辅同步检测算法

2.1 全搜索检测算法

辅同步序列号可根据式(2)计算得到:

该算法需要遍历336组候选序列,每次遍历需要进行长度为62的相关计算,因此该算法的计算量较大,复杂度高。

2.2 低复杂度的辅同步信号检测算法

提出一种新的辅同步信号检测算法,该算法核心思想是对一个5ms帧的辅同步序列进行1bit量化,同时将偶序列和奇序列分开检测,此时相关长度为31,遍历次数为31加14,因此相对于上面提到的全搜索算法,在搜索时间和实现复杂度上都具有优势。下面介绍该算法的检测过程。

由于辅同步信号映射到中间的62个子载波上,因此在完成主同步信号检测之后,也即确定了主同步信号的位置之后,推断出辅同步信号所在的位置,从该位置作为起始FFT变换位置将辅同步信号变换到频域,提取出中间62个子载波数据分为偶序列和奇序列2组,分别记为r(2k)和r(2k+1),k=0,1,…,30。

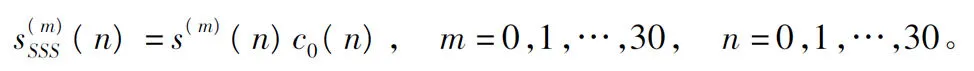

同时,对接收到的偶序列和奇序列进行1bit量化,量化之后的序列分别记为qr(2k)和qr(2k+1),然后就可以进行偶序列的检测,方法是首先产生31组长度为31的本地偶序列,本地偶序列按下式产生:

式中,s(m)(n)和c0(n)是二进制m序列,按照LTE协议标准生成。将本地偶序列和量化后的接收辅同步偶序列qr(2k)进行相关,得到31组相关集,记为C0(m),即:

对应估计到的m值为:

根据式(3)和式(4)即可完成偶序列的检测,并确定偶序列编号,之后根据偶序列的检测结果进行奇序列的检测,方法不同的是不需要遍历产生31组奇序列,而是根据偶序列和奇序列的关系,只需要遍历产生14组奇序列即可,因此本地奇序列按下式产生:

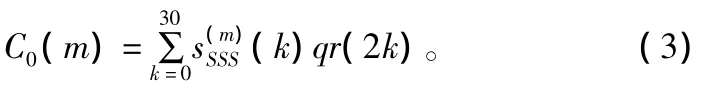

将产生的14组本地奇序列同量化后的序列r(2k+1)进行相关,得到14组相关集合,为C1(m),即:

奇序列检测估计得到的m值根据下式计算得到,即:

至此,完成偶序列和奇序列的检测。并不知道利用的是10ms无线帧中的第1个5ms帧还是第2个5ms帧的辅同步数据进行的辅同步检测,因此,m0和m1值由下式得到:

从提出的辅同步信号检测算法检测过程可以看出,完成辅同步信号检测共需要进行31+14次长度为31的相关运算即可确定小区组号,与之前采用全搜索算法需要遍历所有336组辅同步序列相比,复杂度大大降低。同时由于在检测开始前就进行了接收序列的1bit量化,因此相关计算单元在进行FPGA实现时可以用异或电路实现,而不是利用乘法器,这可以进一步降低实现的复杂度。综上所述,提出的算法更利于硬件实现。

2.3 算法仿真结果

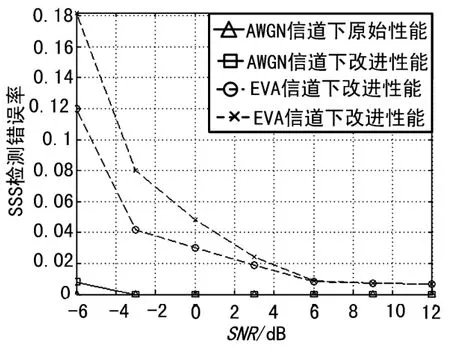

为了评估提出算法的性能,在Matlab仿真平台下,对2种算法进行仿真,系统仿真参数如表1所示,在仿真开始前,假设小区ID号为167,扇区号为2,根据这2个值和表1的仿真参数生成含有辅同步信息的基带信号,利用上文提到的2种算法进行基带信号的解调,并进行辅同步检测,将检测得到的结果与假设值比较,若一样,则记这次检测成功,否则这次检测失败。连续发送1000帧数据,统计检测失败的概率,最后的仿真结果如图2所示。

表1 系统仿真参数

图2 两种算法在AWGN和EPA信道下的性能

由于提出的算法是对传统算法进行了简化,以降低硬件实现复杂度,这必然会带来性能的损失,从图2的仿真结果也可以看出,提出的简化算法在2种信道环境下都有一定性能损失。在AWGN信道和高信噪比下,即-3dB以上时,二者性能接近,在-6dB时全搜索算法也最多只有6%的性能优势。考虑到全搜索算法付出的实现复杂度和搜索时间的代价,提出的算法在硬件实现上更利于小区搜索实现。特别是在高信噪比环境下,本文提出的算法能以较低的实现复杂度和较短的搜索时间满足LTE终端小区搜索的需求。

3 辅同步检测FPGA实现

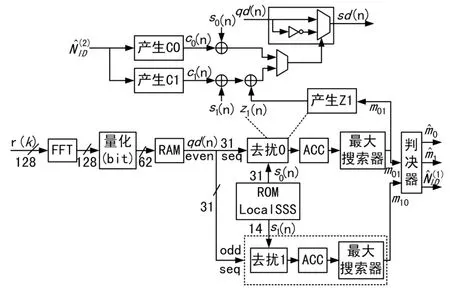

提出的辅同步信号检测算法总体结构如图3所示,接收到的序列首先通过FFT变换到频域,之后进行1bit量化,将量化后的中间62个子载波数据写入RAM,供后续的序列检测电路读取,后续的序列检测电路主要由扰码产生和解扰电路、累加器和最大值搜索电路构成。

图3 辅同步信号检测总体结构

扰码产生电路可以通过将扰码序列写入ROM中,在需要解扰操作时,从ROM中读取,由于其他扰码序列都可以看成基本扰码序列的线性移位,因此只需要存储3种基本的扰码序列c(n)、s(n)和z(n)即可,当需要线性偏移m位的序列时,从起始地址为m的存储单元开始读取即可,如图4所示。

图4 扰码序列产生

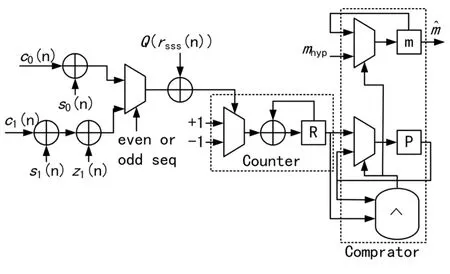

序列检测电路若采用并行检测的方法,则每个序列都需要一个检测器,相关计算得到的结果还要送往最大值搜索模块,实现将十分复杂。同时占用资源也比较多,因此可以将序列分时检测,寄存检测得到的值,同时扰码和相关计算单元可以通过复用选择器和双向计数器实现。简化后的序列检测电路如图5所示,通过1bit异或电路之后的本地序列与量化后的序列进行1bit异或,若二者符号一样,则计数器正向加1,若和本地序列完全匹配,则会连续31次正向加1,此时会得到最大值,每31次计数之后与寄存器P的值比较,若计数器值大,说明此次检测序列的相关值比上次检测大,此时更新寄存器P的值并更新对应的序列编号m值,当所有可遍历的序列都检测完之后,寄存器m中寄存的就是对应匹配到的辅同步序列编号。

图5 序列检测电路

按照上述的结构对辅同步信号检测进行FPGA实现,通过Modelsim进行功能仿真,辅同步模块先后进行偶序列和奇序列的检测,计数器的初始值设置为32,仿真输出结果为当序列完全匹配时,计数器正向加了31次,因此峰值寄存器peak在两个检测阶段输出的峰值都为32+31=63,并同时输出偶序列和奇序列对应的序列号,表明辅同步检测模块完成序列检测,因此功能实现正确。

最后选用Xilinx的V5SX95T芯片在ISE里进行综合实现,ISE给出的资源量使用情况,如表2所示。从该表可以看出,寄存器资源利用率2%,LUT资源利用率1%,都比较小,DSP48E用到8个,这主要是利用了FFT IP核,这会使用大量的DSP48E资源,因此整个辅同步检测消耗资源并不多。

表2 辅同步信号检测资源量分析

4 结束语

辅同步信号检测是LTE小区搜索一个重要检测过程,给出了一种复杂度较低的辅同步信号检测。仿真结果表明,该算法相对于全搜索算法有一定的性能损失,但是降低了计算复杂度,特别是在高信噪比环境下,这种性能损失很小,完全满足工程需求,同时进行了辅同步信号检测硬件结构的设计,并进行了RTL代码编写和功能验证,Modelsim仿真结果表明,对算法进行的硬件简化工作是可行的。

[1]WANG Feng,ZHU Yu,WANG Zongxin.A Low Complexity Scheme For S-sCH Detection in 3GPP LTE Downlink System[C]//Shanghai,2010 Global.Mobile Congress,2010:1-6.

[2]3GPP R1-061662,SCH Structure and Cell Search Method for E-UTRA Downlink[S].

[3]KIM J I,HAN J S,ROH H J,et al.SSS Detection Method for Initial Cell Search in 3GPP LTE FDD/TDD Dual Mode Receiver[C]// Korea,SAMSUNG ELECTRONICS CO,LTD,2009:199-203.

[4]钱春光,于忠臣.LTE系统辅同步信号检测算法研究[J].科技信息,2012(11):112-113.

[5]郝庭基,尹长川,罗涛,等.LTE系统帧定时同步的低复杂度FPGA实现[M].北京:人民邮电出版社,2011:327-331.

[6]史治国.基于Xilinx FPGA的OFDM通信系统基带设计[M].浙江:浙江大学出版社,2009.

[7]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2009:12-13.

[8]Virtex-5 Family,Xilinx Advance Product Specification DS100[M].USA:Xilinx,2008.

[9]夏宇闻.Verilog数字系统设计教程(第2版)[M].北京:电子工业出版社,2008:3-5.

[10]CILETTI M D.Verilog HDL 高级数字设计[M].张雅绮,李锵,译.北京:电子工业出版社,2003:2-5.