模拟集成电路频率特性自测试技术研究

葛 勇,薛 冰,王聪丽

(武警石家庄士官学校,河北 石家庄 050061)

由于模拟信号本身参数多、信息丰富[1],在对信号处理的过程中,除了需要像数字电路那样考虑信号的延迟,还要考虑信号失真、电路自激、频率损失等问题,所以对于简化模拟电路测试系统有较大的难度[2]。在研究过程中发现,模拟集成电路的众多性能参数都与频率有关[3-8],因此考虑选择利用频率极为丰富的脉冲信号为研究对象[9],选用脉冲测试技术为核心技术展开研究。除了脉冲信号包含有丰富的频率信息外,脉冲信号还有利于信号的数字化,可大幅度简化测试电路的优势。脉冲信号经过模拟电路系统后,可以通过其频率响应的变化情况来检测该系统的频率响应、能量传输效率等关键指标,可得到该电路的部分核心性能。

1 脉宽测试法与频率特性

1.1 脉冲参数与频率特性的关系

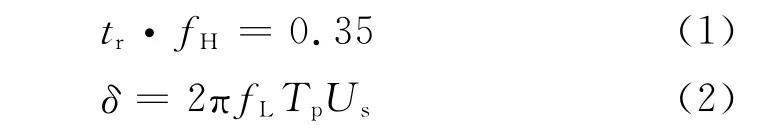

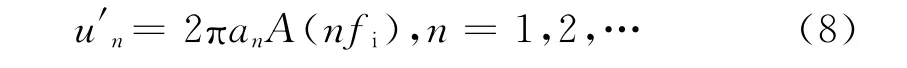

在图1表示中脉冲波形中,δ表示脉冲的顶降,tr表示脉冲的上升时间,tf表示脉冲的下升时间。脉冲信号经过模拟电路后,其参数与模拟电路频率响应有如下的关系[10]:

式中,fH表示模拟电路的上限频率,Tp表示脉冲信号的宽度,Us表示输入的脉冲信号的幅度,fL表示模拟电路的下限频率。

在工程中,fL≪fH[11],因此,在考察模拟电路的频率响应时,通常仅测试上限频率就可以了。根据式(1),可以把上限频率的测试转换成脉冲信号上升时间的测试。

图1 脉冲波形

相比直接测量,脉宽测试法能够延长被测时间,可降低对计数脉冲频率的要求;同时仅需设定一个电压比较阈值0.1Uom,降低了测试过程中辅助电路的资源占用率,减少了硬件需求量,提高了测试的可行性。

1.2 激励脉冲参数的选择

1.2.1 频率选择条件

(1)条件1:被测电路的上限截止频率fH应大于激励脉冲的基波频率fi,并小于激励脉冲8次谐波的频率,即

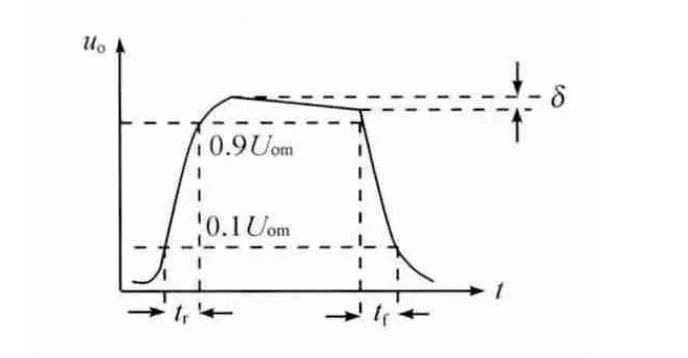

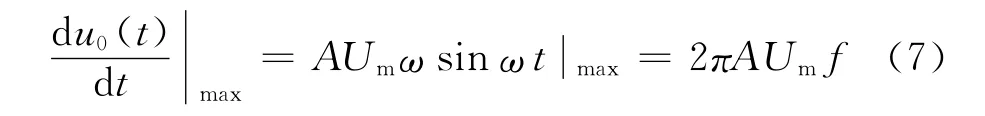

理想的脉冲信号包括无穷多频率成分,是各种频率的正弦波和余弦波的叠加[5]。矩形脉冲f(t)可以分解为以下频率成分:

式(4)中,第1项a0是直流成分,第2项称为基波,其他各项统称为高次谐波[12]。式(5)中,an是n次谐波分量的幅度,Um为脉冲幅度,tp0.5为脉冲宽度,T为脉冲周期。

信号与系统理论中认为,当n次谐波的幅度小于基波幅值的1/10时可忽略不计,加上脉冲信号频率分量仅有基波的偶次倍,因此,可以认为脉冲信号占有8fi的频带宽度,此处fi代表基波频率。

本文提出的脉冲测试方法以激励信号通过被测电路前后频率成分的变化为主要特征。当激励信号频率高于被测电路截止频率时,测试信号将全部被电路滤掉以致无法检测到;当激励信号的8次谐波频率分量仍小于被测电路截止频率时,测试信号将全部通过被测电路。这两种情况下的均无法测得正确的结果,因此条件1是必要条件。

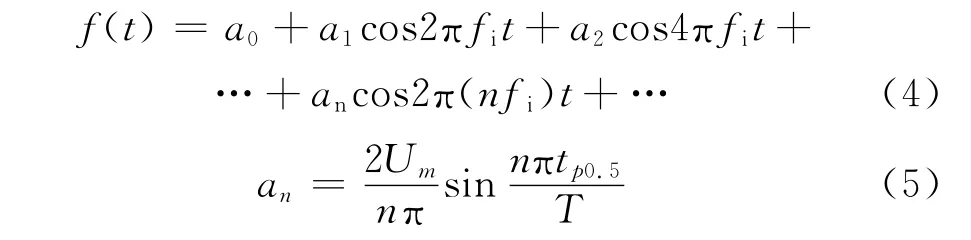

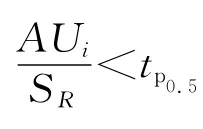

(2)条件2:激励信号的最大变化速率须小于被测电路(运放)的转换速率SR,有

若在运放的输入端加一余弦电压ui=Umcosωt,则输出电压为uo=-AUmcosωt,A为放大倍数,此时输出电压最大变化速率为

由式(4)可知,脉冲信号可分解为多个余弦信号之和,每一个频率分量的最大变化速率为

则周期矩形脉冲信号的最大变化速率 u′f(t)=max(u′n)。

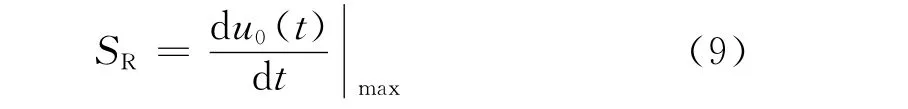

转换速率是指放大电路在闭环状态下,输入信号为大信号时,放大电路输出电压对时间的最大变化速率[13],即

当运放的转换速率SR不能跟上输出信号电压波形的变化时,就造成输出波形的失真,进而影响到建立时间tr以及截止频率fH的测试。因此要保证输出电压波形不失真必须满足u′f(n)<SR,变形后即为式(6)。

另外,还应确保输出信号上升时间小于激励脉冲宽度,否则输出信号将无法正常上升到最大值。这一点与信号幅值、电路增益有直接关系,所以激励信号的幅度也需要加以限定。

1.2.2 幅度的选择条件

2 测试方案设计

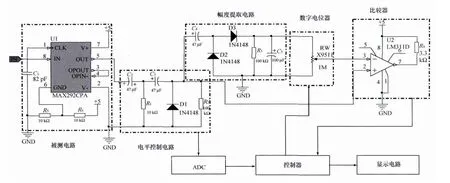

设计的脉宽测试法测频率响应的测试系统框图如图2所示。通过把一定频率和幅度的方波信号作为测试电路的激励源送入被测电路,通过提取被测电路响应信号的建立时间,进而达到测试电路频率特性的目的。

图2 模拟集成电路测试系统框图

各部分的作用如下:

(1)方波产生器:产生被测电路需要的一定频率、一定幅度的方波信号。

(2)外围辅助电路:由于被测为模拟集成电路,需要外围的电阻、电容支持,才能实现其功能或某种功能。

(3)电平变换电路:把被测集成电路输出的脉冲信号变换为低电平为零电平的脉冲信号。

(4)幅度提取电路:提取出脉冲信号的幅度。

(5)10%Um或90%Um电平产生电路:把提取到的脉冲幅度Um经过电阻分压电路,得到10%Um电平或90%Um电平,作为比较器的基准信号。

(6)比较器电路:以前面产生的基准信号为基准,与电平变换电路送出的脉冲信号进行比较,得到该脉冲信号10%Um处的脉冲宽度或90%Um处的脉冲宽度,其输出的信号是TTL电平的脉冲信号。

(7)脉宽测量电路:用来测量比较器电路送来的脉冲信号的宽度。进而在显示电路上显示出被测集成电路响应信号10%Um处的脉冲宽度值或90%Um处的脉冲宽度值。

由脉宽测量电路中得到系统建立时间后就可以根据式(3)计算出被测电路的上限频率(即被测电路的频率响应)。

3 实验验证

3.1 测试方法的验证

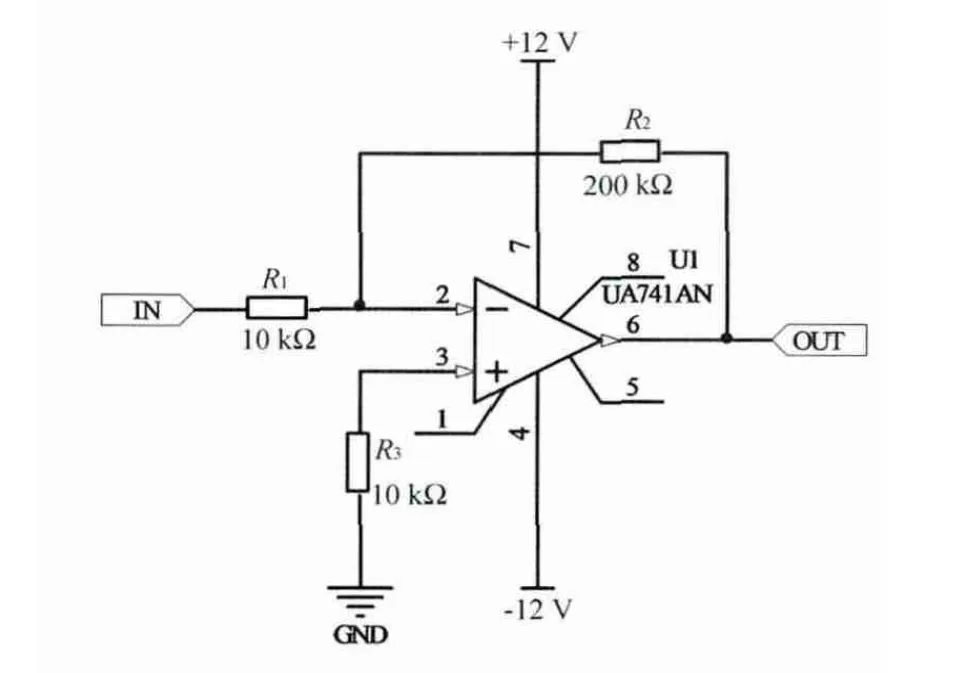

为了验证通过测试脉冲响应信号的脉冲宽度得到脉冲上升时间的正确性,我们用通用集成运算放大器μA741搭接了一个放大电路和一个低通滤波器电路,分别见图3和图4。

图3 电压放大器电路

用Tek AFG3101函数信号发生器和Tek APO4054B示波器构成实验环境。

(1)对电压放大器电路的测试。首先以正弦波为激励信号,采用点频法测得电压放大器的上限频率为45kHz。然后,以fi=10kHz、Uim=100mV方波为激励信号,直接用游标在示波器上测试上升时间,得tr=7.5μs,下降时间tf=7.5μs。计算上限频率为fH=46.7kHz。

图4 低通滤波器电路

再后,用游标在示波器上测试0.1Um处的脉冲宽度tP0.1=57.60μs。计算得到tr=tP0.1-tP0.5=7.6μs,得fH=46.1kHz。

(2)对低通滤波器电路的测试。按照测试电压放大器电路的步骤,得到以下结果:

点频法:低通滤波器的截止频率fc=405Hz。

用频率为50Hz、幅度为1V方波信号作激励信号,直 接 测 上 升 时 间,得 tr=830.0 μs,计 算得fc=422Hz。

测试0.1Um处的脉冲宽度tP0.1=10.85ms,得tr=tP0.1-tP0.5=850μs,得fc=412kHz。

3.2 测试方案的验证

图5为验证本文提出的测试方案所设计的实验电路。从所选择的电路形式可看出,贯彻了用于测试的辅助电路最简的原则。该实验电路用单片机构成了一个自动测试系统,测试对象选择了单片模拟滤波器芯片MAX292,测试系统的工作频率为12MHz,所产生的计数脉冲频率为1MHz。

被测集成电路输出的脉冲信号上会叠加直流分量,所以其低电平不是零电平,这对后续的电平提取和比较造成极大不便。因此,设计了电平转换电路把该信号变换为低电平为零电平的脉冲信号。

图5中幅度提取电路采用了倍压检波电路的形式,通过电容C4保持住脉冲信号幅度。考虑到脉冲信号的幅度有正、有负,因此采用倍压电路,保证在电容C4得到的电平为正、负幅值之和。

图5 模拟集成电路自测试电路

图5中的电平控制电路、幅度提取电路、比较器电路均是用于测试的辅助电路,它们的作用如前所述。虽然这仅是一个实验电路系统,但为了体现内建自测试系统的要求,这些电路均采用了最简电路形式(主要由电阻、电容和二极管组成)。这样一来,必然对测量的准确性造成一定影响,如二极管的开启电压、数字电位器的量化误差等。当然,由于这些影响均造成的是系统误差,可以通过单片机系统进行修正。下面通过采用传统测试方法和由单片机构成的自动测试系统,对其测试的正确性进行验证。

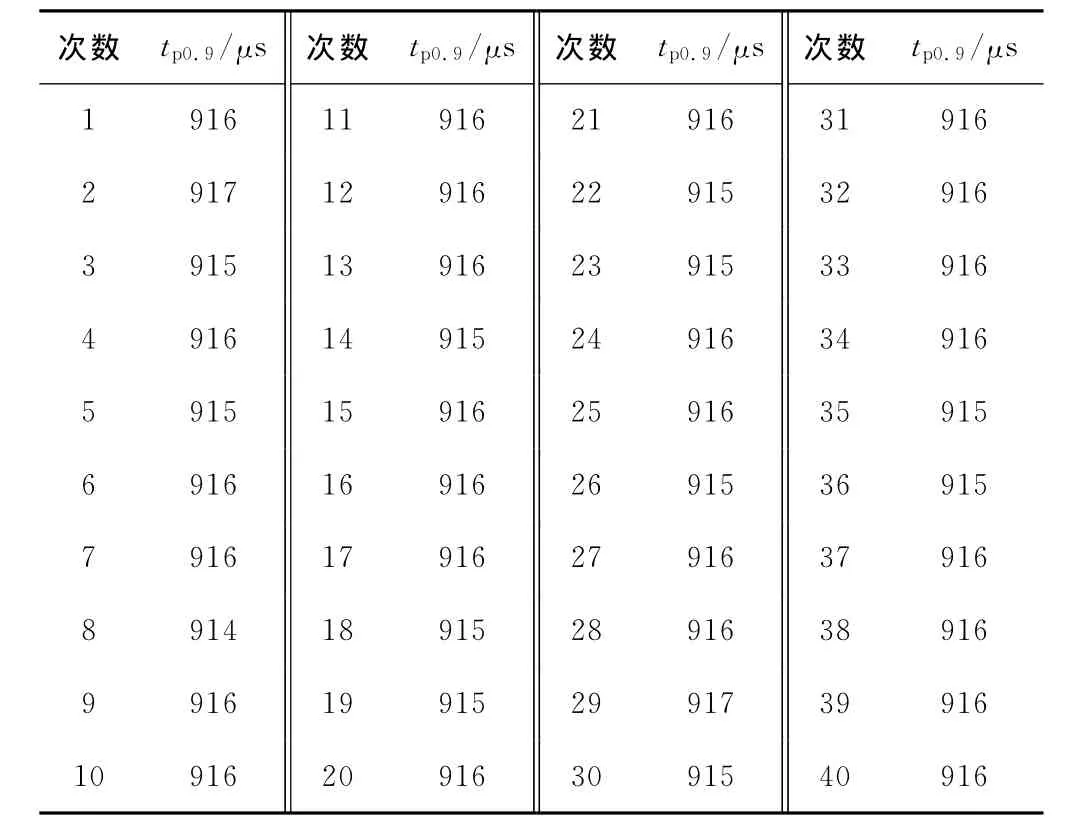

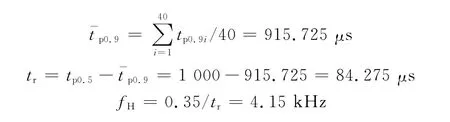

为了保证测试的准确性,采用了多次测试的方法,分别测试了MAX292脉冲响应信号0.1Uom和0.9Uom处的脉冲宽度,测试数据见表1和表2。

表1 0.1Uom处的脉冲宽度数据

表2 0.9Uom处的脉冲宽度数据

4 方法正确性分析

通过用μA741搭接的放大电路和低通滤波器电路的实验,验证了本文提出方法的正确性。该实验中,首先用测试频率特性的经典方法——点频法进行测试。点频法采用的激励信号为正弦信号,它测试的准确性主要依赖于所选测量仪器的精度。我们选用的示波器和信号发生器均是性能较高的测量仪器,因此测出的上限频率的数据是准确的,可以把它作为准确值来用。接下来,分别采用直接测试上升时间的方法和本文提出的测试0.1Uom或0.9Uom处脉冲宽度得到上升时间的方法,得到上限频率。分别对照点频法得到的上限频率进行误差计算。

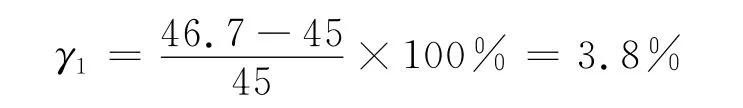

电压放大器的上限频率测试误差:

直接测上升时间方法的误差γ1为

先测量脉冲宽度的方法的测试误差γ2为

低频滤波器电路的上限频率测试误差:

直接测上升时间方法的误差γ1为

先测量脉冲宽度的方法的测试误差γ2为

从以上的误差计算可以反映出,测量误差均小于5%,可以说无论是直接测上升时间还是用本文提出的先测量脉冲宽度,再换算成上升时间的方法,均能较准确地得到上限频率。另外,从数据上还反映出,本文方法的测试准确性稍高于直接测上升时间的方法,其原因是人为因素造成的。由于用示波器直接测上升时间,需要首先调整被测脉冲在示波器显示屏上占满5格,这样才能定位0.1Uom和0.9Uom的位置,然后,再把脉冲上升沿在屏幕上充分展开,测量才比较准确。然而,脉冲信号经过放大器(或滤波器)电路后,波形的高、低电平不会严格的一致,会发生一些变化,因此调整5格会出现偏差,从而造成一定的测量误差。而测试脉冲的宽度时,该影响相应就要弱一些,只要求找准0.1Uom或0.9Uom的位置就可以了。因此,从测量数据上表现出测脉冲法比直接测上升时间法要准确一些。

(

)

[1]Sunter S,Nadeau-Dostie B.Complete contactless I/O testing:reaching the boundary in minimizing digital IC testing cost[C]//Proc Int’l Test Conf(ITC 02).2002:446-455.

[2]朱振军,林明,宋月丽.基于边界扫描技术的板级测试分析[J].电子设计工程,2012,20(9):127-129.

[3]Robert J.A method of extending an 1149.1bus for mixed-signal testing[C]//International Test Conference.1996:410-416.

[4]Kenneth P Parker.The Boundary-scan handbook second edition[M].Kluwer Academic Publishers,New York,Boston,Dordrecht,London,Moscow,2002.

[5]Chen Xiaomei,Meng Xiaofeng,Zhong Bo Application of boundary scan idea on analog circuit specialty testing[J].Sixth Intl.Symp on Instrumentation and Control Technology,2006(6358):271-277.

[6]Mohammed Ali Abdel.An anlog mixed-signal controller[C]//The 45th Midwest Symposium on test.2002:384-387.

[7]冯长江,李晓峰.模拟电路边界扫描功能性测试模型研究[J].计算机测量与控制,2011,19(10):2337-2339.

[8]IEEE.IEEE Standard for mixed-signal test bus[M].Institute of E-lectrical Engineers,Inc,2000.

[9]Hannu J,Häkkinen J,Voutilainen J V,et al.Current State of the Mixed-Signal Test Bus 1149.4[J].Journal of Electronic Testing,2012,28(6):857-863.

[10]Lin H,Hou Z,Yao F,et al.The Study of Design for Testability on Analog Circuit Based on Boundary-Scan[C]//Computer Science& Service System (CSSS).2012International Conference on IEEE,2012:195-198.

[11]Feng Changjiang,Xue Bing.A Method for Analog Integrated Circuit Embedded Self-test[J].Applied Mechanics and Materials,2013,817:1069-1072.

[12]李白,舒鹏飞,杨静竹,等.集成运放参数测试仪[J].科技创新导报,2009(19):218.

[13]李杰,杨军,李锐,等.一种实现数模混合电路中ADC测试的BIST结构[J].微电子学,2004,34(4):466-468.