ICE中调试模块IP软核的设计与实现

江正斌,周建伟,李德安,彭崇梅,袁国顺

(1.河北工业大学 微电子研究所,天津300130;2.北京中科微电子技术有限公司 研发部,北京100029;)

随着片上系统集成度越来越高,嵌入式技术得到广泛应用,尤其是在消费电子产品中的应用,芯片在线仿真器(In-Circuit Emulator,ICE)的研发也变得越来越重要,然而市场上的大部分ICE都是适用于几款或一个系列的芯片,市场中的BD12000、TRACE32等通用仿真器并不能满足需求,一些提出通用仿真器的方案却并没有提出调试模块的IPcore具体的实现方法[1-4]。使得开发人员在开发相应在线仿真器时,周期大幅增长,成本相应增加。基于此,提出一种具体实现调试模块IPcore的方法,实现通用性,缩短开发周期,减少成本。整个过程的开发选择了在Xilinx Spartan系列XC3S700AN开发板套件中进行。

1 特点及其应用

仿真器从应用性角度可分为两类:(1)特定在线仿真器。包括使用BDM、JTAG等,属某一类或者某一系列的。(2)通用型仿真器。一类是用硬件搭建程序来实现的,这种仿真器并没有很好的适用度,但可以作为基本的开发实验,另一类则是基于FPGA用IP核来实现[5-9],将要实现ICE的所有IP软核下载到FPGA中实现,这种方案虽然通用,然而受调试模块IP的限制,想要针对不同处理器进行ICE开发需要较长的周期,且没有固定的方案,可重复率较小,基于此,文中列出实现ICE调试模块IP的详细框架,并列出时钟控制块的详细逻辑,使得其重复利用率大幅提高,缩短了开发周期。

2 系统实现

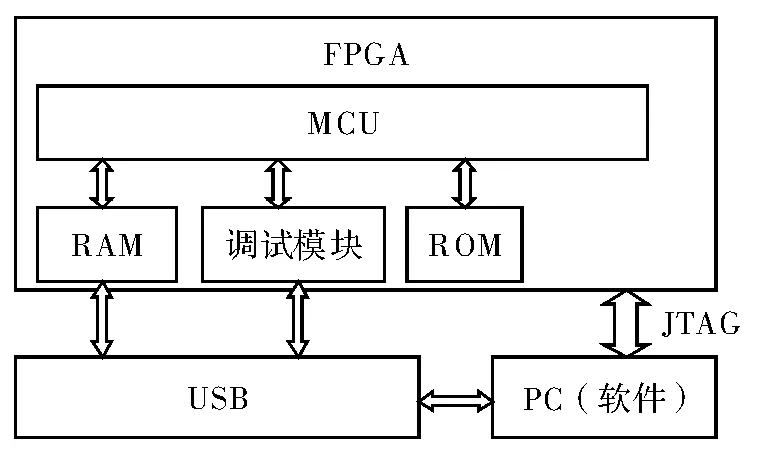

一般通用在线仿真器系统的实现可以分为:PC端软件部分,USB(Universal Serial Bus)接口部分和以FPGA为主的硬件部分,3个部分缺一不可。从实现功能上来说,以FPGA为主的硬件部分是ICE机制实现的关键[10-12]。图1为在线仿真器实现的系统图。

图1 ICE机制实现流程图

2.1 调试模块IP核的实现

PC端软件部分和USB的接口部分为在线仿真器提供了方便,而整个ICE硬件电路的实现则需要在FPGA上实现,硬件电路的质量直接决定着在线仿真器的质量,而调试模块则又是实现ICE机制的关键。

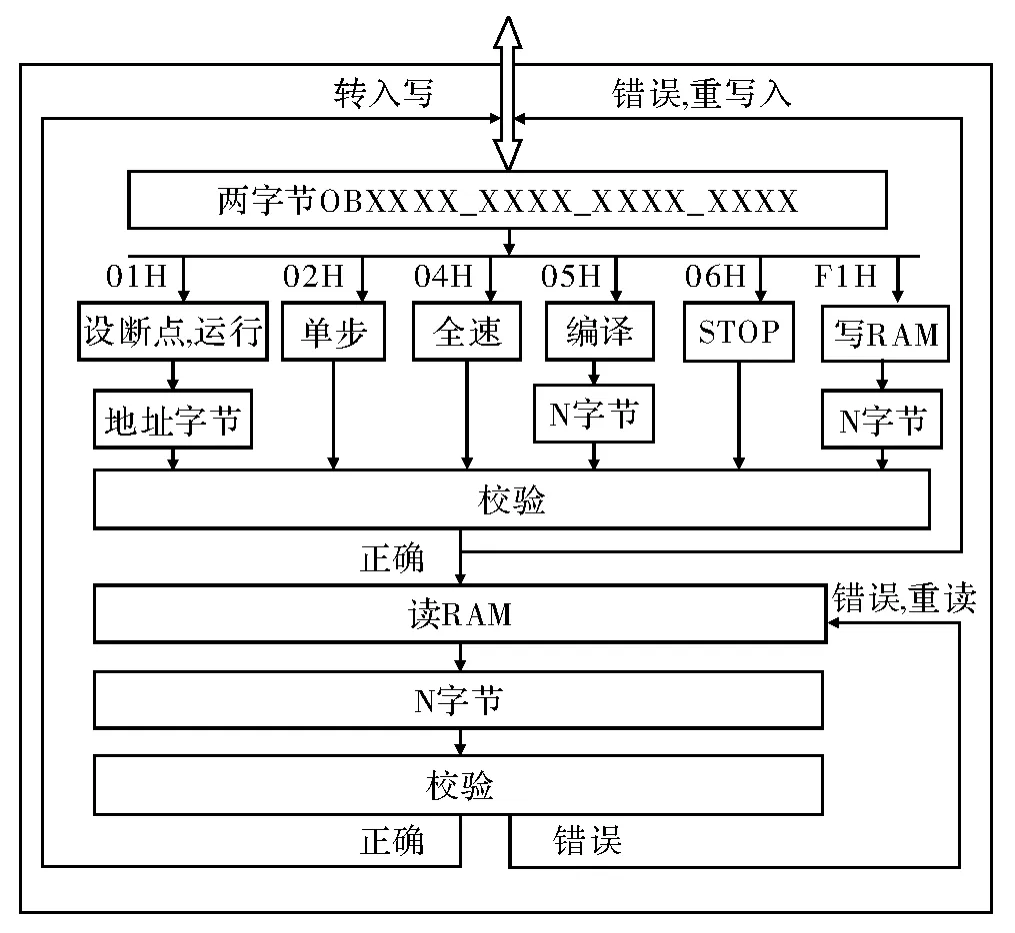

图2中双向箭头表示数据经过调试模块通过USB和电脑端进行双向通讯,电脑端发数据到FPGA视为写数据,FPGA向电脑端发数据视为读过程,整个框图表示的其实是一个读写的状态机,FPGA等待接收数据,之后按照自定义的协议将字节信息进行分类,以识别不同命令,根据命令发出相应的控制CPU运行的动作,之后对发出数据进行校验,如果正确则转入读寄存器状态,将读完的数据进行校验,正确后转入写等待即等待输入新的命令,整个状态机可以较好地实现和电脑端的交互过程。图2是实现调试模块的具体的状态图。

图2 调试模块实现状态流程图

2.2 关键逻辑设计

下面列出调试模块端口中比较重要的信号:

debug_k2,//连接mcu,总开关控制对寄存器的操作;

dclkcon,//连接mcu总的时钟控制线,1有效,有效时MCU时钟被屏蔽;

debug_wr,//连接mcu表示写寄存器命令;

debug_rd,//连接mcu表示读寄存器命令;

debug_addr_w,//地址信息用来表示要读取或写入的是哪个寄存器;

debug_k2是总的寄存器读写控制端口,当微处理器处于停止状态时,通过控制debug_k2来实现对寄存器进行读写,当其为1时,可以对微处理器内部寄存器进行读写,当进行读操作时,此时需要将debug_rd置1,当进行写操作时,将debug_rd置0之后将debug_wr置1即可,对于读哪些寄存器时需要近似于RAM地址线的debug_addr_w进行控制,定义其为9位的位宽,当其取不同值时定义其对应不同的寄存器即可。

调试模块中如何正确有效的控制CPU的运行是实现ICE机制的关键,定义其为1时CPU停止运行,为0时CPU继续运行。然而,断点运行、单步运行、全速运行3种命令之中都隐含有使微处理器运行的命令。同理,断点运行、单步运行、停止命令3种命令之中都隐含有使微处理器停止运行的命令。多个命令控制同一个时钟时,一个触发器是不可能实现的,必须对控制同一寄存器时钟的信号进行逻辑组合,进行优先级的划分,方能实现对整个时钟的控制,以下是根据情况对应不同命令定义的不同的时钟控制分量:

reg adlkcon;//停止命令的“停”控制信号,当其为1时应让CPU停止运行

reg ddlkcon;//单步命令时“停”控制信号,当其为1时应让CPU停止运行

reg edlkcon;//断点命令时“停”控制信号,当其为1时应让CPU停止运行

reg bdlkcon;//运行命令的控制信号,当其为0时CPU运行

要实现正确的时钟逻辑,则需要上述四个分量共同决定dclkcon的时序,经过分析可知,当FPGA接收到断点运行、“单步、“全速运行”命令时,必须将bdlkcon置0,从而使时钟控制信号dclkcon为0,微处理器开始运行,当运行到指定要求时断点运行、单步命令对应的时钟分量必须被置1,使时钟控制信号dclkcon置1,微处理器停止运行,并且各分量对时钟信号的控制必须满足命令循环重复的情况。

当adlkcon,ddlkcon,edlkcon为1时,微处理器需停止运行,此时时钟控制信号dclkcon必须被置1,当bdlkcon为0时微处理器需开始运行,此时时钟控制信号dclkcon必须被置0,然而,当adlkcon,ddlkcon,edlkcon由1变为0或者是bdlkcon由0变为1时,并不希望dclkcon的值发生变化,此时,时钟信号必须保持不变,也就是使其保持原值即可。

通过时序的验证,以上时序逻辑控制能够较好地满足所需要求。当出现跟运行有关的命令时,bdlkcon由1变为0,时钟信号dclkcon被置1,紧接着bdlkcon置1,时序逻辑进入到下一层进行逻辑判断,当遇到跟停止有关的命令时,adlkcon或ddlkcon或edlkcon由0变1,由于bdlkcon为1,时钟控制逻辑直接进入到下一层进行判断,整个时钟控制逻辑得以实现。

2.3 查错设计

有数据发送就难免有错误,由于USB通讯本身的优点,从电脑端发送到调试模块总线端口的数据出错的几率较小,但为了避免出错造成对字节命令的影响,在定义字节含义时,在每一条命令相关的最后一个字节都带有两字节的校验和用来检验,当发生错误时会自动重新发送,从而保证数据传输的正确性。

3 板上验证

选用EM78P447S的IP软核并结合调试模块在Xilinx Spartan系列XC3S700AN开发板套件中成功进行了验证。

一般的仿真器断点实现方法是将断点地址事先存入断点寄存器,执行时断点地址与程序地址进行比较,当相等时则CPU停止运行,然而这样在随时取消断点的同时实现起来较麻烦。如果采用软硬件结合的办法,无论设多少个断点,只在点击断点运行命令时将离当前运行位置最近的断点作为地址发送至内部FPGA,并且每次运行只发一个地址,这样就可以保证在设置了多个断点地址时,在运行了一部分后随意取消之前设置的断点,就可实现任意设置和取消断点,并且每次断点运行只发一次地址的简便实现方法。

单步的实现既可用保存地址而后进行比较的方法实现,最简单的办法则是根据处理器的芯片执行流水线特性选择关键点,此次选用的EM78P447S为两级流水线,PC变化时表示上一条指令刚执行完成,根据其特性,采样PC变化,在单步执行时每变化一次则停止一次即可实现单步功能

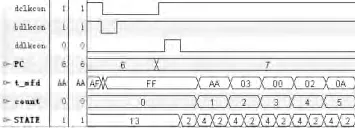

图3为单步运行逻辑分析仪采样图,单步停下的地址为007H,然后读出相应寄存器的值。t_mfd为双向数据总线,将“单步”停止后各个寄存器的值传回电脑端,如图3所示,dclkcon为总的时钟控制信号,当其为高时CPU停止运行,为低时CPU运行,bdlkcon为0时CPU运行,ddlkcon为“单步“命令时控制信号,当“单步”时,ddlkcon发出一个高电平脉冲,由上述总时钟控制逻辑可以看出,当bdlkcon低电平到来时触发dclkcon变低,CPU开始运行,当bdlkcon脉冲结束后,if(adlkcon==1edlkcon==1)并不满足所以dclkcon继续保持逻辑,等到ddlkcon变为1之后,使得dclkcon变1则CPU停止运行,PC的值增加1,CPU执行了一条指令后停止,停止后PC的值为0007H。

图3 断点停止

4 结束语

设计的硬件电路能够较好地实现“全速运行”,“停止”,“断点运行”,“单步运行”,并且读写相应的寄存器,在整个系统中,软硬件结合设计才能有效地完成在线仿真器的开发。基于此设计方法,可以广泛应用于MCU,ARM等芯片的在线仿真器开发中。本IP核具有如下优点:(1)整个程序层次分明、逻辑清晰、可重复利用、易于修改。(2)不受具体器件的限制,根据具体器件的特性稍加改动便可兼容。(3)具有良好的检验差错重发能力,避免了出错带来的错误结果。(4)适用性强,为研发人员提供了方便,大幅节约了调试的成本。(5)摆脱对某些特定种类在线仿真器的束缚,实现了仿真器的通用化。至此,结合通用仿真器方案,将调试模块的IP加入,则可在FPGA上实现具体芯片的ICE机制。

[1] 李舸,桑楠,熊光泽.一种通用在线仿真调试器的设计[J].计算机应用,2007,27(4):875-876.

[2] 曹健雄,严壮志.基于FPGA的单片机仿真器设计[J].中国医疗器械杂志,2010,34(6):424-426.

[3] 郭金怀,刘丹非,王诚.嵌入式CPU的设计与仿真[J].现代电子技术,2003,16(增刊):59-62.

[4] 王祖强,张华,李玲.8位RISC MCU IP软核仿真的新方法[J].计算机工程,2007,33(11):248-249.

[5]Xilinx Conpraion.Spartan-3A FPGA family data sheet[M].CA USA:Xilinx Conpraion,2009.

[6]Intel.Universal serial bus specification[M].CA USA:Intel Conpration,1998.

[7]Cypress.CY7C68013 EZ-USB FX2 USB microcontroller high-speed USB peripheral controller[M].CA USA:Cypress Conpration,2012.

[8] 田耕,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[9] 夏宇闻.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008.

[10]柴欣,张红梅.Visual C++程序设计基础[M].2版.北京:中国铁道出版社,2007.

[11]宋存杰.基于6502的MCU的开发及其ICE机制的实现[D].哈尔滨:哈尔滨工业大学,2010.

[12]朱武星.65C02 MCU在线仿真器的设计研究[D].厦门:厦门大学,2008.