高精度数字逻辑分析设备的研究

石 瑞

(中国电子科技集团公司第二十研究所,陕西西安 710068)

工业水平的高低是衡量一个国家综合国力的重要指标,工业设备现代化程度更是直接体现该水平的一个重要因素[1]。采集设备的多点实时并行状态采集和采集设备单点状态的采集精度的提高,对现有设备进行有效的状态分析控制和新设备研发都有积极的促进作用。

数字逻辑分析设备一般都是将采集到的模拟量(如电压、质量、状态量等)转化成电信号,通过某种模数转换进而得到数字信号,再将数字信号交给处理器进行相应的数据处理,然后通过人机界面将结果输出给使用者[2]。然而,通过分析现有的数字逻辑分析设备的技术特点,发现有一些不足或需要改进的地方。比如,有的逻辑分析设备提供商根据自身利益需求,针对各自市场划分提供相应的专门设备,无形中不但增加了使用者的生产成本,而且降低了设备的通用性;多数数字逻辑分析设备价格昂贵,形成过高的使用价格门槛;设备采集信号功能单一,设备功能灵活性有限。综合以上论述,本文在现有数字逻辑分析设备技术基础上,提出一种高精度数字逻辑分析设备的设计方法,该方法的重点有两个方面:一方面通过高精度时隙控制模块的时隙控制,实现多个低精度的状态采集模块组合完成单路高精度的状态采集并输出(理论上,在一个1GHz精度的时隙控制模块控制下,将10路1MHz采集精度的状态输入分别控制在特定的时隙中,进而获得1路10MHz的状态采集精度);另一方面是通过设置不同的输入比较门限,降低采集结果的失真度。由于逻辑分析仪的市场价格随着采集时间精度的提高而快速增长,所以该方法既可以降低高精度状态设备的设计制造成本,又可以提高普通状态设备的采集精度,获得更高的实际效益[3]。

1 逻辑分析设备原理概述

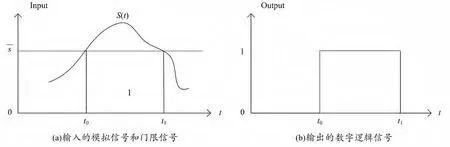

逻辑分析仪是利用时钟从测试设备上采集并显示数字信号的仪器,主要用于时序判定。逻辑分析仪不同于示波器可以显示模拟信号,它针对每一路信号输入仅设置一个唯一的门限值,用于与被测信号进行强度大小比较,故输出的是高于门限信号强度和低于门限信号强度的数字波形。采集效果如图1所示。

图1 单门限状态采集效果

2 高精度状态采集实现方案

根据上述逻辑分析设备工作原理,逻辑分析设备可以获得复杂的模拟输入信号与门限信号的强度比较关系,进而得到可以交给计算机处理的具有时间序列的数字信号,这种信号处理方法针对多路状态量并行(如多路电信号的通断检测)采集和处理比较方便,如果希望通过该状态采集的输出结果还原初始模拟信号,就需要考虑输出信号失真度过高的问题。根据状态采集的技术原理和特点,下文将详细介绍本文所研究设备的设计方案,核心技术是本文中提到的组合多路多门限状态采集,一方面提高输入采样信号的时序精度,另一方面降低输出信号的误差。

2.1 多路组合状态采集方案

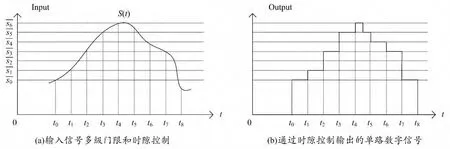

多路组合状态采集的具体技术方案,是在高精度时隙控制模块的时隙控制下,形成一个时隙序列,并控制每个单路状态采集模块工作在确定的时隙内。这种控制方式下,如果单位时间按照时隙控制模块分为N个时隙,则单位时间的组合状态采集的时间精度就相当于单路状态采集时间精度的N倍,如图2(a)中时间轴所示。然后,再按照实际需要对每个状态采集模块门限信号的大小进行设置,如图2(a)门限轴所示,形成输入信号比较强度线性增长的门限序列,并对每个门限信号按照大小进行二进制标记。当被测模拟信号按照同样的时隙划分依次输入到各个状态采集模块时,在每一个时隙里,只要判断输入信号处于哪两个相邻门限信号之间,把较小的门限信号的二进制标记作为输出信号。在设备的输出端按时隙顺序关系将每路输出结果进行组合,即可得到一个近似的按时隙的数字信号输出,如图2(b)所示。

2.2 组合状态采集核心模块构成

图2 多门限状态采集效果

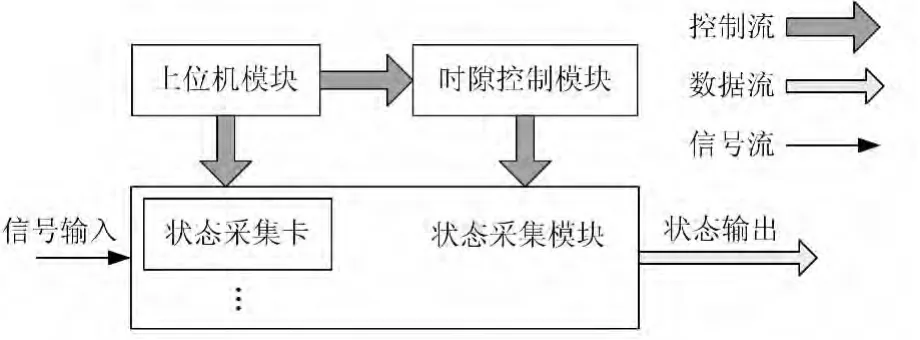

在具体硬件设计中,上述多路状态采集采用的是模块化设计方案,整个核心功能部分由信号输入模块、时隙控制模块、多路状态采集模块和输出模块构成。为了便于用户使用,在核心功能部分之外再加入上位机模块,为用户提供时隙精度控制、多个状态采集门限信号控制和状态采集结果输出的人机界面接口,功能模块的整体拓扑结构如图3所示。

图3 功能模块整体拓扑结构图

由上述设计方案和模块构成可知,该设计方案中硬件模块的功能划分清楚,可以满足通过提高时隙控制模块的时间精度进而提高组合采集精度并实现设备状态采集时间精度的需要,还可以在状态输出端得到一定近似程度的数字输出结果,便于后期的状态采集结果处理。

3 状态采集精度影响因素分析

基于逻辑状态采集的误差,在其构成的各个主要模块中都不可避免地存在,其状态采集结果的精度同样受到很多因素的影响,具体如下。

3.1 硬件电路因素

a.本文所研究的设备设计方案多处用到了微处理器、微控制器以及门限信号大小的设置,所以设备电源输入的波动将引起整个状态采集结果的波动,使得采集结果与真实结果之间产生差异。

b.该设备采用了多路并行状态采集方案,各个采集卡之间的共地干扰也将是一个影响采集结果准确性的因素。

3.2 软件设计因素

组合多点状态采集实现单路输出,这种方案的数学模型就是一种通过分段投影拟合目标曲线的方法。该方法在本文所研究的设备中是通过直接比较输入信号和门限信号强度大小,并将输入信号曲线直接投影到距离最近的门限强度信号轴上,这是一种近似曲线拟合,在算法上存在固有的误差。

4 仿真实验

基于上述多路组合状态采集实现单路高精度采集的设计方案,本文利用Labview软件进行虚拟仪器的程序开发,进而完成相关仿真实验[4-5]。

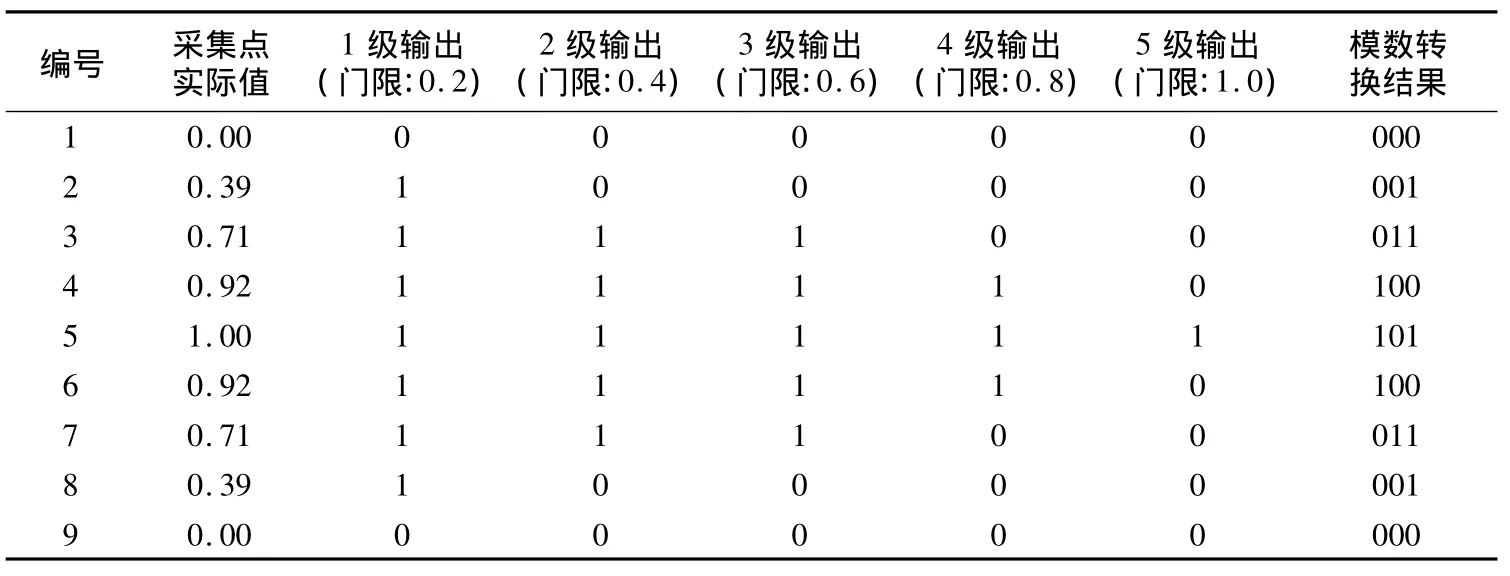

实验中,使用Labview编程,分别实现一个最大值为1的标准正弦波形模块(代表模拟待测输入信号)、一个2级和一个5级大小递增的比较门限多路状态采集模块(代表多路组合状态采集),并且将上述状态采集门限强度平均分布在0~1之间(代表时隙控制),分两次进行仿真实验,得到比较结果输出和数字输出(代表单路状态采集的波形输出和数字输出),2级门限状态采集结果见表1,5级门限状态采集结果见表2。

表1 2级状态采集结果

表2 5级状态采集结果

对比表1和表2可以看出:两次实验都获得了近似的数字输出,相对输出结果曲线图,可以得出5级门限序列组合状态采集得到的输出结果精度更高,模数转换结果也更符合目标信号强度曲线,证明文中所提的逻辑分析设备的设计方案是可行的。表2得出的输出结果与真实值之间的误差很明显,这是因为采集点数量有限,并且采集点分布平均,在这样的条件下拟合一个未知信号的强度曲线是会产生较大误差的。因此,可以通过增加采集点的方法,提高时隙控制模块的控制精度来提高状态采集的精度[6]。

5 结束语

本文提出了一种高精度逻辑分析设备的设计方案,并通过仿真实验证明了该方案的有效性和可行性,同时在实验分析过程中提出进一步提高采集精度的方法。该方案在工业生产和过程控制中有一定实际意义,对于升级现有逻辑分析仪的采集能力有一定参考价值。

[1] 周振安.数据采集系统的设计与实践[M].北京:地震出版社,2005.

[2] 张震.多功能数据采集仪的研制[D].杭州:杭州电子科技大学,2009.

[3] 魏丽娜.多通道高速数据采集卡的设计[J].自动化仪表,2002,23(2):37 -42.

[4] 侯国屏,叶齐鑫.Labview7.1编程与虚拟仪器设计[M].北京:清华大学出版社,2005.

[5] 郑福仁.Labview虚拟仪器程序设计[M].北京:人民邮电出版社,2010.

[6] 管力军.多通道高速数据采集卡的设计[J].自动化仪表,2002,23(2):33 -36.